डिजिटल इलेक्ट्रॉनिक्स और कंप्यूटर इंजीनियरिंग में, सिग्नलों के बीच समय संबंध को समझना सिस्टम विश्वसनीयता के लिए मूलभूत है। एक टाइमिंग डायग्राम इन संबंधों का वर्णन करने के लिए मुख्य दृश्य भाषा के रूप में कार्य करता है। यह सिग्नल अवस्थाओं को समय अक्ष के साथ मैप करता है, जिससे इंजीनियरों को सर्किट के भीतर डेटा प्रवाह, क्लॉक सिंक्रनाइजेशन और संभावित खतरों को देखने में सहायता मिलती है। यह मार्गदर्शिका वेवफॉर्म विश्लेषण में पाए जाने वाले संरचनात्मक तत्वों, संचालन पैटर्नों और महत्वपूर्ण परिदृश्यों का अध्ययन करती है।

क्या आप इंटीग्रेटेड सर्किट डिजाइन कर रहे हैं या एम्बेडेड सिस्टम के डीबग कर रहे हैं, सही टाइमिंग प्रतिनिधित्व को समझने और बनाने की क्षमता एक मूल क्षमता है। यह दस्तावेज सिग्नलों के बीच अंतरक्रिया, उन्हें पूरा करने के लिए आवश्यक सीमाओं और सत्यापन के दौरान सामना किए जाने वाले सामान्य त्रुटियों के तकनीकी समीक्षा प्रदान करता है।

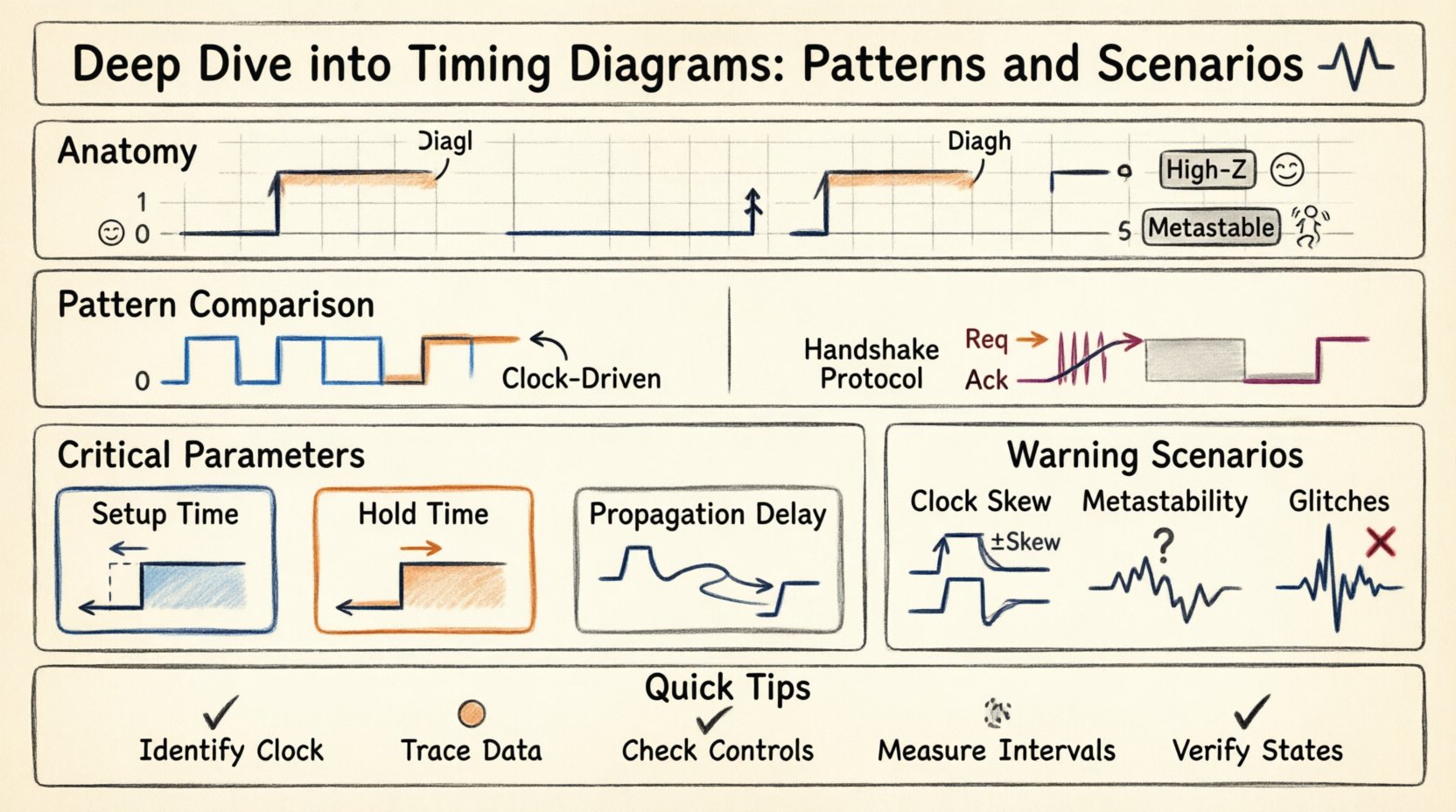

📐 टाइमिंग डायग्राम का अनातॉमी

एक टाइमिंग डायग्राम एक आलेखी प्रतिनिधित्व है जहां क्षैतिज अक्ष समय का प्रतिनिधित्व करता है, और ऊर्ध्वाधर अक्ष सिग्नल स्तरों का प्रतिनिधित्व करता है। प्रत्येक क्षैतिज रेखा डिजाइन के भीतर एक विशिष्ट सिग्नल या नेट के संबंध में होती है। घटकों को समझना सही विश्लेषण की ओर पहला कदम है।

- समय अक्ष: आमतौर पर बाएं से दाएं क्षैतिज रूप से चलता है। यह घटनाओं के पैमाने के आधार पर रेखीय या लघुगणकीय हो सकता है।

- सिग्नल लाइनें: वोल्टेज स्तरों का प्रतिनिधित्व करने वाले अलग-अलग ट्रेस। उच्च वोल्टेज आमतौर पर लॉजिक 1 को दर्शाता है, जबकि निम्न वोल्टेज लॉजिक 0 को दर्शाता है।

- संक्रमण: अवस्था में परिवर्तन को दर्शाने वाली ऊर्ध्वाधर रेखाएं, जैसे राइजिंग एज (0 से 1) या फॉलिंग एज (1 से 0)।

- लेबल: विशिष्ट सिग्नल, पिन या नियंत्रण लाइनों की पहचान करने वाले पाठ अनोटेशन।

- मार्कर्स: आमतौर पर विशिष्ट घटनाओं, जैसे क्लॉक पल्स या रीसेट ट्रिगर को दर्शाने के लिए उपयोग की जाने वाली ऊर्ध्वाधर बिंदी रेखाएं।

🔢 लॉजिक स्तर और अवस्थाएं

डिजिटल सिग्नल हमेशा 0 या 1 पर सख्ती से नहीं होते हैं। व्यावहारिक परिस्थितियों में, सिग्नल अपरिभाषित अवस्थाओं या उच्च प्रतिरोध अवस्थाओं में हो सकते हैं। एक पूर्ण डायग्राम इन भिन्नताओं को ध्यान में रखना चाहिए।

- लॉजिक हाई (1): सिग्नल को एक वोल्टेज स्तर पर ड्राइव किया जाता है जिसे लॉजिकल ट्रू के रूप में माना जाता है।

- लॉजिक लो (0): सिग्नल को एक वोल्टेज स्तर पर ड्राइव किया जाता है जिसे लॉजिकल फॉल्स के रूप में माना जाता है।

- हाई-जी: सिग्नल ड्राइवर से अलग हो जाता है, जिससे यह वास्तव में तैरता है। यह ट्राई-स्टेट बफर में सामान्य है।

- मेटास्टेबल: एक अवस्था जहां सिग्नल न तो हाई है और न ही लो, जो आमतौर पर असिंक्रोनस संक्रमण के दौरान होती है।

⚙️ सामान्य टाइमिंग पैटर्न

डिजाइन डेटा अखंडता सुनिश्चित करने के लिए पूर्वानुमानित पैटर्न का पालन करते हैं। इन पैटर्न को नियंत्रण सिग्नलों के संबंध में डेटा के चलने के तरीके को परिभाषित करते हैं। इन पैटर्न को पहचानना यह सत्यापित करने में मदद करता है कि डिजाइन अपनी विशिष्टताओं को पूरा करता है।

📌 सिंक्रोनस डेटा स्थानांतरण

सिंक्रोनस डिजाइन एक वैश्विक क्लॉक सिग्नल पर निर्भर करते हैं जो क्रियाओं को निर्देशित करता है। डेटा को केवल विशिष्ट क्षणों पर नमूना लिया जाता है, जो आमतौर पर क्लॉक के राइजिंग या फॉलिंग एज पर होता है।

- क्लॉक ड्राइवन: सभी स्थिति परिवर्तन क्लॉक के किनारे के संबंध में होते हैं।

- डेटा वैधता: डेटा क्लॉक के किनारे से पहले स्थिर होना चाहिए और उसके बाद भी स्थिर रहना चाहिए।

- प्रसारण: क्लॉक के किनारे और आउटपुट में परिवर्तन होने के बीच एक देरी होती है।

📌 असमान समय संकेतन

असमान समय संचार एक साझा क्लॉक पर निर्भर नहीं होता है। इसके बजाय, यह नियंत्रण संकेतों का उपयोग करता है जो बताते हैं कि डेटा तैयार है और जब डेटा प्राप्त कर लिया गया है।

- अनुरोध (Req): भेजने वाला संकेत देता है कि डेटा उपलब्ध है।

- स्वीकृति (Ack): प्राप्त करने वाला संकेत देता है कि डेटा स्वीकृत कर लिया गया है।

- प्रतीक्षा अवस्थाएँ: भेजने वाला रुक सकता है जब तक प्राप्त करने वाला तैयार नहीं हो जाता।

| विशेषता | समान समय पैटर्न | असमान समय पैटर्न |

|---|---|---|

| समन्वय | वैश्विक क्लॉक संकेत | नियंत्रण हैंडशेक संकेत |

| गति | आम तौर पर अधिक | चर, प्रतिक्रिया पर निर्भर |

| जटिलता | क्लॉक वितरण नेटवर्क | प्रोटोकॉल तर्क |

| लेटेंसी | पूर्वानुमानित | चर |

⏱️ महत्वपूर्ण समय सीमाएँ

दृश्य रेखाओं के बाहर, विशिष्ट संख्यात्मक सीमाएँ निर्धारित करती हैं कि क्या परिपथ सही तरीके से काम करेगा। इन पैरामीटर्स को स्थिर समय विश्लेषण के लिए महत्वपूर्ण माना जाता है और भौतिक सीमाओं के खिलाफ जांचा जाना चाहिए।

🛑 सेटअप समय

सेटअप समय वह न्यूनतम समय है जिसके दौरान डेटा सिग्नल को क्लॉक एज से पहले स्थिर रखा जाना चाहिए। यदि डेटा क्लॉक एज के बहुत निकट बदलता है, तो प्राप्त करने वाला फ्लिप-फ्लॉप सही मान को कैप्चर नहीं कर सकता है।

- मापन: सक्रिय क्लॉक एज से पीछे की ओर समय के अनुसार मापा गया है।

- खतरा: उल्लंघन सही डेटा कैप्चर करने में विफलता का कारण बनता है।

- आवश्यकता: डेटा पाथ देरी को सेटअप विंडो को पूरा करने के लिए पर्याप्त लंबा होना चाहिए।

🛑 होल्ड समय

होल्ड समय वह न्यूनतम समय है जिसके दौरान डेटा सिग्नल को क्लॉक एज के बाद स्थिर रखा जाना चाहिए। इससे यह सुनिश्चित होता है कि लैच को इनपुट मान को लॉक करने के लिए पर्याप्त समय मिले।

- मापन: सक्रिय क्लॉक एज से आगे की ओर समय के अनुसार मापा गया है।

- खतरा: उल्लंघन अस्थिरता या गलत डेटा कैप्चर करने का कारण बनता है।

- आवश्यकता: डेटा पाथ देरी को होल्ड समय विंडो को अनुमति देने के लिए पर्याप्त छोटा होना चाहिए।

⚡ प्रोपेगेशन देरी

यह वह समय है जिसमें सिग्नल लॉजिक गेट के इनपुट से आउटपुट तक यात्रा करता है। यह लोड कैपैसिटेंस और ट्रांजिस्टर के आंतरिक प्रतिरोध पर निर्भर करता है।

- tपीडी (उच्च से निम्न): 1 से 0 तक संक्रमण करने में लगने वाला समय।

- tपीडी (निम्न से उच्च): 0 से 1 तक संक्रमण करने में लगने वाला समय।

- स्क्यू: समानांतर पथों के बीच देरी में अंतर।

🚨 महत्वपूर्ण समय संदर्भ

कुछ स्थितियां महत्वपूर्ण चुनौतियां प्रस्तुत करती हैं जिनका ध्यान से विश्लेषण करने की आवश्यकता होती है। इन स्थितियों में अक्सर विभिन्न क्लॉक डोमेनों के बीच बातचीत या हार्डवेयर की भौतिक सीमाओं का बारीकी से विश्लेषण करने की आवश्यकता होती है।

🔄 क्लॉक विचलन

क्लॉक विचलन तब होता है जब क्लॉक सिग्नल विभिन्न घटकों पर अलग-अलग समय पर पहुंचता है। यह रूटिंग के अंतर या भौतिक दूरी के कारण हो सकता है।

- सकारात्मक विचलन: गंतव्य क्लॉक स्रोत क्लॉक के बाद आता है।

- नकारात्मक विचलन: गंतव्य क्लॉक स्रोत क्लॉक से पहले आता है।

- प्रभाव: सेटअप समय के अंतराल को प्रभावी रूप से कम कर सकता है या होल्ड समय के उल्लंघन को बढ़ा सकता है।

🌊 अस्थिरता

अस्थिरता एक ऐसी स्थिति है जहां फ्लिप-फ्लॉप आउटपुट न तो उच्च होता है और न ही निम्न। यह सेटअप या होल्ड समय के उल्लंघन के कारण आमतौर पर होता है, विशेष रूप से असिंक्रोनस क्रॉसिंग में।

- निराकरण: सर्किट अंततः एक स्थिर स्थिति में पहुंचता है, लेकिन इसमें लगने वाला समय अनिश्चित होता है।

- समाधान: असफलता की संभावना को कम करने के लिए सिंक्रोनाइज़र (बहु-चरण फ्लिप-फ्लॉप) का उपयोग करें।

- MTBF: असफलताओं के बीच औसत समय की गणना अस्थिरता निराकरण दरों पर आधारित होती है।

📉 ग्लिचेस

ग्लिचेस सिग्नल में छोटे शीर्ष होते हैं जिन्हें मान्य संक्रमण के रूप में गलती से समझा जा सकता है। वे आमतौर पर विभिन्न मार्गों के अलग-अलग प्रसारण देरी के कारण होते हैं।

- कारण: असमान मार्ग लंबाई या रेस की स्थिति।

- प्रभाव: निचले स्तर की तर्क में अनचाहे राज्य परिवर्तन को ट्रिगर कर सकता है।

- उपाय: फिल्टरिंग तर्क का उपयोग करें या सही समय सीमा सुनिश्चित करें।

🔍 तरंगरेखा का विश्लेषण

जब किसी समय आरेख का विश्लेषण करते हैं, तो एक व्यवस्थित दृष्टिकोण से सुनिश्चित किया जाता है कि कोई विवरण न छूटे। � ingineers को डेटा और नियंत्रण सिग्नल के प्रवाह का अनुसरण करना चाहिए ताकि अंतरों को पहचाना जा सके।

🔍 चरण-दर-चरण विश्लेषण

- क्लॉक की पहचान करें: मुख्य क्लॉक सिग्नल को स्थापित करें। यह तय करें कि यह राइजिंग-एज या फॉलिंग-एज ट्रिगर्ड है या नहीं।

- डेटा मार्गों का अनुसरण करें: स्रोत से गंतव्य तक डेटा लाइनों का पालन करें।

- नियंत्रण सिग्नल जांचें:सत्यापित करें कि एनेबल, रीसेट और क्लियर सही तरीके से निर्दिष्ट हैं।

- अंतराल मापें:सेटअप और होल्ड आवश्यकताओं की पुष्टि करने के लिए विशिष्ट घटनाओं के बीच समय की गणना करें।

- राज्य संक्रमण की पुष्टि करें:सुनिश्चित करें कि आउटपुट राज्य प्रत्याशित तार्किक कार्य के अनुरूप है।

🔍 किनारे ट्रिगर पढ़ना

सिग्नल किनारों के प्रति घटक के प्रतिक्रिया को समझना आवश्यक है।

- सकारात्मक किनारा ट्रिगर किया गया: क्रिया निम्न से उच्च में संक्रमण पर होती है।

- नकारात्मक किनारा ट्रिगर किया गया: क्रिया उच्च से निम्न में संक्रमण पर होती है।

- स्तर ट्रिगर किया गया: क्रिया तब तक होती रहती है जब तक सिग्नल एक विशिष्ट स्तर पर रहता है।

🛠️ दस्तावेज़ीकरण मानक

स्पष्ट दस्तावेज़ीकरण सुनिश्चित करता है कि डिज़ाइन अन्य � ingineers द्वारा समझे जाते हैं। नोटेशन और लेबलिंग में सामंजस्य डिबगिंग या हैंडओवर के दौरान गलत व्याख्या से बचाता है।

📝 लेबलिंग प्रथाएं

- सिग्नल नाम: स्थिर नामकरण प्रथाओं का उपयोग करें (उदाहरण के लिए,

clk,rst_n,data_in). - ध्रुवता: स्पष्ट रूप से सक्रिय-निम्न सिग्नल को चिह्नित करें, अक्सर बार या संज्ञा के साथ।

- इकाइयाँ: समय अक्ष पर समय इकाइयों (ns, µs, ms) को स्पष्ट रूप से बताएं।

- स्केलिंग: सुनिश्चित करें कि समय का पैमाना दिखाए गए घटनाओं के लिए उचित हो।

📝 दृश्य स्पष्टता

- अंतराल: जहां संभव हो, ओवरलैपिंग लाइनों से बचें।

- विपरीतता: विभिन्न सिग्नल प्रकारों के लिए अलग-अलग रंग या लाइन मोटाई का उपयोग करें।

- अनोटेशन: जटिल व्यवहार या विशिष्ट सीमाओं को समझाने वाले नोट जोड़ें।

- ग्रिड: समय अंतराल मापने में सहायता के लिए ग्रिड बैकग्राउंड का उपयोग करें।

🚧 समस्या निवारण क्रम

जब डिज़ाइन समय की आवश्यकताओं को पूरा नहीं करता है, तो एक संरचित समस्या निवारण प्रक्रिया मूल कारण को अलग करने में मदद करती है। इसमें भौतिक सीमाओं के खिलाफ आरेख का विश्लेषण करना शामिल है।

🚧 उल्लंघनों की पहचान

- सेटअप समय की जांच करें: क्या डेटा क्लॉक के संबंध में बहुत देर से आ रहा है?

- होल्ड समय की जांच करें: क्या डेटा क्लॉक के बाद बहुत जल्दी बदल रहा है?

- क्लॉक आवृत्ति की जांच करें: क्या क्लॉक अवधि आवश्यक न्यूनतम से छोटी है?

🚧 निवारण रणनीतियां

- पाइपलाइन रजिस्टर: लंबे कॉम्बिनेशनल पथों को तोड़ने के लिए अतिरिक्त रजिस्टर डालें।

- क्लॉक गेटिंग: शक्ति को कम करने और संभवतः समय सीमा में सुधार करने के लिए गतिविधि को कम करें।

- बफर स्थापना: समानांतर पथों के बीच देरी को संतुलित करने के लिए बफर जोड़ें।

- समय सीमाएं: डेटा प्रवाह को प्रभावित न करने वाली तर्क को बाहर रखने के लिए गलत पथ परिभाषित करें।

📈 डिज़ाइन के लिए सर्वोत्तम प्रथाएं

डिज़ाइन चरण के दौरान सर्वोत्तम प्रथाओं को अपनाने से विकास चक्र के बाद के चरण में समय संबंधी समस्याओं की संभावना कम हो जाती है। प्रतिक्रियात्मक ठीक करने की तुलना में सक्रिय योजना अधिक कुशल है।

- इंटरफेस मानकीकरण:डेटा स्थानांतरण के लिए ज्ञात प्रोटोकॉल का उपयोग करें ताकि समय संबंधी सत्यापन सरल हो जाए।

- असमान रास्तों को न्यूनतम करें:असमान बातचीत को न्यूनतम रखें ताकि अस्थिरता के जोखिम को कम किया जा सके।

- मान्यताओं को दस्तावेज़ीकृत करें:डिज़ाइन विवरण में घड़ी की आवृत्ति और वोल्टेज स्तर को स्पष्ट रूप से बताएं।

- नियमित रूप से समीक्षा करें:परियोजना के हर महत्वपूर्ण चरण पर समय संबंधी समीक्षा करें।

🎯 मुख्य अवधारणाओं का सारांश

समय आरेख डिजिटल प्रणालियों के समय संबंधी व्यवहार को दृश्यमान करने के लिए आवश्यक उपकरण हैं। वे डेटा और नियंत्रण संकेतों के समय के साथ बातचीत कैसे होती है, इसका खुलासा करते हैं, जिसमें सेटअप और होल्ड समय जैसी महत्वपूर्ण सीमाएं शामिल हैं। इन आरेखों के रचना को समझकर इंजीनियर पैटर्न की पहचान कर सकते हैं, त्रुटियों का अनुमान लगा सकते हैं, और विश्वसनीय प्रणाली प्रदर्शन सुनिश्चित कर सकते हैं।

मुख्य बातें में सिंक्रोनस और असिंक्रोनस पैटर्न के बीच अंतर, घड़ी विचलन प्रबंधन के महत्व और स्पष्ट दस्तावेज़ीकरण मानकों की आवश्यकता शामिल हैं। इन सिद्धांतों का पालन करने से विश्वसनीय डिज़ाइन करना आसान हो जाता है और सत्यापन प्रक्रिया सरल हो जाती है।

तरंग आकृति डेटा का निरंतर विश्लेषण सुनिश्चित करता है कि डिज़ाइन संचालन सीमाओं के भीतर रहें। तकनीक विकसित होने और घड़ी की गति बढ़ने के साथ, समय विश्लेषण में आवश्यक निपुणता और अधिक महत्वपूर्ण हो जाती है। इन अवधारणाओं को समझने से स्थिर, उच्च प्रदर्शन वाली डिजिटल संरचनाओं के निर्माण की अनुमति मिलती है।