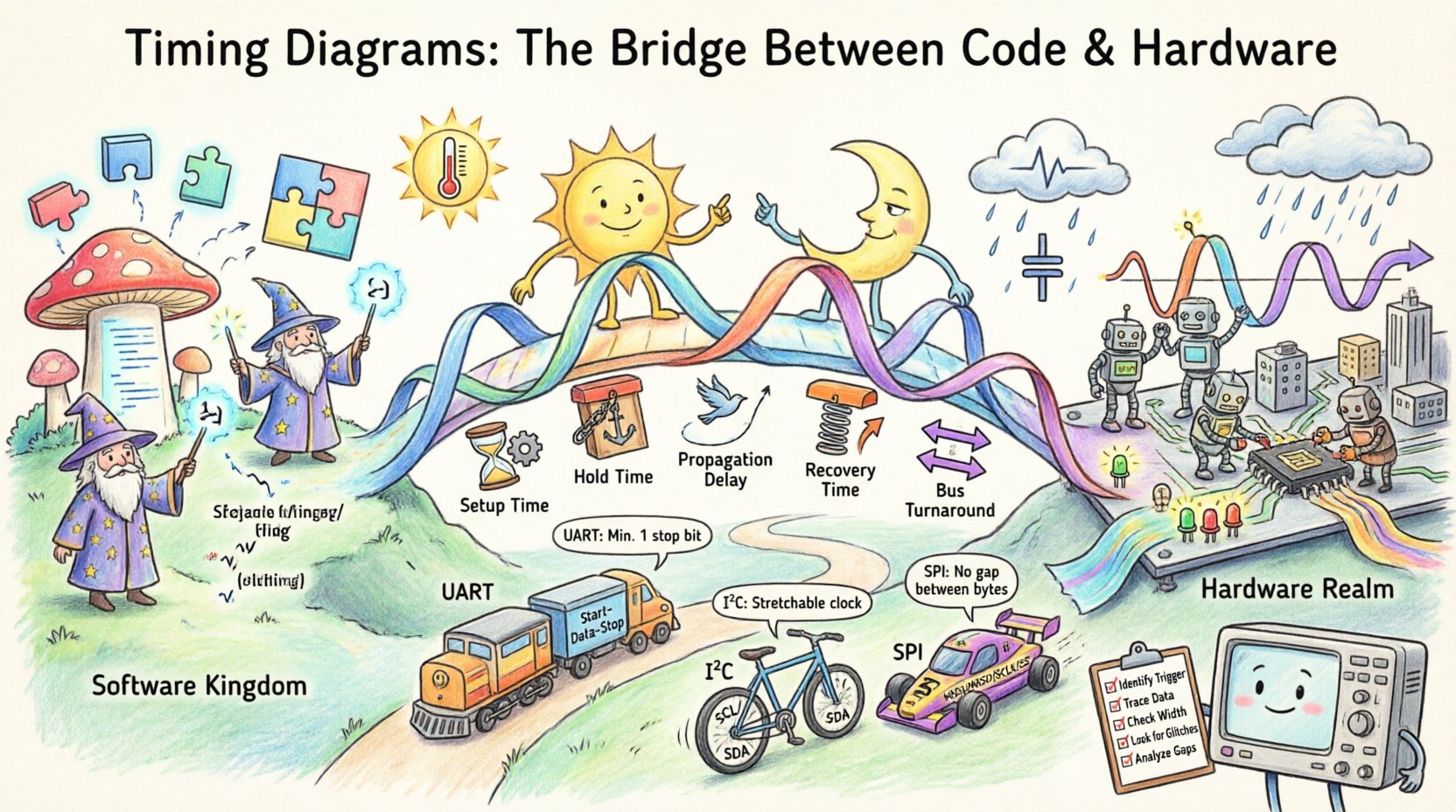

जब सॉफ्टवेयर इंजीनियर कोड लिखते हैं, तो वे निर्देशों, चरों और तर्क प्रवाह में सोचते हैं। जब हार्डवेयर इंजीनियर परिपथ डिज़ाइन करते हैं, तो वे वोल्टेज स्तरों, प्रसारण देरी और क्लॉक चक्करों में सोचते हैं। इन दोनों दुनियाओं के बीच अक्सर तनाव की स्थिति होती है। कोड एक विशिष्ट तार्किक क्षण पर सिग्नल के आने की अपेक्षा करता है, लेकिन हार्डवेयर भौतिक समय पर काम करता है, जो शोर, तापमान और विद्युत प्रतिरोध के प्रभाव में होता है। इन दोनों क्षेत्रों के बीच सेतु टाइमिंग डायग्राम है।

एक टाइमिंग डायग्राम सिर्फ एक चित्र नहीं है; यह एक संविदा है। यह समय में घटनाओं के बीच सटीक संबंध को परिभाषित करता है। यह फर्मवेयर को बताता है कि किस समय पिन को पढ़ना सुरक्षित है और सिलिकॉन को बताता है कि किस समय लाइन को ड्राइव करना सुरक्षित है। इन आरेखों की स्पष्ट समझ के बिना, एम्बेडेड सिस्टम अप्रत्याशित रूप से विफल हो जाते हैं। डेटा क्षति, रेस कंडीशन और सिस्टम हैंग आम समस्याएं बन जाती हैं। यह मार्गदर्शिका टाइमिंग आरेखों के यांत्रिकी, उनके पीछे के भौतिकी और उन्हें पढ़ने और बनाने के प्रभावी तरीकों का अध्ययन करती है।

📊 सिग्नल का अनातमी

इसके केंद्र में, डिजिटल तर्क द्विआधारी अवस्थाओं पर निर्भर होता है। हालांकि भौतिक दुनिया में, इन अवस्थाओं को वोल्टेज स्तरों द्वारा दर्शाया जाता है। एक “उच्च” 3.3 वोल्ट हो सकता है, और एक “निम्न” 0 वोल्ट हो सकता है। लेकिन सिग्नल तुरंत बदलते नहीं हैं। वे एक सीमित अवधि में बढ़ते और गिरते हैं। एक टाइमिंग आरेख इस संक्रमण को दर्शाता है।

इन आरेखों की दृश्य भाषा को समझना महारत प्राप्त करने का पहला कदम है। मुख्य तत्वों में शामिल हैं:

- समय अक्ष:आमतौर पर क्षैतिज होता है, बाएं से दाएं जाता है। यह रैखिक या लघुगणकीय हो सकता है, हालांकि अधिकांश लॉजिक विश्लेषण के लिए रैखिक मानक है।

- सिग्नल लाइनें:विशिष्ट तारों, पिनों या आंतरिक नोड्स का प्रतिनिधित्व करने वाली ऊर्ध्वाधर रेखाएं।

- संक्रमण: निम्न से उच्च (राइजिंग एज) या उच्च से निम्न (फॉलिंग एज) की ओर गति। इन एजेस अक्सर क्रमिक तर्क में अवस्था परिवर्तन को ट्रिगर करते हैं।

- स्तर: संक्रमण के पहले या बाद में सिग्नल की स्थिर अवस्था।

- लेबल: विशिष्ट पल्स या अंतराल के अर्थ को स्पष्ट करने वाले पाठ अनोटेशन।

एक सरल क्लॉक सिग्नल को ध्यान में रखें। यह उच्च और निम्न के बीच दोलन करता है। एक पूर्ण चक्कर पूरा करने में लगने वाला समय आवर्तकाल है। आवर्तकाल का व्युत्क्रम आवृत्ति है। एक टाइमिंग आरेख में, क्लॉक सिस्टम की धड़कन के रूप में कार्य करता है। अन्य सभी सिग्नल अक्सर इन एजेस के साथ समकालीन होते हैं।

🕰️ क्लॉक डोमेन

अधिकांश डिजिटल सिस्टम एक क्लॉक डोमेन के भीतर काम करते हैं। यह एक समूह है जिसमें सर्किट्स एक ही समय संदर्भ साझा करते हैं। हालांकि, सिग्नल अक्सर अलग-अलग डोमेनों के बीच पार करते हैं। इससे जटिलता आती है। एक तेज़ डोमेन में उत्पन्न सिग्नल एक धीमे डोमेन के लिए बहुत देर से आ सकता है या बहुत जल्दी, जिससे होल्ड उल्लंघन हो सकता है।

जब समय विश्लेषण कर रहे हों, तो आपको निम्न पर विचार करना होगा:

- क्लॉक स्क्यू: विभिन्न घटकों पर क्लॉक सिग्नल के आगमन समय का अंतर। यदि क्लॉक प्रेषक से पहले प्राप्त होता है, तो समय सीमा संकुचित हो जाती है।

- फेज शिफ्ट: कुछ प्रणालियों में, सिग्नल क्लॉक एज के साथ संरेखित नहीं होते हैं, बल्कि चक्कर के बीच में आते हैं।

- जिटर: सिग्नल के समय में भिन्नता। जिटर यादृच्छिक या निर्धारक हो सकता है। यह शोर मार्जिन को कम करता है और आरेख को कम भविष्यवाणी योग्य बनाता है।

हार्डवेयर के साथ इंटरफेस करने के लिए लिखा गया कोड एक स्थिर क्लॉक के अस्तित्व को मानता है। यदि भौतिक क्लॉक तापमान या वोल्टेज उतार-चढ़ाव के कारण विचलित हो जाता है, तो टाइमिंग आरेख वास्तविकता के अनुरूप नहीं रहता है। इसी कारण टाइमिंग आरेखों में टॉलरेंस बैंड या सबसे खराब स्थितियों को शामिल करना आवश्यक है।

⚙️ महत्वपूर्ण समय संबंधी पैरामीटर

विशिष्ट पैरामीटर सिग्नल अखंडता की सीमा को परिभाषित करते हैं। इन मानों को अक्सर डेटाशीट में पाया जाता है, लेकिन टाइमिंग आरेख के संदर्भ में समझना बेहतर होता है। निम्नलिखित तालिका इंजीनियरों द्वारा मूल्यांकन करने के लिए सबसे महत्वपूर्ण पैरामीटरों का वर्णन करती है।

| पैरामीटर | परिभाषा | प्रणाली पर प्रभाव |

|---|---|---|

| सेटअप समय | डेटा के स्थिर रहने के लिए न्यूनतम समयपहले क्लॉक किनारे के बाद। | यदि उल्लंघन किया जाता है, तो प्राप्त करने वाला फ्लिप-फ्लॉप सही मान को कैप्चर नहीं कर सकता है। |

| होल्ड समय | डेटा के स्थिर रहने के लिए न्यूनतम समयके बाद क्लॉक किनारे के बाद। | यदि उल्लंघन किया जाता है, तो फ्लिप-फ्लॉप एक अस्थिर अवस्था में प्रवेश कर सकता है। |

| प्रसारण देरी | सिग्नल के इनपुट से आउटपुट तक यात्रा करने में लगने वाला समय। | देरी लॉजिक गेट्स के माध्यम से जमा होती है, जिससे क्लॉक साइकिल्स छूट सकती हैं। |

| पुनर्स्थापना समय | एक असिंक्रोनस घटना के बाद नियंत्रण सिग्नल के सामान्य स्थिति में लौटने के लिए आवश्यक समय। | रीसेट या इंटरप्ट्स के बाद प्रणाली कितनी तेजी से पुनर्स्थापित होती है, इस पर प्रभाव डालता है। |

| बस टर्नअराउंड समय | बस के आउटपुट मोड से इनपुट मोड में स्विच करने के लिए आवश्यक समय। | I2C या 1-वायर जैसे द्विदिशात्मक बस के लिए महत्वपूर्ण। |

इन पैरामीटर्स के उल्लंघन के कारण हमेशा तुरंत क्रैश नहीं होता है। कभी-कभी प्रणाली 99% समय काम करती है और केवल विशिष्ट स्थितियों में विफल होती है। इसी कारण समय संबंधी विश्लेषण एक आवर्ती प्रक्रिया है। आपको यह सत्यापित करना होगा कि आरेख दुर्भाग्यपूर्ण वोल्टेज और तापमान की स्थितियों में भी सही रहता है।

👀 तरंग आकृति को पढ़ना

समय आरेख को पढ़ने के लिए एक व्यवस्थित दृष्टिकोण की आवश्यकता होती है। हार्डवेयर समस्या के निराकरण के समय, सिग्नल स्तरों को देखने के अलावा कुछ और भी देखें। सिग्नलों के बीच के संबंधों पर ध्यान दें।

एक तरंग आकृति के विश्लेषण के लिए निम्नलिखित चरणों का पालन करें:

- ट्रिगर की पहचान करें: उस घटना की पहचान करें जो अनुक्रम की शुरुआत करती है। यह आमतौर पर क्लॉक किनारा या बाहरी इंटरप्ट होता है।

- डेटा का अनुसरण करें: ट्रिगर के संबंध में डेटा लाइनों का अनुसरण करें। क्या डेटा क्लॉक किनारे से पहले या बाद में दिखाई देता है?

- चौड़ाई की जांच करें पल्स की अवधि का मापन करें। क्या एक “हाई” सिग्नल प्राप्त करने वाले लॉजिक द्वारा पहचाने जाने के लिए पर्याप्त लंबा है?

- ग्लिचेस की तलाश करें: स्थिर अवस्थाओं के बीच होने वाले अनावश्यक पल्स। इनके कारण क्रॉसटॉल या लॉजिक हाजर्ड हो सकते हैं।

- अंतराल का विश्लेषण करें: एक लेनदेन के अंत और अगले के शुरू होने के बीच के समय को देखें। क्या हार्डवेयर के रीसेट होने के लिए पर्याप्त समय है?

अक्सर, समस्या अंतराल में होती है। यदि एक माइक्रोकंट्रोलर एक पेरिफेरल में डेटा लिखने के बाद, अगला बाइट भेजने से पहले एक विशिष्ट देरी की आवश्यकता हो सकती है। यदि आरेख इन बाइट्स को बिना किसी अंतराल के एक के बाद एक दिखाता है, तो कोड हार्डवेयर के लिए अत्यधिक उत्साही होने की संभावना है।

🔌 सामान्य प्रोटोकॉल और समय निर्धारण

विभिन्न संचार प्रोटोकॉल विभिन्न समय सीमाओं को लागू करते हैं। विश्वसनीय रूप से संचार करने वाले फर्मवेयर को लिखने के लिए इन सीमाओं को समझना आवश्यक है।

| प्रोटोकॉल | मुख्य समय विशेषता | सामान्य विफलता का रूप |

|---|---|---|

| यूएआरटी | स्टार्ट बिट के बाद डेटा बिट्स और स्टॉप बिट। बॉड दर पर निर्भर। | प्रेषक और प्राप्तकर्ता के बीच क्लॉक ड्रिफ्ट के कारण बिट त्रुटियाँ। |

| आई2सी | एससीएल और एसडीए लाइनें। पुल-अप प्रतिरोधकों की आवश्यकता होती है। एसडीए को एससीएल हाई के दौरान स्थिर रहना चाहिए। | बस होल्ड-अप या क्लॉक स्ट्रेचिंग समस्याएं जो टाइमआउट का कारण बनती हैं। |

| एसपीआई | क्लॉक और डेटा लाइनें अलग-अलग होती हैं। किनारे द्वारा ट्रिगर्ड (सीपीओएल/सीपीएचए सेटिंग्स)। | स्लेव्स मास्टर क्लॉक गति के लिए बहुत धीमी प्रतिक्रिया देते हैं। |

| जीपीआईओ इंटरप्ट | किनारे संवेदनशीलता। आईएसआर में न्यूनतम प्रोसेसिंग समय की आवश्यकता होती है। | पिछली सेवा रूटीन के लंबे निष्पादन के कारण इंटरप्ट छूट जाते हैं। |

उदाहरण के लिए, एसपीआई में, क्लॉक किनारे के समय को डेटा लाइन के संबंध में निर्धारित करता है कि डेटा राइजिंग या फॉलिंग एज पर लैच किया जाता है या नहीं। यदि फर्मवेयर एक मोड को मानता है और हार्डवेयर दूसरे मोड के लिए कॉन्फ़िगर किया गया है, तो डेटा गलत तरीके से पढ़ा जाएगा। एक समय आरेख इस संबंध को दृश्य रूप से स्पष्ट करता है, जिससे कॉन्फ़िगरेशन त्रुटियों से बचा जा सकता है।

🔍 समय संबंधी समस्याओं का निराकरण

जब कोई प्रणाली अनियमित व्यवहार करती है, तो पहला उपकरण जिसे प्राप्त करना चाहिए वह डिबगर नहीं है, बल्कि समय आरेख है। समय के साथ डिबगिंग में वास्तविक विद्युत व्यवहार को कैप्चर करना और उसकी अपेक्षित डिजाइन के साथ तुलना करना शामिल है।

सामान्य समय संबंधी समस्याओं में शामिल हैं:

- मेटास्टेबिलिटी: जब कोई सिग्नल क्लॉक एज के बहुत निकट फ्लिप-फ्लॉप पर पहुंचता है, तो आउटपुट अनिश्चित हो जाता है। यह हाई, लो या अनिश्चित समय तक एक मध्यवर्ती अवस्था में रह सकता है।

- रेस कंडीशन्स: जब परिणाम घटनाओं के सापेक्ष समय पर निर्भर करता है। यदि दो सिग्नल एक साथ बदलते हैं, तो प्रोसेसिंग का क्रम महत्वपूर्ण होता है।

- सिग्नल अखंडता:लंबे ट्रेस पर प्रतिबिंब और रिंगिंग के कारण गलत संक्रमण हो सकते हैं। आरेख में एक साफ स्क्वायर वेव के स्थान पर दोलन दिखाई दे सकते हैं।

- सेटअप/होल्ड उल्लंघन: डेटा क्लॉक एज के बहुत निकट बदल जाता है। इसका कारण अक्सर लॉजिक पथ के लिए क्लॉक गति बहुत अधिक होना होता है।

इन समस्याओं को दूर करने के लिए आपको कोड में देरी जोड़ने, क्लॉक आवृत्ति बदलने या हार्डवेयर लेआउट को समायोजित करने की आवश्यकता हो सकती है। समय आरेख इन परिवर्तनों को आत्मविश्वास के साथ करने के लिए आवश्यक साक्ष्य प्रदान करता है।

📝 दस्तावेजीकरण के लिए सर्वोत्तम प्रथाएं

दस्तावेजीकरण के लिए समय आरेख बनाना उन्हें पढ़ने जितना ही महत्वपूर्ण है। खराब दस्तावेजीकृत समय के कारण रखरखाव की समस्याएं होती हैं। भविष्य के इंजीनियरों को समझने में कठिनाई होगी कि कोड में विशिष्ट देरी क्यों जोड़ी गई थी।

अपने आरेख बनाते समय इन दिशानिर्देशों का पालन करें:

- मानक प्रतीकों का उपयोग करें: लेजेंड में परिभाषित न हों तो कस्टम आइकन का उपयोग न करें। मानक राइजिंग/फॉलिंग एज नोटेशन का उपयोग करें।

- सब कुछ लेबल करें: यह न मानें कि पाठक हर लाइन का अर्थ जानता है। पिन, सिग्नल और स्थितियों को स्पष्ट रूप से लेबल करें।

- संदर्भ शामिल करें: डेटा लाइनों के साथ कंट्रोल सिग्नलों (जैसे चिप सेलेक्ट या एनेबल) की स्थिति दिखाएं।

- इकाइयां निर्दिष्ट करें: हमेशा समय स्केल निर्दिष्ट करें। क्या यह माइक्रोसेकंड, नैनोसेकंड या क्लॉक साइकिल है?

- महत्वपूर्ण पथों को उजागर करें: सिस्टम स्थिरता निर्धारित करने वाले सिग्नलों को जोर देने के लिए मोटी लाइनें या अलग रंगों का उपयोग करें।

- संस्करण नियंत्रण: जब हार्डवेयर या फर्मवेयर में परिवर्तन होता है, तो आरेख को अपडेट करें। अप्रचलित आरेख एक जोखिम है।

दस्तावेजीकरण केवल “खुशहाल मार्ग” को दिखाने के लिए नहीं होना चाहिए। यह त्रुटि स्थितियों को भी दिखाना चाहिए। जब टाइमआउट होता है तो आरेख कैसा दिखता है? जब रीसेट ट्रिगर किया जाता है तो आरेख कैसा दिखता है? ये परिदृश्य अक्सर सबसे अधिक बग छिपे रहते हैं।

🌡️ पर्यावरणीय कारक

एक समय आरेख अक्सर आदर्श प्रयोगशाला स्थितियों के तहत बनाया जाता है। वास्तविक दुनिया के पर्यावरण अक्सर आदर्श नहीं होते हैं। तापमान, वोल्टेज और विद्युत चुंबकीय हस्तक्षेप सभी सिग्नल प्रसारण को प्रभावित करते हैं।

निम्नलिखित कारकों पर विचार करें:

- तापमान: उच्च तापमान पर सिलिकॉन प्रदर्शन घटता है। प्रसारण देरी बढ़ती है। 25°C पर काम करने वाला सिस्टम 85°C पर विफल हो सकता है।

- वोल्टेज: कम आपूर्ति वोल्टेज देरी बढ़ाता है। उच्च वोल्टेज देरी को कम कर सकता है लेकिन शक्ति उपभोग और गर्मी बढ़ाता है।

- लोड कैपैसिटेंस: लंबे तारों में धारिता जोड़ते हैं। इससे सिग्नल के उठने और गिरने के समय धीमे हो जाते हैं, जिससे संकेत की चौड़ाई बढ़ जाती है लेकिन संक्रमण धीमा हो जाता है।

मजबूत डिजाइन इन भिन्नताओं को ध्यान में रखता है। उत्पादन के लिए समय आरेख बनाते समय “सबसे खराब संभावित” कोने को ध्यान में रखें। इसका मतलब है कि आरेख सबसे धीमे संकेत संक्रमण और सबसे तेज क्लॉक किनारों का प्रतिनिधित्व करता है। यदि प्रणाली इन शर्तों के तहत काम करती है, तो यह अधिकांश स्थितियों में काम करेगी।

🛠️ आरेख बनाना और मान्यता देना

जबकि हाथ से बनाना संभव है, आधुनिक � ingineering समय को कैप्चर और मान्यता देने के लिए स्वचालित उपकरणों पर निर्भर करता है। हालांकि, उपकरण के उपयोग के बावजूद सिद्धांत वही रहते हैं। लक्ष्य समय के प्रवाह को दृश्यमान करना है।

जब किसी आरेख की मान्यता करते हैं:

- डेटासीट्स के बीच तुलना करें: सुनिश्चित करें कि आपके आरेख में समय संबंधी मान उपयोग किए गए चिप्स के निर्माता की विशिष्टताओं के अनुरूप हैं।

- सिमुलेशन चलाएं: भौतिक परिपथ बनाने से पहले तर्क को मॉडल करने के लिए सिमुलेशन वातावरण का उपयोग करें।

- वास्तविक हार्डवेयर को मापें: कोई भी वास्तविक माप के बदले नहीं हो सकता। भौतिक बोर्ड से तरंगरूप प्राप्त करें और उन्हें डिजाइन आरेख पर ओवरले करें।

- मार्जिन जांचें: क्या सिग्नलों के बीच पर्याप्त आराम का समय है? यदि मार्जिन शून्य है, तो कोई भी भिन्नता विफलता का कारण बनेगी।

मान्यता एक निरंतर प्रक्रिया है। जैसे-जैसे फर्मवेयर विकसित होता है, समय संबंधी आवश्यकताएं बदल सकती हैं। एक नया इंटरप्ट हैंडलर एक देरी ला सकता है जो किसी सिग्नल को उसकी समय सीमा के बाहर धकेल दे। निरंतर सत्यापन सुनिश्चित करता है कि कोड और हार्डवेयर के बीच का सेतु ठोस बना रहे।

🔗 तर्क और भौतिकी का प्रतिच्छेदन

अंततः, एक समय आरेख तर्क और भौतिकी के प्रतिच्छेदन का प्रतिनिधित्व करता है। तर्क यह निर्धारित करता है कि क्या होना चाहिए; भौतिकी यह निर्धारित करती है कि वास्तव में क्या होता है। इंजीनियर का काम इन दोनों वास्तविकताओं को मिलाना है।

इन आरेखों के व्याख्या और निर्माण को समझने के बाद, आप जटिल विफलताओं का निदान करने की क्षमता प्राप्त करते हैं जो दूसरे लोग छोड़ सकते हैं। आप यह अनुमान लगाना बंद कर देते हैं कि प्रणाली क्यों फंसती है और ठीक वहां देखने लगते हैं जहां समय सीमा का उल्लंघन हुआ था। इस स्तर की समझ एक विकासकर्ता को एक डिजाइनर में बदल देती है।

चाहे आप एक सरल सेंसर इंटरफेस या एक उच्च गति संचार बस का डिजाइन कर रहे हों, समय आरेख आपका प्राथमिक संदर्भ है। यह सुनिश्चित करता है कि आपके द्वारा लिखा गया कोड हार्डवेयर द्वारा अपेक्षित समय में निष्पादित होता है। यह सुनिश्चित करता है कि आप स्क्रीन पर देख रहे सिग्नल पिन पर वोल्टेज के अनुरूप हैं। यह समन्वय की भाषा है।

इन आरेखों को समझने में समय निवेश करें। उन्हें कोड के समान गंभीरता से लें। एम्बेडेड प्रणालियों में, समय केवल एक विवरण नहीं है; यह विश्वसनीयता की नींव है। जब कोड और हार्डवेयर समय की एक ही भाषा बोलते हैं, तो प्रणाली सटीकता और स्थिरता के साथ काम करती है।