डिजिटल हार्डवेयर डिजाइन के जटिल लैंडस्केप में, स्पष्टता महत्वपूर्ण है। इंजीनियर और डिजाइनर समय के साथ सिग्नलों के व्यवहार को समझाने के लिए दृश्य प्रतिनिधित्व पर निर्भर करते हैं। समय आरेख इस उद्देश्य के लिए सबसे महत्वपूर्ण उपकरणों में से एक है। यह संक्षिप्त तर्क को एक दृश्य समय रेखा में बदलता है, जो विभिन्न घटकों के माध्यम से उच्च और निम्न स्तरों के नृत्य को उजागर करता है। हालांकि, जैसे-जैसे प्रणालियाँ जटिलता में बढ़ती हैं, इन आरेखों को भारी लगने लगते हैं। यह मार्गदर्शिका एक मॉड्यूलर रणनीति का अध्ययन करती है जिससे समय आरेखों को प्रभावी ढंग से विश्लेषित और विश्लेषित किया जा सके, जिससे हार्डवेयर सत्यापन में सटीकता और विश्वसनीयता सुनिश्चित होती है।

कार्यात्मक विफलताओं को रोकने के लिए डेटा और नियंत्रण सिग्नलों के प्रवाह को समझना आवश्यक है। चाहे आप माइक्रोकंट्रोलर इंटरफेस या उच्च गति संचार प्रोटोकॉल का डिजाइन कर रहे हों, इन आरेखों को पढ़ने और बनाने की क्षमता एक मजबूत डिजाइन को एक नाजुक डिजाइन से अलग करती है। एक संरचित, मॉड्यूलर दृष्टिकोण अपनाकर टीमें जटिलता का प्रबंधन कर सकती हैं और समय सीमा उल्लंघन के जोखिम को कम कर सकती हैं।

समय आरेखों के बुनियादी बातों को समझना ⏱️

एक समय आरेख समय के साथ सिग्नलों के राज्य में परिवर्तन का एक आलेखीय प्रतिनिधित्व है। इसमें समय को क्षैतिज अक्ष पर और सिग्नल राज्य को ऊर्ध्वाधर अक्ष पर दर्शाया जाता है। इस दृश्य रूप में इंजीनियरों को डिजिटल सर्किट के भीतर विभिन्न सिग्नलों के बीच संबंध की पुष्टि करने में मदद मिलती है। मुख्य उद्देश्य यह सुनिश्चित करना है कि डेटा तब स्थिर और वैध हो जब इसे प्राप्त करने वाले घटक द्वारा नमूना लिया जाता है।

कई महत्वपूर्ण तत्व किसी भी समय आरेख की नींव बनाते हैं:

- सिग्नल लाइनें:क्षैतिज रेखाएं विशिष्ट सिग्नल जैसे क्लॉक, डेटा या नियंत्रण ले जाने वाले अलग-अलग तारों या बस का प्रतिनिधित्व करती हैं।

- समय अक्ष:क्षैतिज प्रगति समय के बीतने को दर्शाती है, जो नैनोसेकंड या क्लॉक चक्कर में अक्सर चिह्नित की जाती है।

- तार्किक स्तर:सिग्नल आमतौर पर द्विआधारी होते हैं, जिन्हें उच्च (1) या निम्न (0) के रूप में दर्शाया जाता है। कभी-कभी अपरिभाषित अवस्थाओं या उच्च प्रतिरोध अवस्थाओं को भी दिखाया जाता है।

- संक्रमण:ऊर्ध्वाधर रेखाएं उस क्षण को दर्शाती हैं जब कोई सिग्नल एक अवस्था से दूसरी अवस्था में स्विच करता है, जैसे उत्थान या अवपतन किनारे।

- अनोतेशन:पाठ लेबल आमतौर पर आरेख के भीतर विशिष्ट सीमाएं, देरी या कार्यात्मक ब्लॉक को परिभाषित करते हैं।

इन बुनियादी बातों के स्पष्ट ज्ञान के बिना, जटिल बातचीत को समझना मुश्किल हो जाता है। एक समय आरेख सिर्फ एक ड्राइंग नहीं है; यह प्रेषक और प्राप्तकर्ता के बीच एक संविदा है। यह निर्धारित करता है कि डेटा को किन नियमों के तहत यात्रा करनी चाहिए ताकि सही ढंग से प्रसंस्कृत किया जा सके।

जटिल डिजाइन के लिए मॉड्यूलर रणनीति 🧩

आधुनिक डिजिटल प्रणालियाँ अक्सर सरल नहीं होती हैं। इनमें बहुत से उप-प्रणालियाँ होती हैं, जिनमें प्रत्येक की अपनी समय सीमा की आवश्यकता होती है। एक ही आरेख में पूरी प्रणाली को बनाने की कोशिश करने से अक्सर भारी और भ्रम की स्थिति बनती है। एक मॉड्यूलर दृष्टिकोण डिजाइन को प्रबंधन योग्य टुकड़ों में बांटता है। इस विधि से पठनीयता में सुधार होता है और डिबगिंग प्रक्रिया सरल हो जाती है।

मॉड्यूलरता क्यों महत्वपूर्ण है

एक प्रणाली को मॉड्यूल में बांटने से डिजाइनरों को पूरी वास्तुकला के शोर में खो जाने के बिना विशिष्ट इंटरफेस पर ध्यान केंद्रित करने की अनुमति मिलती है। जब समय उल्लंघन होता है, तो मॉड्यूलर आरेख समस्या के स्रोत को आसानी से अलग करने में मदद करता है। यह संज्ञानात्मक भार को कम करता है और अलग-अलग ब्लॉक पर काम कर रही विभिन्न इंजीनियरिंग टीमों के बीच सहयोग को सुगम बनाता है।

इस दृष्टिकोण के लाभ इस प्रकार हैं:

- समस्याओं का अलगाव:समस्याओं को पूरी प्रणाली के बजाय एक विशिष्ट ब्लॉक के भीतर पहचाना जा सकता है।

- पुनर्उपयोगिता:सामान्य मॉड्यूल के लिए मानकीकृत समय पैटर्न को अलग-अलग प्रोजेक्ट में पुनर्उपयोग किया जा सकता है।

- स्केलेबिलिटी:नए फीचर्स को पूरे आरेख को फिर से बनाए बिना नए मॉड्यूल के रूप में जोड़ा जा सकता है।

- टीम की कार्यक्षमता:अलग-अलग टीमें अपने-अपने समय आरेखों पर एक साथ काम कर सकती हैं।

मॉड्यूल सीमाओं को परिभाषित करना

इस रणनीति को प्रभावी ढंग से लागू करने के लिए स्पष्ट सीमाओं को स्थापित करना आवश्यक है। प्रत्येक मॉड्यूल के परिभाषित इनपुट और आउटपुट होने चाहिए। एक मॉड्यूल के लिए समय आरेख में उन सिग्नलों पर ध्यान केंद्रित करना चाहिए जो उस सीमा को पार करते हैं। आंतरिक विवरण को छिपाया जा सकता है, जब तक कि वे सीमा समय को सीधे प्रभावित न करें।

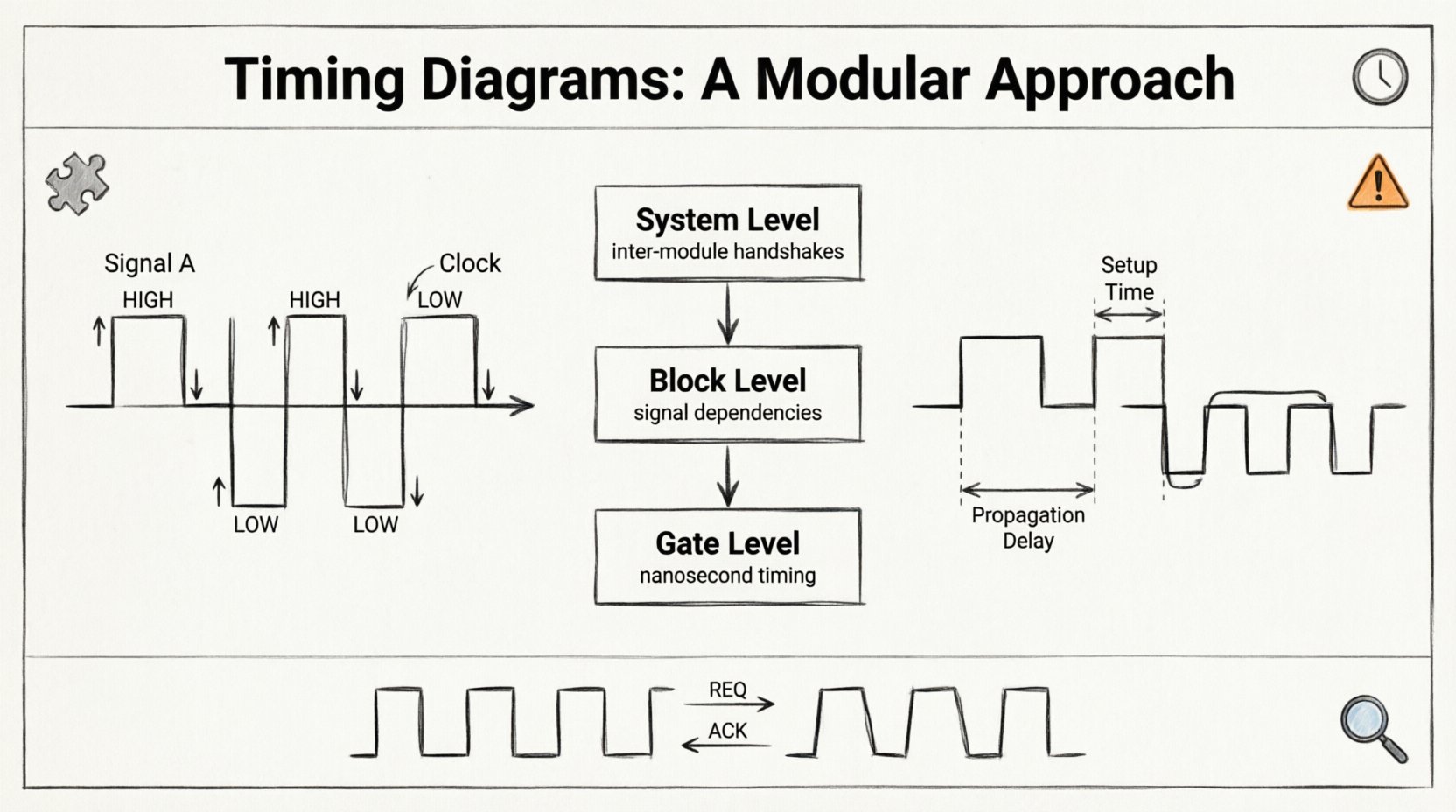

| मॉड्यूल स्तर | फोकस क्षेत्र | विवरण की विस्तृतता |

|---|---|---|

| प्रणाली स्तर | मॉड्यूल के बीच संचार | उच्च स्तर के हैंडशेक |

| ब्लॉक स्तर | आंतरिक डेटा पथ | विशिष्ट सिग्नल निर्भरता |

| गेट स्तर | प्रसारण देरी | सटीक नैनोसेकंड समय |

इन स्तरों के अनुसार आरेखों को व्यवस्थित करने से इंजीनियर जानकारी के स्पष्ट पदानुक्रम को बनाए रख सकते हैं। इस संरचना सुनिश्चित करती है कि डिजाइन प्रक्रिया के सही चरण के लिए सही स्तर की विस्तृत जानकारी उपलब्ध हो।

सिग्नल अवस्थाओं और संक्रमणों को समझना 📊

जब मॉड्यूलर संरचना तैयार हो जाती है, तो अगला चरण विशिष्ट सिग्नलों के विश्लेषण करना होता है। सभी सिग्नल एक ही तरीके से नहीं व्यवहार करते हैं। कुछ सिग्नल निरंतर होते हैं, जबकि अन्य किनारे-द्वारा ट्रिगर होते हैं। प्रत्येक सिग्नल की प्रकृति को समझना सटीक आरेख निर्माण के लिए आवश्यक है।

सामान्य सिग्नल श्रेणियाँ इस प्रकार हैं:

- घड़ी सिग्नल: प्रणाली की धड़कन। ये आवर्ती होते हैं और अवस्था परिवर्तन को प्रेरित करते हैं। इनके लिए आमतौर पर सख्त आवृत्ति और ड्यूटी साइकिल की आवश्यकता होती है।

- डेटा सिग्नल: स्थानांतरित की जा रही वास्तविक जानकारी। इन्हें घड़ी के संबंध में विशिष्ट खंडों में स्थिर रहना चाहिए।

- नियंत्रण सिग्नल: ऐसे सिग्नल जो कार्यक्षमता को सक्षम या अक्षम करते हैं, जैसे चिप सेलेक्शन या एनेबल।

- रीसेट सिग्नल: प्रारंभिक सिग्नल जो प्रणाली को एक ज्ञात अवस्था में लाते हैं।

इन लाइनों पर संक्रमण क्रांतिक होते हैं। एक बढ़ते किनारे के लिए एक क्रिया शुरू करने की संभावना होती है, जबकि गिरते किनारे के लिए इसे पूरा करने की संभावना होती है। असमान समय वाली प्रणालियों में, इन किनारों के बीच संबंध कम भविष्यवाणी योग्य होता है, जिसके लिए अधिक विस्तृत विश्लेषण की आवश्यकता होती है।

प्रसारण देरी का दृश्यीकरण

कोई भी सिग्नल तुरंत नहीं बदलता है। भौतिक सीमाएँ प्रसारण देरी के कारण होती हैं। जब कोई सिग्नल एक घटक से निकलता है, तो तार के माध्यम से अगले घटक तक पहुँचने में समय लगता है। समय आरेखों में इस लेटेंसी को ध्यान में रखना आवश्यक है। यदि एक आरेख समय T पर सिग्नल बदलने को दिखाता है, तो प्राप्त करने वाला सिरा इसे T + Δt तक नहीं देख सकता है।

प्रसारण देरी को नजरअंदाज करने से सिमुलेशन और कार्यान्वयन में महत्वपूर्ण त्रुटियाँ हो सकती हैं। इंजीनियरों को इन देरियों को मॉडल करना चाहिए ताकि पूरे पथ में सेटअप और होल्ड समय को पूरा किया जा सके।

महत्वपूर्ण समय सीमाओं की व्याख्या ⚠️

डिजिटल डिज़ाइन में विफलता का सबसे सामान्य कारण समय सीमा का उल्लंघन है। ये उल्लंघन तब होते हैं जब सिग्नल आवश्यक स्थिरता खंडों को पूरा नहीं करते हैं। इस व्यवहार को नियंत्रित करने वाले दो मुख्य सीमाएं हैं: सेटअप समय और होल्ड समय।

सेटअप समय

सेटअप समय वह न्यूनतम समय है जिसके लिए डेटा को सक्रिय क्लॉक किनारे से पहले स्थिर रहना चाहिए। यदि डेटा बहुत देर से आता है, तो फ्लिप-फ्लॉप सही मान को कैप्चर नहीं कर सकता है। यह सीमा एक प्रणाली की अधिकतम संचालन आवृत्ति निर्धारित करने के लिए महत्वपूर्ण है। यदि क्लॉक अवधि संचरण देरी और सेटअप समय के योग से कम है, तो प्रणाली विफल हो जाएगी।

सेटअप समय के लिए मुख्य विचारों में शामिल हैं:

- सबसे खराब स्थिति का पता लगाने के लिए सबसे लंबे मार्ग का विश्लेषण आवश्यक है।

- प्रक्रिया, वोल्टेज और तापमान में भिन्नता देरी को प्रभावित करती है।

- क्लॉक जिटर उपलब्ध सेटअप विंडो में कटौती कर सकता है।

होल्ड समय

होल्ड समय वह न्यूनतम समय है जिसके लिए डेटा को सक्रिय क्लॉक किनारे के बाद स्थिर रहना चाहिए। यदि डेटा बहुत जल्दी बदल जाता है, तो फ्लिप-फ्लॉप गलत मान को कैप्चर कर सकता है या एक अस्थिर अवस्था में प्रवेश कर सकता है। सेटअप समय के विपरीत, होल्ड समय क्लॉक आवृत्ति से स्वतंत्र है। इसका निर्धारण घटक की आंतरिक देरी और बाहरी पथ पर निर्भर करता है।

होल्ड समय के उल्लंघन अक्सर ठीक करने में कठिन होते हैं क्योंकि इन्हें क्लॉक को धीमा करके ठीक नहीं किया जा सकता है। इसके बजाय, इन्हें डेटा मार्ग में देरी जोड़ने या तर्क को पुनर्डिज़ाइन करके ठीक किया जाना चाहिए।

समय सीमा सारांश

| सीमा | परिभाषा | आवृत्ति पर प्रभाव | निवारण विधि |

|---|---|---|---|

| सेटअप समय | क्लॉक किनारे से पहले स्थिर | अधिकतम आवृत्ति को सीमित करता है | तर्क मार्ग को अनुकूलित करें |

| होल्ड समय | क्लॉक किनारे के बाद स्थिर | आवृत्ति से स्वतंत्र | बफर देरी जोड़ें |

| संचरण देरी | तर्क के माध्यम से यात्रा करने में लगने वाला समय | दोनों को प्रभावित करता है | परिपथ अनुकूलन |

आम गलतियाँ और उल्लंघन 🚫

एक मॉड्यूलर दृष्टिकोण के साथ भी, त्रुटियाँ छिप सकती हैं। आम गलतियों को पहचानने से डिज़ाइन चरण के दौरान उन्हें रोकने में मदद मिलती है। हार्डवेयर सत्यापन में कई प्रकार के उल्लंघन अक्सर पाए जाते हैं।

- अस्थिरता: जब कोई सिग्नल बिल्कुल क्लॉक एज पर बदलता है, तो यह घटित होता है। फ्लिप-फ्लॉप आउटपुट अनिश्चित हो जाता है। यह क्लॉक डोमेन के पार जाने पर आम है।

- ग्लिचेस: लॉजिक पाथ के अंतर के कारण होने वाले छोटे, अनचाहे पल्स। इनके कारण गलत स्थिति परिवर्तन हो सकते हैं।

- क्लॉक स्क्यू: जब क्लॉक सिग्नल विभिन्न घटकों पर अलग-अलग समय पर पहुंचता है। इससे प्रभावी समय सीमा कम हो जाती है।

- रेस कंडीशन्स: जब परिणाम घटनाओं के क्रम पर निर्भर करता है, जो असिंक्रोनस डिजाइन में अनिश्चित होता है।

इन समस्याओं को दूर करने के लिए समय आरेख का ध्यान से विश्लेषण करना आवश्यक है। उन ओवरलैपिंग विंडो को देखें जहां स्थिरता गारंटी नहीं है। सुनिश्चित करें कि रीसेट अनुक्रम सही तरीके से अपनाए जाएं ताकि अपरिभाषित स्थितियों से बचा जा सके।

मॉड्यूलर वर्कफ्लो को लागू करना 🛠️

इस पद्धति को प्रभावी ढंग से लागू करने के लिए, संरचित वर्कफ्लो का पालन करें। इससे यह सुनिश्चित होता है कि समय संबंधी हर पहलू को बिना दोहराव के कवर किया जाए।

- इंटरफेस को परिभाषित करें:प्रत्येक मॉड्यूल के लिए सभी इनपुट और आउटपुट को स्पष्ट रूप से सूचीबद्ध करें।

- क्लॉक डोमेन की पहचान करें:यह तय करें कि कौन से सिग्नल किस क्लॉक डोमेन से संबंधित हैं।

- डेटा पाथ को मैप करें:स्रोत से गंतव्य तक पथ का अनुसरण करें।

- प्रतिबंध लागू करें:प्रत्येक फ्लिप-फ्लॉप के लिए सेटअप और होल्ड आवश्यकताएं निर्धारित करें।

- संक्रमण की पुष्टि करें:किनारों के संरेखण और पल्स चौड़ाई की जांच करें।

- एकीकरण की समीक्षा करें:सुनिश्चित करें कि मॉड्यूल आरेखों को जोड़ने पर वे संरेखित हों।

प्रत्येक चरण पिछले चरण पर निर्भर करता है। एक चरण को छोड़ने से कवरेज में खामियां आ सकती हैं। उदाहरण के लिए, क्लॉक डोमेन को नजरअंदाज करने से सिंक्रोनाइजेशन विफलताएं हो सकती हैं, जिन्हें बाद में डीबग करना मुश्किल होता है।

मल्टी-क्लॉक डोमेन का प्रबंधन 🌐

जैसे-जैसे डिजाइन बढ़ता है, बहुत सारी क्लॉक आवृत्तियां आवश्यक हो जाती हैं। सिस्टम के कुछ हिस्से तेज चलते हैं, जबकि अन्य धीमे। इन डोमेन को सिंक्रोनाइज करना समय विश्लेषण के सबसे चुनौतीपूर्ण पहलुओं में से एक है।

जब सिग्नल एक क्लॉक डोमेन से दूसरे क्लॉक डोमेन में पार जाते हैं, तो समय आरेख में दोनों क्लॉक के बीच संबंध को दर्शाना आवश्यक है। यदि क्लॉक असिंक्रोनस हैं, तो अस्थिरता से बचने के लिए विशेष सावधानी बरतने की आवश्यकता होती है। इस स्थानांतरण को सुरक्षित ढंग से प्रबंधित करने के लिए सिंक्रोनाइजर चेन या हैंडशेक प्रोटोकॉल जैसी तकनीकों का उपयोग किया जाता है।

मल्टी-क्लॉक डिजाइन के लिए मुख्य रणनीतियां इस प्रकार हैं:

- ग्रे कोडिंग:बहु-बिट काउंटर को डोमेन के बीच सुरक्षित रूप से स्थानांतरित करने के लिए ग्रे कोड का उपयोग करना।

- FIFO बफर: पढ़ने और लिखने के घड़ी सिग्नल को अलग करने के लिए पहले आने वाले को पहले निकालने वाले भंडारण का उपयोग कर रहे हैं।

- हैंडशेक सिग्नल: डेटा की वैधता सुनिश्चित करने के लिए अनुरोध/पुष्टि जोड़ी का उपयोग कर रहे हैं।

इन परिस्थितियों के लिए समय आरेखों में दोनों क्षेत्रों के घड़ी के किनारों को स्पष्ट रूप से दिखाना आवश्यक है। इससे इंजीनियरों को देखने में मदद मिलती है कि डेटा प्राप्त करने वाली घड़ी द्वारा इसे पकड़ने के लिए पर्याप्त समय तक स्थिर रहता है या नहीं।

दृश्य डेटा के साथ डिबगिंग 🔍

जब डिज़ाइन विफल होता है, तो समय आरेखों को देखने के लिए पहले स्थान होता है। डिबगिंग में धैर्य और एक व्यवस्थित दृष्टिकोण की आवश्यकता होती है। विफल मॉड्यूल को अलग करके शुरू करें। अपेक्षित आरेख की तुलना वास्तविक तरंगरेखा से करें।

अंतरों में निरीक्षण करें:

- घड़ी के संबंध में सिग्नल समय।

- नियंत्रण सिग्नल की पल्स चौड़ाई।

- रीसेट के दौरान राज्य संक्रमण।

- डेटा लाइनों पर ग्लिच।

उपकरण अक्सर नैनोसेकंड स्तर की विस्तृत जांच के लिए ज़ूम क्षमता प्रदान करते हैं। उल्लंघन के ठीक समय की पुष्टि करने के लिए इन विशेषताओं का उपयोग करें। दृश्य डेटा को तर्क के साथ संबंधित करें ताकि मूल कारण को समझा जा सके।

डिज़ाइन अखंडता पर अंतिम विचार 💡

समय आरेख केवल तकनीकी ड्राइंग से अधिक हैं; वे विश्वसनीय डिजिटल प्रणालियों के लिए नक्शा हैं। एक मॉड्यूलर दृष्टिकोण अपनाकर, इंजीनियर जटिलता को प्रबंधित कर सकते हैं और स्पष्टता बनाए रख सकते हैं। इस विधि को स्केलेबिलिटी का समर्थन मिलता है और महंगी त्रुटियों के होने की संभावना कम हो जाती है।

हार्डवेयर डिज़ाइन में सफलता विवरणों पर ध्यान देने पर निर्भर करती है। हर नैनोसेकंड महत्वपूर्ण है। हर संक्रमण महत्वपूर्ण है। इन सिद्धांतों को कठोरता से लागू करके, टीमें प्रतिबंधित वास्तविक दुनिया की स्थितियों में भविष्यवाणी करने वाले प्रणालियों का निर्माण कर सकती हैं। समय विश्लेषण के मॉड्यूलर विभाजन से यह सुनिश्चित होता है कि कोई विवरण न छूटे, जिससे दृढ़ और कुशल हार्डवेयर समाधान प्राप्त होते हैं।

तकनीक विकसित होने के साथ इन कौशलों के निरंतर सुधार की आवश्यकता होती है। नए मानक और तेज गति के लिए अद्यतन विश्लेषण तकनीकों की आवश्यकता होती है। डिजिटल इंजीनियरिंग के क्षेत्र में प्रतिस्पर्धात्मक लाभ बनाए रखने के लिए उभरती हुई उत्तम विधियों के बारे में जानकारी रखें।