デジタル電子工学およびコンピュータ工学において、信号間の時間的関係を理解することは、システムの信頼性にとって基本的なものです。タイミング図は、これらの関係を記述するための主要な視覚的言語です。信号の状態を時間軸に対してマッピングすることで、エンジニアはデータの流れ、クロック同期、回路内の潜在的な危険を可視化できます。このガイドでは、波形解析に見られる構造的要素、動作パターン、および重要なシナリオについて探求します。

集積回路の設計から組み込みシステムのデバッグまで、正確なタイミング表現を解釈し作成する能力は、核心的なスキルです。この文書では、信号の相互作用、遵守すべき制約、検証中に遭遇する一般的な落とし穴について、技術的な概要を提供します。

📐 タイミング図の構造

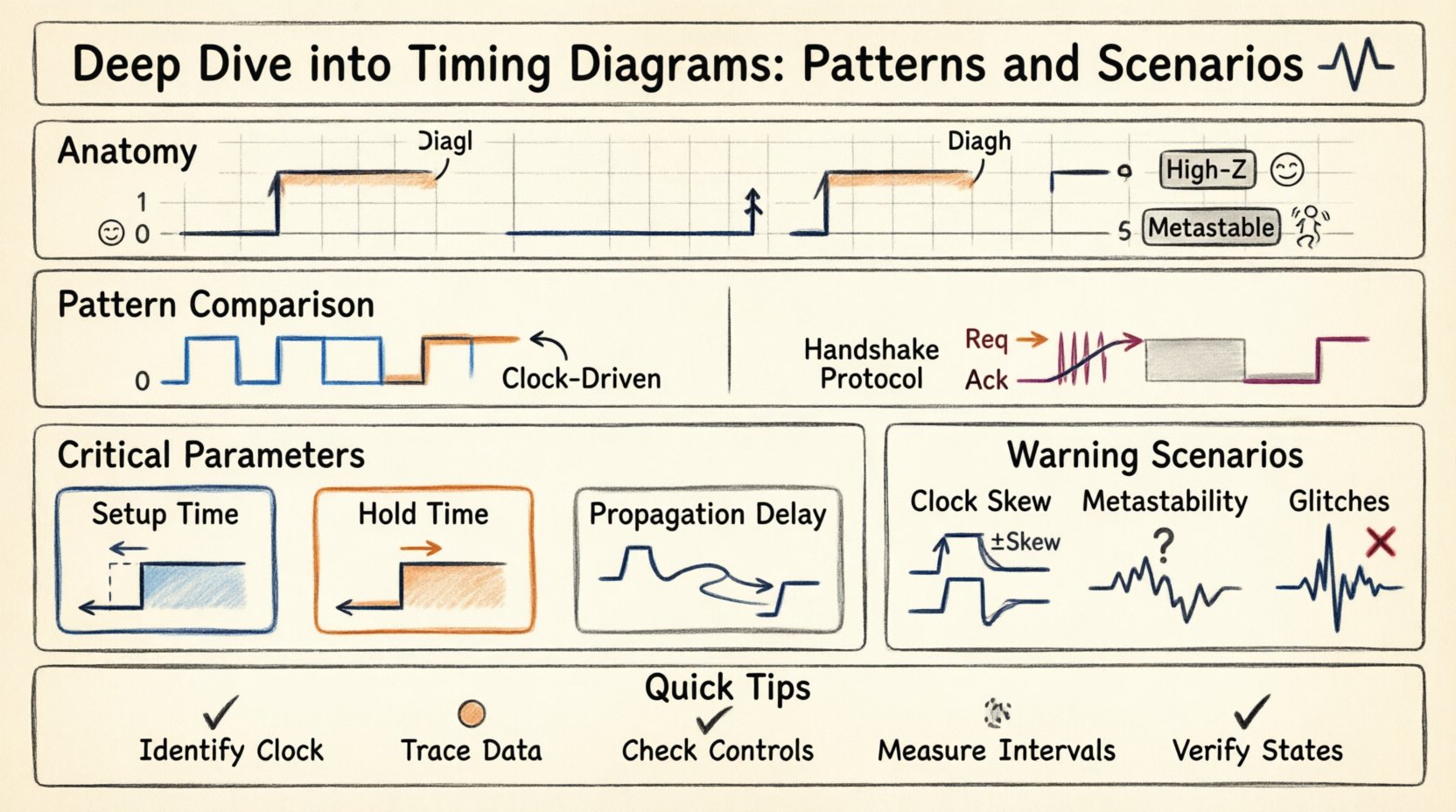

タイミング図は、横軸が時間を、縦軸が信号レベルを表すグラフィカルな表現です。各水平線は設計内の特定の信号またはネットに対応しています。構成要素を理解することは、正確な解析への第一歩です。

- 時間軸:通常、左から右へ水平に進行します。観察対象のイベントのスケールに応じて、線形または対数的になることがあります。

- 信号線:電圧レベルを表す個別のトレースです。高電圧は通常論理1を、低電圧は論理0を示します。

- 遷移:状態の変化を示す垂直線であり、例えば立ち上がりエッジ(0から1)や立ち下がりエッジ(1から0)が含まれます。

- ラベル:特定の信号、ピン、または制御線を識別するテキストの注釈です。

- マーカー:特定のイベント、例えばクロックパルスやリセットトリガを示すために、しばしば垂直の破線が使用されます。

🔢 ロジックレベルと状態

デジタル信号は常に0または1に厳密に存在するわけではありません。実際の状況では、信号は定義されていない状態や高インピーダンス状態にあることがあります。完全な図はこれらの変化を考慮しなければなりません。

- 論理高(1):信号は論理的に真と認識される電圧レベルに駆動されています。

- 論理低(0):信号は論理的に偽と認識される電圧レベルに駆動されています。

- 高インピーダンス(High-Z):信号はドライバから切り離されており、実質的に浮遊状態です。これは3状態バッファで一般的です。

- 不安定状態(Metastable):信号が高でも低でもない状態であり、非同期遷移中にしばしば発生します。

⚙️ 一般的なタイミングパターン

設計はデータの整合性を確保するために予測可能なパターンに従います。これらのパターンは、データが制御信号に対してどのように移動するかを定義します。これらのパターンを認識することで、設計が仕様を満たしているかを検証しやすくなります。

📌 同期データ転送

同期設計は、動作を調整するためにグローバルなクロック信号に依存します。データは特定の瞬間、通常はクロックの立ち上がりエッジまたは立ち下がりエッジでのみサンプリングされます。

- クロック駆動: すべての状態変化はクロックエッジに関連して発生する。

- データ有効性: データはクロックエッジの前に安定している必要があり、その後も安定したまま保たれる必要がある。

- プロパゲーション: クロックエッジと出力が変化するまでの間に遅延がある。

📌 非同期ハンドシェイキング

非同期通信は共有クロックに依存しない。代わりに、データが準備できたときや受信されたときに示すための制御信号を使用する。

- リクエスト(Req): 送信者がデータが利用可能であることを示す。

- アックノリッジ(Ack): 受信者がデータが受け入れられたことを示す。

- ウェイトステート: 送信者は受信者が準備できるまで一時停止する可能性がある。

| 特徴 | 同期パターン | 非同期パターン |

|---|---|---|

| 調整 | グローバルクロック信号 | 制御ハンドシェイク信号 |

| 速度 | 一般的に高い | 変動する。応答に依存する |

| 複雑さ | クロック配布ネットワーク | プロトコル論理 |

| レイテンシ | 予測可能 | 変動する |

⏱️ 重要なタイミングパラメータ

視覚的な線を超えて、特定の数値制約が回路が正しく機能するかどうかを定義している。これらのパラメータは静的タイミング解析にとって重要であり、物理的限界に対して検証されなければならない。

🛑 ラッチアップ時間

ラッチアップ時間は、クロックエッジの前にデータ信号が安定して保持される必要がある最小時間です。データがクロックエッジに近すぎるように変化すると、受信側のフリップフロップが正しい値をキャプチャできなくなる可能性があります。

- 測定方法:アクティブなクロックエッジから時間軸の逆方向に測定する。

- リスク:違反すると、誤ったデータのキャプチャが発生する。

- 要件:データパス遅延は、ラッチアップ時間ウィンドウを満たすために十分に長くなければならない。

🛑 ホールド時間

ホールド時間は、クロックエッジの後にデータ信号が安定して保持される必要がある最小時間です。これにより、ラッチが入力値を確実にロックするのに十分な時間が確保されます。

- 測定方法:アクティブなクロックエッジから時間軸の前方向に測定する。

- リスク:違反すると、メタスタビリティまたは誤ったデータのキャプチャが発生する。

- 要件:データパス遅延は、ホールド時間ウィンドウを確保できるように十分に短くなければならない。

⚡ 伝播遅延

これは、論理ゲートの入力から出力まで信号が伝わるのにかかる時間です。負荷容量およびトランジスタの内部抵抗によって異なります。

- tpd(高から低へ):1から0に遷移するまでの時間。

- tpd(低から高へ):0から1に遷移するまでの時間。

- スキュー:並列パス間の遅延の差異。

🚨 重要なタイミング状況

特定の状況は、慎重な分析を要する大きな課題を提示する。これらの状況は、異なるクロックドメイン間の相互作用や、ハードウェアの物理的制限が関係することが多い。

🔄 クロックスキー

クロックスキーとは、クロック信号が異なるコンポーネントに異なるタイミングで到達するときに発生する現象である。これはルーティングの違いや物理的な距離の違いによって起こりうる。

- ポジティブスキー: デスティネーションクロックがソースクロックより遅れて到達する。

- ネガティブスキー: デスティネーションクロックがソースクロックより早く到達する。

- 影響:セットアップ時間の余裕を実質的に減少させたり、ホールド時間の違反を増加させたりする可能性がある。

🌊 メタスタビリティ

メタスタビリティとは、フリップフロップの出力が高電圧でも低電圧でもない状態を指す。通常、セットアップ時間またはホールド時間の違反が発生した場合、特に非同期なクロスングで発生する。

- 解決方法: 回路は最終的に安定した状態に落ち着くが、その時間は予測できない。

- 修正方法: シンクロナイザー(マルチステージのフリップフロップ)を使用して、障害の確率を低下させる。

- MTBF: 故障間平均時間(MTBF)は、メタスタビリティの解決率に基づいて計算される。

📉 グリッチ

グリッチとは、信号に一時的なスパイクが発生する現象で、有効な遷移と誤認されることがある。これは、異なる経路における伝播遅延の違いによって頻繁に発生する。

- 原因: 異なる経路長またはレースコンディション。

- 影響: 下流の論理回路で予期しない状態変化を引き起こす可能性がある。

- 緩和策: フィルタリング論理を使用するか、適切なタイミングクロージャーを確保する。

🔍 波形の解析

タイミング図を確認する際は、体系的なアプローチを取ることで、細部を見逃すことがない。エンジニアはデータ信号および制御信号の流れを追跡し、不一致を特定する必要がある。

🔍 ステップバイステップの解析

- クロックを特定する: 主クロック信号を特定する。立ち上がりエッジまたは立ち下がりエッジでトリガされるかを確認する。

- データパスを追跡する: ソースから宛先までデータラインを追跡してください。

- 制御信号を確認する:有効、リセット、クリア信号が正しくアサートされているか確認してください。

- インターバルを測定する:特定のイベント間の時間を計算し、セットアップおよびホールド要件を検証します。

- 状態遷移を確認する:出力状態が期待される論理関数と一致していることを確認してください。

🔍 エッジトリガの読み取り

コンポーネントが信号エッジにどのように反応するかを理解することは重要です。

- ポジティブエッジトリガ: アクションは低から高への遷移時に発生します。

- ネガティブエッジトリガ: アクションは高から低への遷移時に発生します。

- レベルトリガ: シグナルが特定のレベルに保たれている間、アクションが発生します。

🛠️ ドキュメント作成の基準

明確なドキュメントは、他のエンジニアが設計を理解できるようにします。表記やラベルの一貫性が、デバッグや引継ぎ時の誤解を防ぎます。

📝 ラベル付けの慣例

- シグナル名: 一貫した命名規則を使用してください(例:

clk,rst_n,data_in). - 極性: アクティブロー信号を明確に示し、しばしばバー記号や接尾語を使用します。

- 単位: 時間軸上に時間単位(ns、µs、ms)を明確に記載してください。

- スケーリング:イベントの内容に応じて、時間スケールが適切であることを確認してください。

📝 視覚的明確性

- 間隔:可能な限り、線が重ならないようにしてください。

- コントラスト:異なる信号タイプには、明確に区別できる色や線の太さを使用してください。

- 注釈:複雑な動作や特定の制約を説明するメモを追加してください。

- グリッド:時間間隔の測定を支援するために、グリッド背景を使用してください。

🚧 ファイルのトラブルシューティングワークフロー

設計がタイミング要件を満たさない場合、構造化されたトラブルシューティングプロセスにより根本原因を特定できます。これは、図面を物理的制約と照らし合わせて検討することを含みます。

🚧 違反の特定

- セットアップ時間の確認:データがクロックに対して遅れて到着しているか?

- ホールド時間の確認:データがクロックの直後に早すぎるように変化しているか?

- クロック周波数の確認:クロック周期が必要な最小値より短いか?

🚧 軽減戦略

- パイプラインレジスタ:長いコンビネーショナルパスを断つために、追加のレジスタを挿入してください。

- クロックゲーティング:活動を減らして消費電力を低下させ、タイミングの改善も可能になります。

- バッファ挿入:並列パス間の遅延をバランスさせるために、バッファを追加してください。

- タイミング制約:データフローに影響しない論理を除外するために、誤ったパスを定義してください。

📈 設計のベストプラクティス

設計段階でベストプラクティスを採用することで、開発サイクルの後半でタイミング問題が発生する可能性が低くなります。予防的な計画立案は、対応的な修正よりも効率的です。

- インターフェースを標準化する:データ転送には既知のプロトコルを使用し、タイミングの検証を簡素化する。

- 非同期パスを最小限に抑える:非同期な相互作用を最小限に抑え、メタスタビリティのリスクを低減する。

- 仮定を文書化する:設計仕様書にクロック周波数と電圧レベルを明確に記載する。

- 定期的にレビューする:プロジェクトの各主要マイルストーンでタイミングレビューを実施する。

🎯 主な概念の要約

タイミング図は、デジタルシステムの時間的挙動を可視化するための必須ツールです。データ信号と制御信号が時間とともにどのように相互作用するかを明らかにし、セットアップ時間やホールド時間といった重要な制約を強調します。これらの図の構造を理解することで、エンジニアはパターンを識別し、エラーを予測し、堅牢なシステム性能を確保できます。

主な教訓には、同期的パターンと非同期的パターンの違い、クロックスキー管理の重要性、明確な文書化基準の必要性が含まれます。これらの原則に従うことで、信頼性の高い設計が容易になり、検証プロセスも簡素化されます。

波形データの継続的な分析により、設計が運用限界内に保たれます。技術の進歩とクロック速度の向上に伴い、タイミング解析に求められる精度はさらに重要になります。これらの概念を習得することで、安定した高パフォーマンスなデジタルアーキテクチャの構築が可能になります。