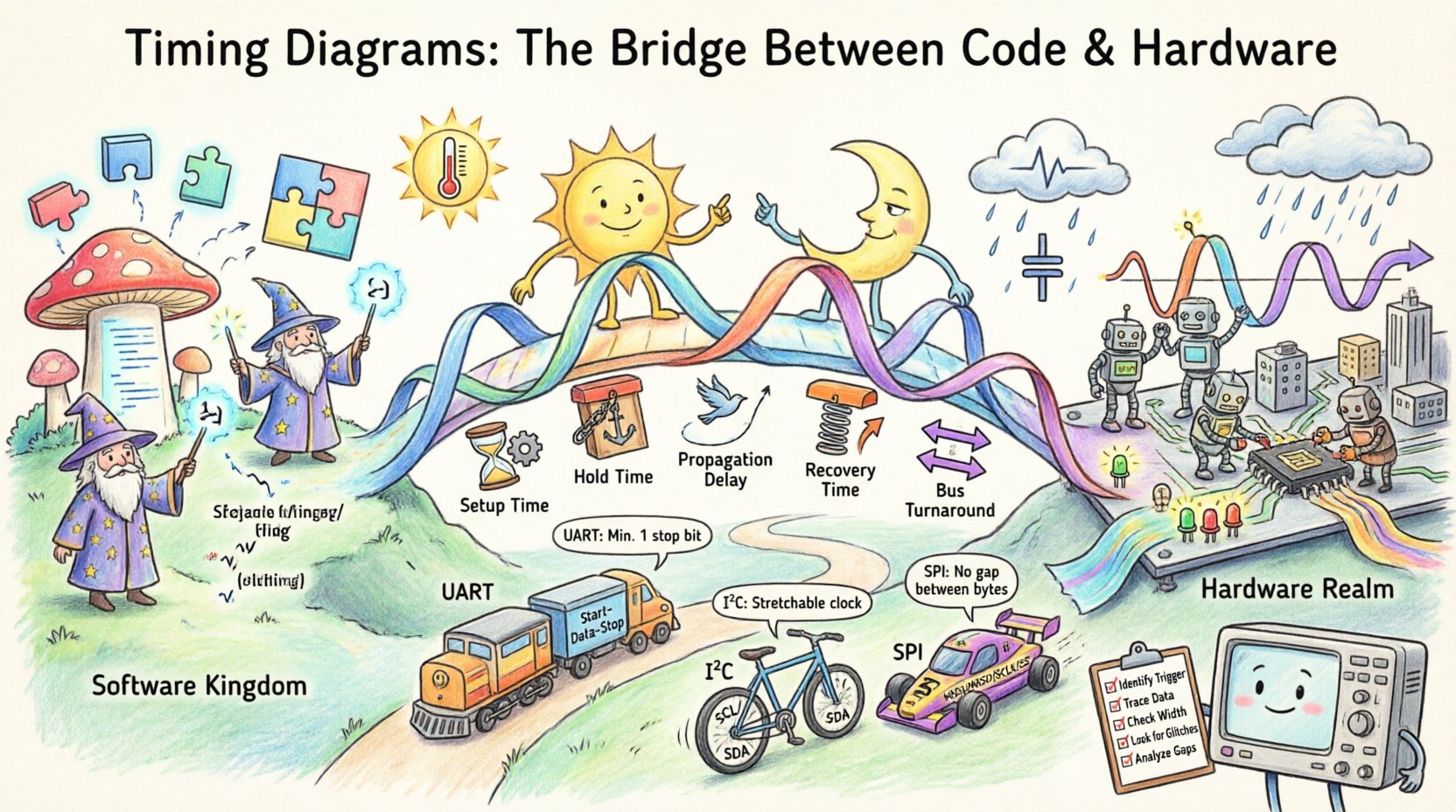

ソフトウェアエンジニアがコードを書くとき、彼らは命令、変数、論理フローのことを考えます。ハードウェアエンジニアが回路を設計するとき、彼らは電圧レベル、伝播遅延、クロックサイクルのことを考えます。この二つの世界はしばしば摩擦状態にあります。コードは特定の論理的瞬間に信号が到着することを期待していますが、ハードウェアはノイズ、温度、電気抵抗の影響を受ける物理的な時間で動作しています。この二つの領域をつなぐ橋がタイミング図です。

タイミング図は単なる図面ではなく、契約です。時間における出来事の正確な関係を定義します。ファームウェアにピンを読み取るのに安全なタイミングを、シリコンにラインを駆動するのに安全なタイミングを伝えます。これらの図を明確に理解しないと、組み込みシステムは予測不能に失敗します。データ破損、レースコンディション、システムの停止が一般的な問題になります。このガイドでは、タイミング図のメカニズム、その背後にある物理現象、そして効果的に読み書きする方法について探ります。

📊 シグナルの構造

本質的に、デジタル論理は2値状態に依存しています。しかし物理世界では、これらの状態は電圧レベルによって表現されます。「High」は3.3ボルトである場合があり、「Low」は0ボルトである場合があります。しかし、シグナルは瞬時に切り替わるわけではありません。有限の期間をかけて上昇し、下降します。タイミング図はこの遷移を可視化します。

これらの図の視覚的言語を理解することは、習得への第一歩です。主な要素には以下が含まれます:

- 時間軸:通常は水平で、左から右へと進みます。線形または対数のどちらかですが、ほとんどの論理解析では線形が標準です。

- シグナルライン:特定の配線、ピン、または内部ノードを表す垂直線です。

- 遷移:LowからHighへの移動(立ち上がりエッジ)またはHighからLowへの移動(立ち下がりエッジ)。これらのエッジは、順序回路における状態変化をしばしばトリガーします。

- レベル:遷移の前または後の信号の安定状態。

- ラベル:特定のパルスまたは期間の意味を明確にするテキストの注釈。

単純なクロック信号を考えてみましょう。これはHighとLowの間を振動します。1つの完全なサイクルを完了するのにかかる時間が周期です。周期の逆数が周波数です。タイミング図では、クロックがシステムの鼓動の役割を果たします。他のすべての信号は、これらのエッジに同期されることがよくあります。

🕰️ クロックドメイン

ほとんどのデジタルシステムはクロックドメイン内で動作します。これは同じタイミングリファレンスを共有する回路のグループです。しかし、信号はしばしば異なるドメイン間を渡ります。これにより複雑性が生じます。高速ドメインで生成された信号が、遅いドメインに到着が遅れたり、早すぎたりすると、ホールド違反が発生する可能性があります。

タイミングを分析する際には、以下の点を考慮する必要があります:

- クロックスキー:クロック信号が異なるコンポーネントに到着する時間の差。送信側にクロックが受信側より先に到着すると、タイミングマージンが狭まります。

- 位相シフト:一部のシステムでは、信号はクロックエッジと同期しておらず、サイクルの途中に発生します。

- ジッター:信号のタイミングのばらつきです。ジッターはランダムまたは決定論的であることがあります。ノイズマージンを低下させ、図を予測不可能にします。

ハードウェアとインターフェースするためのコードは、安定したクロックを前提としています。物理的なクロックが温度や電圧の変動によってずれると、タイミング図は現実と一致しなくなります。そのため、タイミング図には許容範囲帯や最悪ケースのシナリオを含める必要があります。

⚙️ 重要なタイミングパラメータ

特定のパラメータが信号整合性の限界を定義します。これらの値はデータシートに頻繁に記載されていますが、タイミング図の文脈の中で理解するのが最も適切です。以下の表は、エンジニアが評価しなければならない最も重要なパラメータを概説しています。

| パラメータ | 定義 | システムへの影響 |

|---|---|---|

| セットアップ時間 | データが安定している必要がある最小時間前にクロックエッジの | 違反すると、受信フリップフロップは正しい値をキャプチャできなくなる。 |

| ホールド時間 | データが安定したまま保たれる必要がある最小時間後にクロックエッジの | 違反すると、フリップフロップは準安定状態に入ることがある。 |

| プロパゲーション遅延 | 信号が入力から出力まで伝わるのにかかる時間。 | 遅延は論理ゲートを跨いで蓄積され、クロックサイクルを逃す可能性がある。 |

| リカバリータイム | 非同期イベントの後に制御信号が通常状態に戻るために必要な時間。 | リセットや割り込みからのシステムの回復速度に影響する。 |

| バスのトランザイション時間 | バスを出力モードから入力モードに切り替えるために必要な時間。 | I2Cや1-Wireのような双方向バスにおいて重要である。 |

これらのパラメータを違反しても、必ずしも即座にクラッシュするわけではない。時々、システムは99%の確率で正常に動作し、特定の条件下でのみ失敗する。これがタイミング解析が反復的プロセスである理由である。最悪の電圧および温度条件下でも図が成り立つことを確認しなければならない。

👀 波形の読み方

タイミング図の読み取りには体系的なアプローチが必要である。ハードウェアの問題をデバッグする際には、信号レベルだけを見ないでください。信号間の関係性に注目してください。

波形を分析するには以下の手順に従ってください:

- トリガを特定する:シーケンスを開始するイベントを見つける。通常はクロックエッジまたは外部割り込みである。

- データを追跡する:トリガに対してデータラインを追跡する。データはクロックエッジの前か後か?

- 幅を確認する: パルスの持続時間を測定する。 「High」信号は受信ロジックによって認識できるほど十分に長いか?

- ギャップを確認する: 安定状態の間に発生する不正なパルス。これはクロストークやロジックハザードによって引き起こされることがある。

- ギャップを分析する: 1回のトランザクションの終了と次のトランザクションの開始の間の時間を確認する。ハードウェアがリセットするのに十分な時間が確保されているか?

しばしば問題はギャップに起因する。マイコンが周辺機器にデータを書き込んだ後、次のバイトを送信する前に特定の遅延が必要な場合がある。図面にこれらのバイトがギャップなしに連続して表示されている場合、コードはハードウェアに対してあまりに攻撃的である可能性が高い。

🔌 一般的なプロトコルとタイミング

異なる通信プロトコルは異なるタイミング制約を課す。これらの制約を理解することは、信頼性の高い通信を実現するファームウェアを書く上で不可欠である。

| プロトコル | 重要なタイミング特性 | 一般的な故障モード |

|---|---|---|

| UART | スタートビットの後にデータビット、ストップビットが続く。ボーレートに依存する。 | 送信側と受信側のクロックドリフトによるビットエラー。 |

| I2C | SCLおよびSDAライン。プルアップ抵抗が必要。SDAはSCLがHighの間に安定している必要がある。 | バスホールドアップまたはクロックストレッチングの問題によりタイムアウトが発生する。 |

| SPI | クロック線とデータ線は別々。エッジトリガー(CPOL/CPHA設定)。 | スレーブがマスタクロック速度に対して応答が遅すぎる。 |

| GPIO割り込み | エッジ感度。ISRでの最小限の処理時間が必要。 | 前のサービスルーチンの実行時間が長いため、割り込みが見逃される。 |

例えばSPIでは、クロックエッジのタイミングがデータラインに対してどのタイミングかによって、データが立ち上がりエッジまたは立ち下がりエッジでラッチされるかが決まる。ファームウェアが一方のモードを想定しているのに、ハードウェアがもう一方のモードに設定されている場合、データは正しく読み取れない。タイミング図はこの関係を視覚的に明確にし、設定ミスを防ぐ。

🔍 タイミングに関する問題のデバッグ

システムが不安定に動作する場合、最初に取り出すべきツールはデバッガーではなく、タイミング図である。タイミングを使ったデバッグは、実際の電気的挙動をキャプチャし、想定される設計と比較することを意味する。

一般的なタイミング関連の問題には以下が含まれる:

- メタスタビリティ: シグナルがクロックエッジに近すぎるタイミングでフリップフロップに到達すると、出力が予測不能になる。High、Lowに安定するか、不定な時間にわたって中間状態のままになる可能性がある。

- レースコンディション: 出力がイベントの相対的なタイミングに依存する場合。2つの信号が同時に変化する場合、処理の順序が重要になる。

- 信号整合性:長いトレース上の反射やリングは、誤った遷移を引き起こす可能性がある。図では、クリーンな方形波が表示されるべき場所に振動が現れることがある。

- セットアップ/ホールド違反:データがクロックエッジに非常に近いタイミングで変化している。これは、論理パスに対してクロック速度が高すぎることが原因であることが多い。

これらの問題を解決するには、コードに遅延を追加したり、クロック周波数を変更したり、ハードウェアレイアウトを調整する必要がある場合がある。タイミング図は、これらの変更を自信を持って行うために必要な証拠を提供する。

📝 ドキュメント作成のベストプラクティス

ドキュメント用にタイミング図を作成することは、それを読むことと同じくらい重要である。 poorly documented timing leads to maintenance nightmares. Future engineers will struggle to understand why a specific delay was added to the code.

自らの図を作成する際には、以下のガイドラインに従うこと。

- 標準記号を使用する:凡例に定義されている場合を除き、カスタムアイコンは避ける。標準的な立ち上がり/立ち下がりエッジ表記を使用する。

- すべてにラベルを付ける:読者がすべてのラインが何を表しているかを知っていると仮定してはならない。ピン、信号、状態を明確にラベル付けする。

- 文脈を含める:データラインと併せて、制御信号(チップセレクトやEnableなど)の状態を示す。

- 単位を明記する:常に時間スケールを明記する。マイクロ秒かナノ秒か、クロックサイクルか?

- 重要なパスを強調する:システムの安定性を決定する信号を強調するために、太線または異なる色を使用する。

- バージョン管理:ハードウェアまたはファームウェアが変更されたら、図を更新する。古くなった図はリスクとなる。

ドキュメントは「順調な状態」だけを示すべきではない。エラー状態も示すべきである。タイムアウトが発生したときの図はどのようなものになるか?リセットがトリガーされたときの図はどのようなものになるか?これらのシナリオこそ、多くのバグが隠れている場所であることが多い。

🌡️ 環境要因

タイミング図はしばしば理想的な実験室条件下で生成される。実際の環境はほとんどが理想的ではない。温度、電圧、電磁干渉はすべて信号伝播に影響を与える。

以下の要因を検討する:

- 温度:シリコンの性能は高温で低下する。伝播遅延が増加する。25°Cで動作するシステムが85°Cでは失敗する可能性がある。

- 電圧:低電圧では遅延が増加する。高電圧は遅延を減少させる可能性があるが、電力消費と発熱を増加させる。

- 負荷容量: 長い配線は静電容量を増加させる。これにより信号の立ち上がり・立ち下がり時間が遅れ、パルス幅は実質的に広がるが、遷移が遅くなる。

ロバストな設計はこれらの変動を考慮する。量産用のタイミング図を作成する際には「ワーストケース」のコーナーを考慮すべきである。これは、信号の遷移が最も遅くなる状態とクロックエッジが最も速くなる状態を表すことを意味する。これらの条件下でシステムが動作すれば、ほとんどの状況で動作する。

🛠️ 図の作成と検証

手動での描画は可能だが、現代のエンジニアリングはタイミングの取得と検証に自動化ツールに依存している。しかし、使用するツールに関わらず、原則は同じである。目的は時間の流れを可視化することである。

図の検証時に考慮すべき点:

- データシートと比較する: 図内のタイミング値が使用しているチップのメーカー仕様と一致していることを確認する。

- シミュレーションを実行する: 実際の回路を構築する前に、シミュレーション環境を使って論理をモデル化する。

- 実際のハードウェアを測定する: 実測に代わるものはない。実物の基板から波形を取得し、設計図上に重ねて確認する。

- マージンを確認する: シグナル間に十分な余裕時間があるか?マージンがゼロの場合、何らかの変動が発生すれば失敗する。

検証は継続的なプロセスである。ファームウェアが進化するにつれて、タイミング要件が変化する可能性がある。新しい割り込みハンドラが遅延を導入し、信号がデッドラインを過ぎてしまう可能性がある。継続的な検証により、コードとハードウェアの間の橋渡しが安定した状態を保つ。

🔗 論理と物理の交差点

結局のところ、タイミング図は論理と物理の交差点を表している。論理は「何が起こるべきか」を規定し、物理は「実際に何が起こるか」を規定する。エンジニアの仕事は、この二つの現実を一致させることである。

これらの図の解釈と作成を習得することで、他人が見逃す複雑な障害を診断する能力が得られる。システムがフリーズする理由を推測するのをやめ、タイミング制約がどこで違反されたかを正確に把握できるようになる。このレベルの洞察力は、開発者をデザイナーに変える。

シンプルなセンサインターフェースを設計している場合でも、高速通信バスを設計している場合でも、タイミング図はあなたの主要な参照資料である。書いたコードがハードウェアが期待する時間内に実行されることを保証する。画面に表示される信号がピン上の電圧と一致することを保証する。それは同期の言語である。

これらの図を理解する時間を投資する。コードと同様に真剣に扱うべきである。組み込みシステムでは、タイミングは単なる細部ではない。信頼性の基盤である。コードとハードウェアが時間という同じ言語を話すとき、システムは正確かつ安定した動作を実現する。