デジタルハードウェア設計の複雑な領域において、明確さは極めて重要です。エンジニアや設計者は、信号が時間とともにどのように振る舞うかを伝えるために視覚的な表現に頼っています。タイミング図は、この目的において最も重要なツールの一つです。抽象的な論理を視覚的なタイムラインに変換し、さまざまなコンポーネント間で高・低状態がどのように交互に変化するかを明らかにします。しかし、システムの複雑さが増すにつれて、これらの図は混乱を招くようになります。このガイドでは、タイミング図を効果的に分解・分析するためのモジュラー戦略を検討し、ハードウェア検証における正確性と信頼性を確保します。

データ信号および制御信号の流れを理解することは、機能的障害を防ぐために不可欠です。マイコンコントローラのインターフェースを設計している場合でも、高速通信プロトコルを設計している場合でも、これらの図を読み解き、作成できる能力は、堅牢な設計と脆弱な設計を分ける要因となります。構造的でモジュラーな視点を採用することで、チームは複雑さを管理し、タイミング違反のリスクを低減できます。

タイミング図の基礎を理解する ⏱️

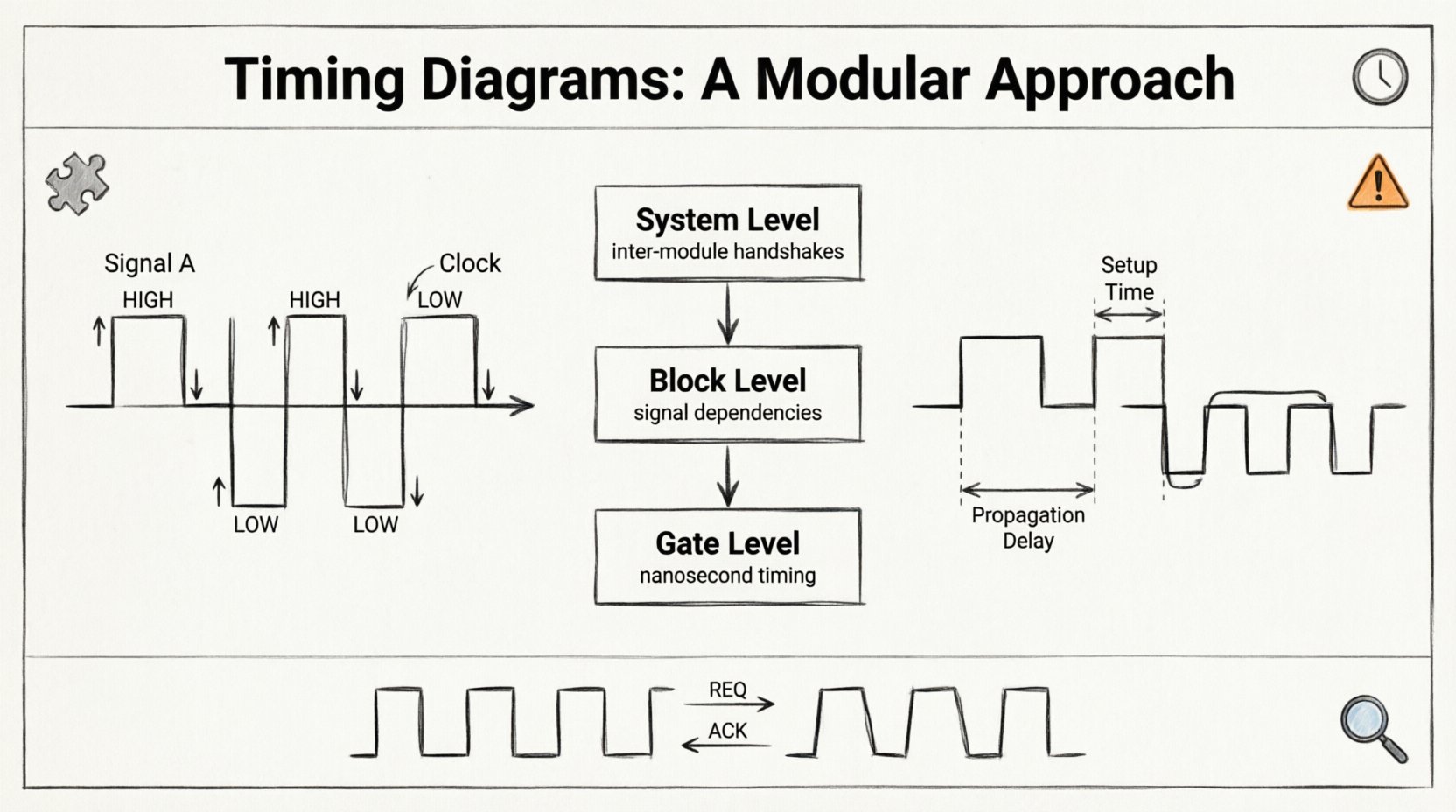

タイミング図は、信号が時間とともにどのように状態を変化するかをグラフィカルに表現したものです。横軸に時間を、縦軸に信号の状態をプロットします。この視覚的な形式により、エンジニアはデジタル回路内の異なる信号間の関係を確認できます。主な目的は、受信コンポーネントがデータをサンプリングする際に、データが安定しており、有効であることを保証することです。

あらゆるタイミング図の基盤を成すいくつかの重要な要素があります:

- 信号線:水平線は、クロック、データ、制御などの特定の信号を伝送する個別のワイヤーやバスを表します。

- 時間軸:水平方向の進行は時間の経過を示し、しばしばナノ秒またはクロックサイクル単位で目盛りが付けられます。

- 論理レベル:信号は通常、二値で表現され、High(1)またはLow(0)として示されます。場合によっては、定義されていない状態や高インピーダンス状態も表示されることがあります。

- 遷移:垂直線は、信号が一つの状態から別の状態に切り替わる瞬間、例えば立ち上がりエッジや立ち下がりエッジを示します。

- 注記:テキストラベルは、図内の特定の制約、遅延、または機能ブロックを定義することが多いです。

これらの基礎を明確に理解しないと、複雑な相互作用を解釈することは困難になります。タイミング図は単なる図面ではなく、送信側と受信側の間の契約です。データが正しく処理されるために必要なルールを規定しています。

複雑な設計におけるモジュラー戦略 🧩

現代のデジタルシステムはほとんど単純ではありません。複数のサブシステムから構成されており、それぞれに独自のタイミング要件があります。全体を一つの図に描こうとすると、混雑や混乱を招くことがよくあります。モジュラーなアプローチは、設計を扱いやすい部分に分割します。この方法により、可読性が向上し、デバッグプロセスが簡素化されます。

モジュラー性が重要な理由

システムをモジュールに分割することで、設計者は全体のアーキテクチャのノイズに巻き込まれることなく、特定のインターフェースに集中できます。タイミング違反が発生した場合、モジュラーな図は問題の原因を特定しやすくなります。認知的負荷を軽減し、別々のブロックを担当する異なるエンジニアチーム間の協力を促進します。

このアプローチの利点には以下が含まれます:

- 問題の隔離:問題は、全体システムではなく特定のブロック内で特定できる。

- 再利用性:一般的なモジュール向けの標準化されたタイミングパターンは、異なるプロジェクト間で再利用できる。

- スケーラビリティ:新しい機能は、図全体を再描画することなく、新たなモジュールとして追加できる。

- チームの効率性:異なるチームが、それぞれのタイミング図を同時に作業できる。

モジュール境界の定義

この戦略を効果的に実行するためには、明確な境界を設ける必要がある。各モジュールには明確な入力と出力が存在するべきである。単一モジュールのタイミング図は、その境界を越える信号に注目すべきである。内部の詳細はインターフェースのタイミングに直接影響しない限り、抽象化してもよい。

| モジュールレベル | 注目領域 | 詳細の粒度 |

|---|---|---|

| システムレベル | モジュール間通信 | 高レベルなハンドシェイク |

| ブロックレベル | 内部データパス | 特定の信号依存関係 |

| ゲートレベル | 伝播遅延 | 正確なナノ秒単位のタイミング |

これらのレベルに従って図を整理することで、エンジニアは情報の明確な階層構造を維持できる。この構造により、設計プロセスの適切な段階で適切な詳細レベルが利用可能になることが保証される。

信号状態と遷移の解読 📊

モジュール構造が整えられたら、次に特定の信号を分析する。すべての信号が同じように振る舞うわけではない。一部は連続的であり、他の信号はエッジトリガーである。各信号の性質を理解することは、正確な図の作成にとって不可欠である。

一般的な信号カテゴリには以下が含まれる:

- クロック信号:システムの鼓動。周期的であり、状態変化を駆動する。通常、周波数とデューティサイクルに厳格な要件がある。

- データ信号:実際に転送されている情報。これらはクロックに対して特定の期間内において安定している必要がある。

- 制御信号:機能の有効・無効を制御する信号。たとえば、チップセレクトやイネーブルなど。

- リセット信号:システムを既知の状態に強制する初期化信号。

これらのライン上の遷移は重要である。立ち上がりエッジはしばしば動作をトリガーし、立ち下がりエッジがそれを完了する場合がある。非同期システムでは、これらのエッジ間の関係は予測しにくく、より詳細な分析が必要となる。

伝播遅延の可視化

信号は瞬時に変化しない。物理的な制限が伝播遅延を引き起こす。信号がコンポーネントから出るとき、その信号は配線を通過して次のコンポーネントに到達するまでに時間がかかる。タイミング図はこの遅延を考慮しなければならない。図で信号が時刻Tで変化していると表示されたとしても、受信側はT + Δtまでその変化に気づかない可能性がある。

伝播遅延を無視すると、シミュレーションや実装において重大な誤差が生じる。エンジニアは、パス全体でセットアップ時間およびホールド時間の要件を満たすために、これらの遅延をモデル化しなければならない。

重要なタイミング制約の説明 ⚠️

デジタル設計における失敗の最も一般的な原因はタイミング違反です。これらの違反は、信号が必要な安定性ウィンドウを満たさないときに発生します。この動作を制御する2つの主要な制約は、セットアップ時間とホールド時間です。

セットアップ時間

セットアップ時間は、アクティブなクロックエッジの前にデータが安定している必要がある最小時間です。データが遅れて到着すると、フリップフロップが正しい値をキャプチャできなくなる可能性があります。この制約は、システムの最大動作周波数を決定する上で非常に重要です。クロック周期が伝播遅延とセットアップ時間の合計より短い場合、システムは失敗します。

セットアップ時間に関する重要な考慮事項には以下が含まれます:

- 最悪ケースを特定するには、最長パス解析が必要です。

- プロセス、電圧、温度の変動が遅延に影響します。

- クロックジッターは、利用可能なセットアップウィンドウを削り取る可能性があります。

ホールド時間

ホールド時間は、アクティブなクロックエッジの後にデータが安定したまま維持される必要がある最小時間です。データが早すぎると、フリップフロップが誤った値をキャプチャするか、メタスタビリティ状態に入ってしまう可能性があります。セットアップ時間とは異なり、ホールド時間はクロック周波数に依存しません。これは部品の内部遅延と外部パスに依存します。

ホールド時間違反は、クロックを遅くするだけでは解決できないため、しばしば修正が難しいです。代わりに、データパスに遅延を追加するか、論理回路を再設計する必要があります。

タイミング制約の要約

| 制約 | 定義 | 周波数への影響 | 解決方法 |

|---|---|---|---|

| セットアップ時間 | クロックエッジの前に安定 | 最大周波数を制限 | 論理パスを最適化 |

| ホールド時間 | クロックエッジの後に安定 | 周波数に依存しない | バッファ遅延を追加 |

| 伝播遅延 | 論理を通過する時間 | 両方に影響 | 回路最適化 |

一般的な落とし穴と違反 🚫

モジュールアプローチを採用しても、エラーが入り込むことがあります。一般的な落とし穴を認識することで、設計段階での防止が可能になります。ハードウェア検証では、いくつかの種類の違反が頻繁に見られます。

- メタスタビリティ:信号がクロックエッジちょうどタイミングで変化するときに発生する。フリップフロップの出力は予測不能になる。クロックドメイン間を跨ぐ際によく見られる。

- グリッチ:論理パスの違いによって生じる短い、意図しないパルス。これらは誤った状態変化を引き起こす可能性がある。

- クロックスキュー:クロック信号が異なるコンポーネントに異なるタイミングで到達する状態。これにより、有効なタイミングウィンドウが減少する。

- レースコンディション:結果がイベントの順序に依存する状態。非同期設計では予測不可能である。

これらの問題に対処するには、タイミング図の慎重な分析が必要である。安定性が保証されない重複するウィンドウを確認する。リセットシーケンスが正しく実行されていることを確認し、未定義状態を避ける。

モジュールワークフローの実装 🛠️

この手法を効果的に適用するには、構造化されたワークフローに従う。これにより、タイミングのすべての側面が重複なくカバーされる。

- インターフェースの定義:各モジュールのすべての入力と出力を明確にリストアップする。

- クロックドメインの特定:どの信号がどのクロックドメインに属するかを決定する。

- データパスのマッピング:ソースから宛先までのパスを追跡する。

- 制約の適用:すべてのフリップフロップに対してセットアップ時間およびホールド時間の要件を設定する。

- 遷移の検証:エッジの整合性とパルス幅を確認する。

- 統合のレビュー:モジュール図が結合された際に整合していることを確認する。

各ステップは前のステップに基づいて構築される。ステップを飛ばすとカバレッジの穴が生じる。たとえばクロックドメインを無視すると、後でデバッグが困難な同期失敗が発生する可能性がある。

マルチクロックドメインの処理 🌐

設計が大きくなるにつれて、複数のクロック周波数が必要になる。システムの一部は高速で動作し、他の一部は低速で動作する。これらのドメインを同期することは、タイミング解析において最も困難な側面の一つである。

信号が一つのクロックドメインから別のドメインに渡るとき、タイミング図は二つのクロックの関係を反映しなければならない。クロックが非同期の場合、メタスタビリティを防ぐために特別な配慮が必要である。同期チェーンやハンドシェイクプロトコルなどの技術が、この転送を安全に管理するために用いられる。

マルチクロック設計のための主要な戦略には以下が含まれる:

- グレイ符号化:マルチビットカウンタをドメイン間で安全に伝送するためにグレイコードを使用する。

- FIFOバッファ:読み取りクロックと書き込みクロックを分離するために、先入れ先出しキューを使用する。

- ハンドシェイク信号:リクエスト/アックノリッジペアを使用して、データの有効性を保証する。

これらのシナリオにおけるタイミング図は、両ドメインのクロックエッジを明示的に表示しなければならない。これにより、エンジニアはデータが受信クロックがそれをキャプチャするのに十分な時間安定しているかどうかを確認できる。

視覚データを用いたデバッグ 🔍

設計が失敗した場合、タイミング図を最初に確認すべきである。デバッグには忍耐と体系的なアプローチが必要である。まず、故障したモジュールを特定する。期待される図と実際の波形を比較する。

以下の点に差異がないか確認する:

- クロックに対する信号タイミング。

- 制御信号のパルス幅。

- リセット中の状態遷移。

- データライン上のギャップ。

ツールはしばしばナノ秒レベルの詳細を検査できるズーム機能を提供する。違反が発生する正確な瞬間を確認するためにこれらの機能を使用する。視覚データを論理と照合することで、根本原因を理解できる。

設計の整合性についての最終的な考察 💡

タイミング図は単なる技術図面以上のものである。信頼性の高いデジタルシステムの設計図なのである。モジュール化アプローチを採用することで、エンジニアは複雑さを管理し、明確さを保つことができる。この方法はスケーラビリティを支援し、高コストの誤りの発生可能性を低減する。

ハードウェア設計での成功は細部への注意にかかっている。1ナノ秒も重要である。すべての遷移が意味を持つ。これらの原則を厳密に適用することで、実世界の条件下でも予測可能な動作を示すシステムを構築できる。タイミング解析のモジュール化分解により、どの細部も見逃されず、堅牢で効率的なハードウェアソリューションが得られる。

技術の進歩に伴い、これらのスキルの継続的な洗練が不可欠である。新しい規格や高速化は、更新された解析手法を必要とする。デジタルエンジニアリング分野での競争優位を維持するため、新たなベストプラクティスについて常に情報収集を続けること。