W świecie elektroniki cyfrowej i inżynierii komputerowej sygnały nie istnieją w próżni. Przesuwają się po ścieżkach, przez bramki i w procesory z określonymi ograniczeniami czasowymi. Aby zrozumieć, jak działa system, inżynierowie muszą wizualizować sposób zmian tych sygnałów w czasie. Taka wizualizacja osiągana jest za pomocą diagramu czasowego. Dla początkującego te wykresy mogą wydawać się skomplikowanymi hieroglify, ale są w rzeczywistości najważniejszym narzędziem do debugowania i projektowania logiki cyfrowej.

Ten przewodnik zawiera szczegółowy przegląd diagramów czasowych. Przeanalizujemy budowę sygnału, kluczowe parametry wpływające na niezawodność oraz typowe pułapki prowadzące do awarii systemu. Niezależnie od tego, czy przygotowujesz się do egzaminu, czy projektujesz swój pierwszy obwód mikrokontrolera, zrozumienie tych wykresów jest niezbędne.

🧠 Co to jest diagram czasowy?

Diagram czasowy to graficzne przedstawienie stanu sygnałów cyfrowych w czasie. W przeciwieństwie do schematu elektrycznego, który pokazujecojest połączone zco, diagram czasowy pokazujekiedysię dzieje. Rysuje poziomy napięcia względem osi czasu, umożliwiając inżynierom widzenie kolejności zdarzeń.

Te wykresy są niezastąpione z kilku powodów:

- Debugowanie: Ujawniają warunki wyścigu, gdy sygnały przychodzą w niepoprawnej kolejności.

- Weryfikacja: Potwierdzają, że obwód spełnia wymagane specyfikacje prędkości.

- Dokumentacja: Służą jako odniesienie do sposobu komunikacji między różnymi chipami.

- Projektowanie: Pomagają określić maksymalną częstotliwość taktowania, jaką system może wspierać.

Gdy patrzysz na diagram czasowy, patrzysz na zdjęcie chwilowe zachowania fizycznego elektronów poruszających się przez system. Uchwycił on rzeczywistość opóźnień, propagacji i synchronizacji.

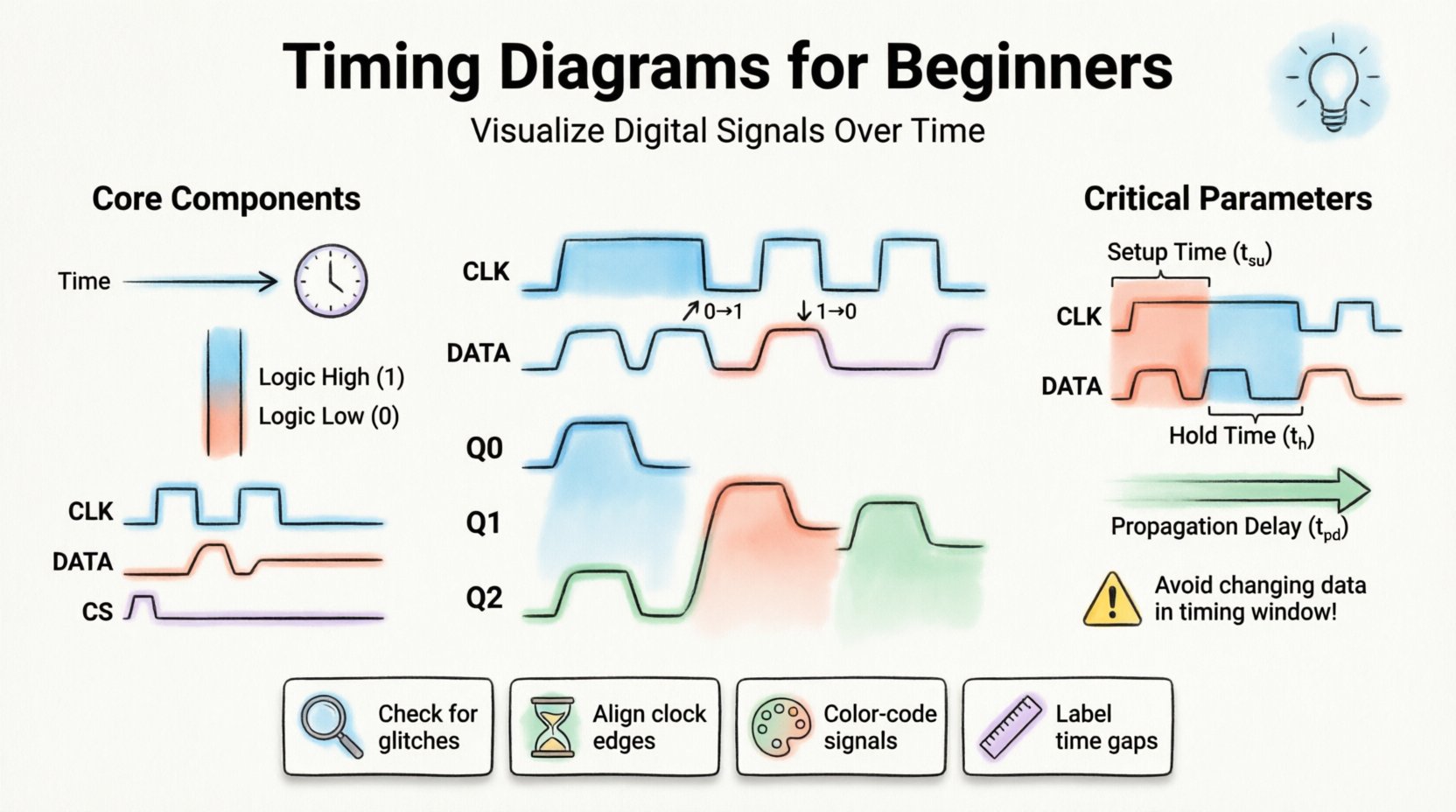

📊 Podstawowe elementy diagramu czasowego

Zanim przeanalizujesz złożone przebiegi, musisz zrozumieć elementy budowlane. Każdy diagram czasowy składa się z kilku podstawowych elementów.

1. Oś czasu

Oś pozioma reprezentuje czas. Przepływa od lewej do prawej. W projektowaniu cyfrowym oś ta często jest podzielona na cykle zegarowe, oznaczone pionowymi liniami siatki. Skala może się zmieniać od nanosekund (ns) dla szybkich procesorów po milisekundy (ms) dla wolniejszej logiki sterującej.

2. Oś poziomu napięcia

Oś pionowa reprezentuje stan logiczny sygnału. W standardowych rodzinach logiki jest to zwykle stan dwustanowy:

- Stan logiczny wysoki (1):Często reprezentowany jako VCC lub 5V.

- Stan logiczny niski (0): Często oznaczane jako Ziemia lub 0V.

- High-Z (Wysokie impedancja): Stan, w którym pin jest efektywnie odłączony, powszechny w systemach szynowych.

3. Linie sygnałowe

Każda pozioma linia reprezentuje określoną przewód lub nazwę sygnału. Te linie są jasno oznaczone (np. CLK, DATA_IN, CS), aby określić, którą część obwodu monitoruje się.

🔄 Odczytywanie przejść sygnału

Ruch linii sygnału w górę i w dół to miejsce, gdzie znajduje się dane. Zrozumienie kierunku tych ruchów jest kluczowe.

⬆️ Krawędź narastająca

Krawędź narastająca występuje, gdy sygnał przechodzi z niskiego na wysokie. W logice binarnej jest to często punkt wyzwalający wiele operacji. Reprezentuje zmianę od 0 do 1.

⬇️ Krawędź spadająca

Krawędź spadająca występuje, gdy sygnał przechodzi z wysokiego na niski. Reprezentuje zmianę od 1 do 0.

⚡ Wyzwalanie po krawędzi

Wiele cyfrowych komponentów, takich jak przerzutniki, reaguje tylko na te krawędzie, a nie na stan stały. Przerzutnik może przechwytywać dane tylko w momencie krawędzi narastającejsygnału zegarowego. Jeśli przegapisz krawędź, dane zostaną utracone.

| Przejście | Kierunek | Zmiana binarna | Powszechny typ wyzwalania |

|---|---|---|---|

| Krawędź narastająca | Niski ➔ Wysoki | 0 ➔ 1 | Wyzwalane po krawędzi dodatniej |

| Krawędź spadająca | Wysoki ➔ Niski | 1 ➔ 0 | Wyzwalane po krawędzi ujemnej |

| Poziom wysoki | Stały poziom wysoki | Stały 1 | Wrażliwy na poziom |

| Poziom niski | Stabilny poziom niski | Stabilny 0 | Wrażliwy na poziom |

⏳ Krytyczne parametry czasowe

Wykresy czasowe to nie tylko obrazy; zawierają pomiary. Przestrzeń między zmianami sygnałów to miejsce, gdzie decyduje się o niezawodności. Trzy konkretne parametry dominują analizę czasową cyfrową.

1. Opóźnienie propagacji (tpd)

Sygnały nie poruszają się natychmiast. Gdy wejście ulega zmianie, upływa skończony czas, zanim wyjście odzwierciedli tę zmianę. To opóźnienie propagacji. Powstaje ono z powodu fizycznej rezystancji i pojemności materiałów.

- Definicja: Różnica czasowa między zmianą wejścia a zmianą wyjścia.

- Wpływ: W łańcuchu bramek logicznych opóźnienia się akumulują. Jeśli opóźnienie jest zbyt duże, sygnał może dotrzeć po rozpoczęciu kolejnego cyklu zegara, co powoduje błędy.

2. Czas ustawienia (tsu)

Czas ustawienia to wymóg, aby sygnał danych był stabilny przed przybyciem krawędzi zegara. Jeśli dane zmieniają się zbyt blisko krawędzi zegara, odbiorcza układ nie może ich poprawnie zarejestrować.

- Zasada: Dane muszą być ważne przez określony czas przed wyzwoleniem zegara.

- Wizualnie: Na wykresie to odstęp między ustabilizowaniem się linii danych a krawędzią zegara.

3. Czas utrzymania (th)

Czas utrzymania to wymóg, aby sygnał danych pozostał stabilny po gdy przychodzi krawędź zegara. Jeśli dane zmieniają się od razu po krawędzi zegara, obwód może nie ustalić poprawnej wartości.

- Zasada:Dane muszą pozostawać niezmienione przez określony czas po uruchomieniu zegara.

- Wizualnie:Na schemacie jest to odstęp między krawędzią zegara a następną zmianą danych.

⚠️ Okno czasowe

Połączenie czasu przygotowania i czasu utrzymania tworzy poprawne okno do przechwytywania danych. Jeśli na diagramie czasowym widać zmianę danych w tym oknie, system jest narażony na awarię.

⚡ Systemy synchroniczne vs. asynchroniczne

Diagramy czasowe znacznie się różnią w zależności od architektury systemu.

Systemy synchroniczne

W projektowaniu synchronicznym wszystkie operacje są koordynowane przez sygnał zegara globalnego. Każda zmiana stanu następuje na krawędzi tego zegara. Diagramy czasowe dla tych systemów wyglądają bardzo regularnie.

- Cechy:Przewidywalne, łatwiejsze do projektowania, ograniczone szybkością zegara.

- Wygląd diagramu:Pionowe linie siatki idealnie pokrywają się ze wszystkimi zmianami sygnałów.

Systemy asynchroniczne

W projektowaniu asynchronicznym nie ma zegara globalnego. Sygnały zmieniają się w momencie zmiany wejść. Oferuje to większe możliwości szybkości, ale znacznie utrudnia analizę czasową.

- Cechy:Szybsza reakcja na wejścia, skomplikowana analiza zagrożeń.

- Wygląd diagramu:Przejścia sygnałów występują w nierównych odstępach czasu. Musisz mierzyć dokładne odstępy czasowe między zdarzeniami.

📝 Jak rysować diagram czasowy

Tworzenie diagramu czasowego to systematyczny proces. Postępuj zgodnie z tymi krokami, aby zarejestrować obwód lub zweryfikować projekt.

- Zidentyfikuj sygnały: Wypisz wszystkie wejścia, wyjścia i wewnętrzne linie sterujące. Oznacz je jasno.

- Ustal podstawę czasową: Zdecyduj o skali czasowej. Dla obwodów logicznych cykle zegara są zwykle jednostką standardową.

- Narysuj zegar: Zawsze najpierw narysuj sygnał zegara. Jest to odniesienie dla wszystkich innych zdarzeń.

- Zmapuj wejścia Narysuj przebiegi sygnałów wejściowych na podstawie operacji logicznej lub sekwencji testowej.

- Oblicz opóźnienia: Przesuń sygnały wyjściowe w prawo na podstawie opóźnienia propagacji bramek zaangażowanych.

- Sprawdź ograniczenia: Upewnij się, że czas ustalania i czas utrzymania są spełnione dla każdego przerzutnika.

- Przejrzyj przejścia: Upewnij się, że nie ma zakłóceń. Zakłócenie to krótki, niechciany impuls, który może niepoprawnie wywołać działanie logiki.

🔄 Przykład z rzeczywistego świata: prosty licznik

Aby zobrazować, jak te pojęcia działają razem, rozważ prosty licznik binarny 3-bitowy. Ten obwód zwiększa swoją wartość za każdym razem, gdy sygnał zegara impulsuje.

Wyobraź sobie trzy linie wyjściowe: Q0, Q1 i Q2. Q0 zmienia stan w każdym cyklu zegara. Q1 zmienia stan za każdym razem, gdy Q0 zakończy pełny cykl. Q2 zmienia stan za każdym razem, gdy Q1 zakończy pełny cykl.

Analiza krok po kroku

- Zegar (CLK): Fala prostokątna o wypełnieniu 50%.

- Q0 (najmłodszy bit): Zmienia stan przy każdym narastającym zboczu zegara. Częstotliwość wynosi połowę częstotliwości zegara.

- Q1: Zmienia stan przy każdym narastającym zboczu Q0. Częstotliwość wynosi połowę częstotliwości Q0.

- Q2 (najstarszy bit): Zmienia stan przy każdym narastającym zboczu Q1. Częstotliwość wynosi połowę częstotliwości Q1.

Podczas rysowania zauważysz efekt rozprzestrzeniania się. Najpierw zmienia się Q0. Q1 czeka, aż Q0 ustali się, zanim zmieni stan. Q2 czeka na Q1. Zgromadzenie tych opóźnień to esencja licznika rozprzestrzeniania się.

| Cykl zegara | Q2 | Q1 | Q0 | Wartość dziesiętna |

|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 1 |

| 3 | 0 | 1 | 0 | 2 |

| 4 | 0 | 1 | 1 | 3 |

| 5 | 1 | 0 | 0 | 4 |

⚠️ Najczęstsze pułapki do uniknięcia

Nawet doświadczeni inżynierowie mogą popełniać błędy przy odczytywaniu wykresów czasowych. Bądź na baczności przed tymi częstymi błędami.

- Ignorowanie zakłóceń:Krótki impuls może nie być widoczny, jeśli skala czasu jest zbyt duża, ale może wywołać zablokowanie. Zawsze sprawdzaj obecność wąskich impulsów.

- Nieprawidłowe rozumienie cyklu roboczego:Zakładanie, że zegar ma 50% cyklu roboczego, podczas gdy jest przesunięty. To wpływa na okno czasowe.

- Ignorowanie stanów High-Z:W systemach szynowych linie są nieprzypisane. Wykres czasowy musi pokazywać, kiedy linia jest aktywna, a kiedy jest nieprzypisana.

- Pomylenie czasu ustalania i czasu utrzymania:Czas ustalania jest przed krawędzią; czas utrzymania po krawędzi. Pomylenie tych pojęć prowadzi do niepoprawnych projektów obwodów.

- Pomijanie odniesienia do masy: Wszystkie poziomy napięcia muszą być mierzone względem tej samej masy. Jeśli masy się różnią, poziomy logiczne są nieprawidłowe.

🛠 Najlepsze praktyki dokumentacji

Podczas tworzenia diagramów czasowych do dokumentacji lub debugowania postępuj zgodnie z tymi wskazówkami, aby zapewnić jasność.

- Używaj spójnego skalowania: Upewnij się, że oś czasu jest liniowa. Nie kompresuj jednej części i nie rozciągaj drugiej, chyba że jest to jasno oznaczone.

- Wyrównaj krytyczne krawędzie: Upewnij się, że krawędź zegara idealnie się pokrywa z punktem próbkowania danych.

- Oznacz przerwy: Jeśli występuje opóźnienie, oznacz je konkretną wartością czasu (np. tpd= 5ns).

- Kodowanie kolorowe: Używaj różnych kolorów dla różnych typów sygnałów (np. niebieski dla zegara, czerwony dla danych, zielony dla sterowania).

- Zaznacz stany aktywne: Jasno wskazuj, czy sygnał jest aktywny wysokim (active High) czy niskim (active Low) (np. używając kreski nad nazwą, jak /CS).

🧩 Metastabilność i zagrożenia czasowe

Zaawansowane diagramy czasowe często ujawniają zjawisko nazywane metastabilnością. Występuje ono wtedy, gdy sygnał zmienia się dokładnie w oknie ustawienia/zachowania (setup/hold) przerzutnika. Wyjście nie ustala się od razu na 0 lub 1; waha się na pośrednim poziomie napięcia.

Choć rzadkość, metastabilność może spowodować awarię systemu. Diagramy czasowe pomagają przewidzieć to zjawisko, pokazując zależność między sygnałami asynchronicznymi a zegarem synchronicznym. Jeśli sygnał zewnętrzny zmienia się zbyt blisko krawędzi zegara, diagram pokaże, że dane przekraczają próg w złym momencie.

🔍 Analiza danych rzeczywistych

Gdy patrzysz na diagram czasowy wygenerowany przez analizator logiczny, linie rzadko są idealnymi kwadratami. Sygnały rzeczywiste mają:

- Czas narastania: Czas potrzebny na przejście od poziomu niskiego do wysokiego. Zazwyczaj nie jest natychmiastowy.

- Czas spadku: Czas potrzebny na przejście od poziomu wysokiego do niskiego.

- Przeciążenie/Przeciążenie dolne: Piki napięcia przekraczające poziomy zasilania.

- Jitter: Zmiany w czasie krawędzi sygnału.

Zrozumienie tych niedoskonałości jest kluczowe dla projektowania układów o wysokiej prędkości. Idealny sygnał prostokątny to pojęcie teoretyczne; rzeczywiste sygnały są falami analogowymi, które reprezentują logikę cyfrową.

📚 Podsumowanie kluczowych wniosków

Diagramy czasowe to język czasowania cyfrowego. Przekładają abstrakcyjną logikę na rzeczywistość fizyczną. Opanowanie ich daje Ci możliwość:

- Wizualizować przepływ danych przez system.

- Określać, gdzie sygnały mogą się ze sobą kolidować.

- Zapewniać wiarygodne przechwytywanie danych.

- Obliczać maksymalną prędkość pracy obwodu.

Zacznij ćwiczyć z prostymi bramkami logicznymi. Narysuj wejście, oblicz opóźnienie i narysuj wyjście. W miarę postępu przechodź do złożonych szyn danych i domen zegarowych. Z cierpliwością i praktyką czytanie tych diagramów stanie się dla Ciebie naturalne.

🚀 Postępowanie dalej

Kontynuuj eksplorację subtelności integralności sygnałów i sieci dystrybucji zegarów. W miarę jak systemy stają się szybsze, zapasy czasowe stają się mniejsze. Umiejętność dokładnego odczytywania diagramów czasowych pozostanie podstawową kompetencją każdego inżyniera pracującego z sprzętem cyfrowym.