W złożonym świecie projektowania sprzętu cyfrowego kluczowe znaczenie ma jasność. Inżynierowie i projektanci opierają się na reprezentacjach wizualnych, aby przekazywać sposób działania sygnałów w czasie. Diagram czasowy stanowi jedno z najważniejszych narzędzi do tego celu. Przekształca abstrakcyjną logikę w wizualny czas, ujawniając taniec stanów wysokich i niskich na różnych elementach. Jednak wraz ze wzrostem złożoności systemów te diagramy mogą stać się przytłaczające. Niniejszy przewodnik omawia podejście modułowe do analizy i rozkładania diagramów czasowych, zapewniając dokładność i wiarygodność w weryfikacji sprzętu.

Zrozumienie przepływu sygnałów danych i sterujących jest kluczowe dla zapobiegania awariom funkcjonalnym. Niezależnie od tego, czy projektujesz interfejs mikrokontrolera, czy protokół komunikacji o wysokiej prędkości, umiejętność odczytywania i tworzenia tych diagramów oddziela solidny projekt od niestabilnego. Przyjęcie strukturalnego, modułowego podejścia pozwala zespołom zarządzać złożonością i zmniejsza ryzyko naruszeń czasowych.

Zrozumienie podstaw diagramów czasowych ⏱️

Diagram czasowy to graficzna reprezentacja zmian stanów sygnałów w czasie. Na osi poziomej oznacza się czas, a na osi pionowej stany sygnałów. Ten format wizualny pozwala inżynierom weryfikować relacje między różnymi sygnałami w obwodzie cyfrowym. Głównym celem jest zapewnienie, że dane są stabilne i poprawne w momencie próbkowania przez odbiorcę.

Kilka kluczowych elementów stanowi podstawę każdego diagramu czasowego:

- Linie sygnałów:Poziome linie reprezentują pojedyncze przewody lub szyny przenoszące określone sygnały, takie jak zegar, dane lub sygnały sterujące.

- Oś czasu:Poziome rozciąganie oznacza upływ czasu, często oznaczony w nanosekundach lub cyklach zegara.

- Poziomy logiczne:Sygnały są zazwyczaj dwustanowe, reprezentowane jako wysoki (1) lub niski (0). Czasem pokazywane są również nieokreślone stany lub stany wysokiej impedancji.

- Przejścia:Linie pionowe wskazują moment przejścia sygnału z jednego stanu do drugiego, takiego jak narastające lub spadające krawędzie.

- Adnotacje:Etykiety tekstowe często określają konkretne ograniczenia, opóźnienia lub bloki funkcjonalne wewnątrz diagramu.

Bez jasnego zrozumienia tych podstaw interpretacja złożonych interakcji staje się trudna. Diagram czasowy to nie tylko rysunek; jest to umowa między nadawcą a odbiorcą. Określa zasady, według których dane muszą się poruszać, aby zostały poprawnie przetworzone.

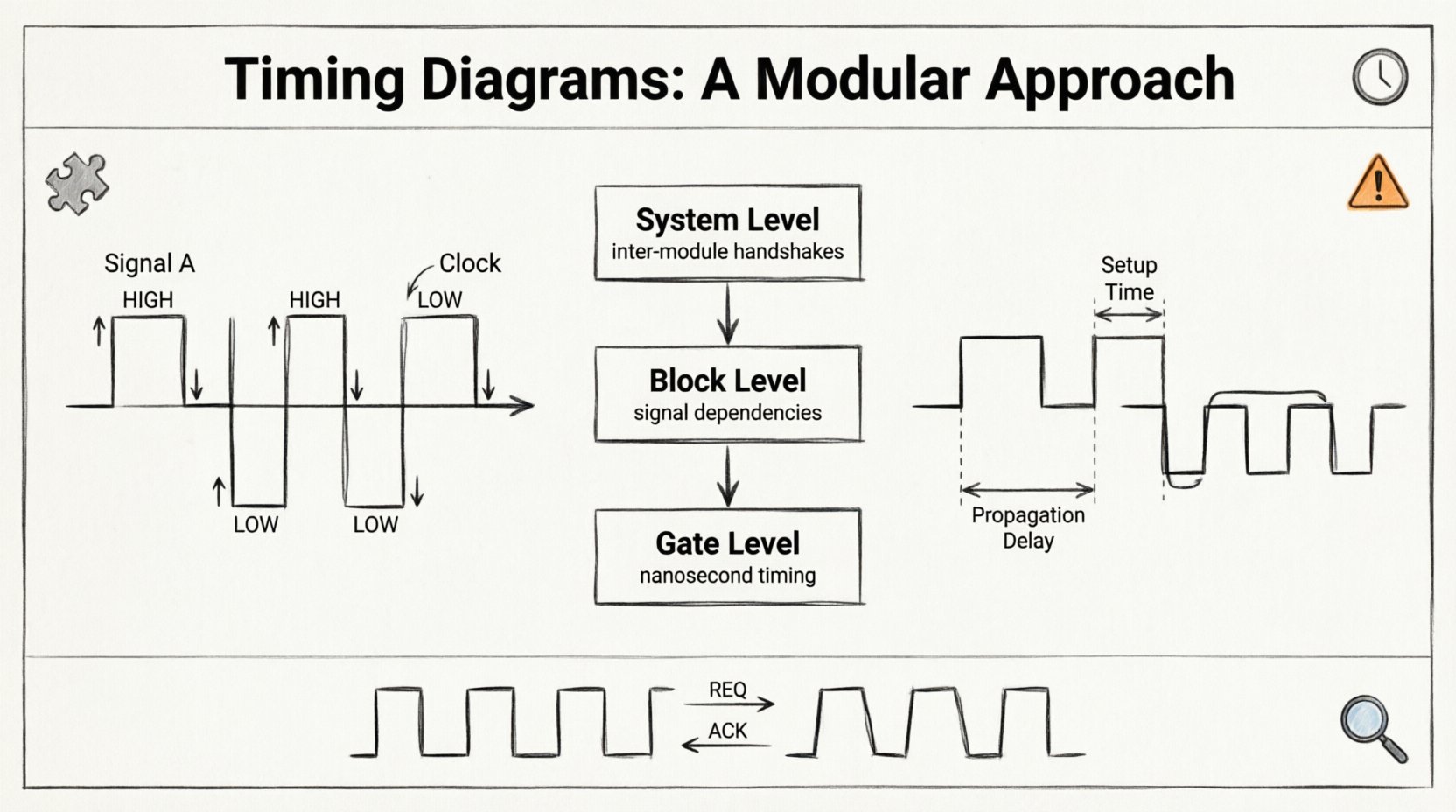

Podejście modułowe do złożonych projektów 🧩

Nowoczesne układy cyfrowe rzadko są proste. Składają się z wielu podsystemów, każdy z własnymi wymogami czasowymi. Próba narysowania całego systemu na jednym diagramie często prowadzi do zamieszania i nieporozumień. Podejście modułowe dzieli projekt na obszary łatwe do zarządzania. Ta metoda poprawia czytelność i upraszcza proces debugowania.

Dlaczego modułowość ma znaczenie

Podział systemu na moduły pozwala projektantom skupić się na konkretnych interfejsach, nie tracąc się w hałasie całej architektury. Gdy występuje naruszenie czasowe, diagram modułowy ułatwia izolację źródła problemu. Zmniejsza obciążenie poznawcze i wspiera współpracę między różnymi zespołami inżynierskimi pracującymi nad oddzielnymi blokami.

Zalety tego podejścia obejmują:

- Izolacja problemów:Problemy można zidentyfikować w konkretnym bloku, a nie w całym systemie.

- Powtarzalność:Standardowe wzorce czasowe dla typowych modułów mogą być wykorzystywane ponownie w różnych projektach.

- Skalowalność:Nowe funkcje mogą być dodawane jako nowe moduły bez konieczności ponownego rysowania całego diagramu.

- Efektywność zespołu:Różne zespoły mogą jednocześnie pracować nad własnymi diagramami czasowymi.

Określanie granic modułów

Aby skutecznie zastosować tę strategię, muszą zostać ustalone jasne granice. Każdy moduł powinien mieć zdefiniowane wejścia i wyjścia. Diagram czasowy pojedynczego modułu powinien skupiać się na sygnałach przechodzących przez tę granicę. Wewnętrzne szczegóły mogą być abstrahowane, chyba że bezpośrednio wpływają na czas przekazywania sygnałów na interfejsie.

| Poziom modułu | Obszar skupienia | Poziom szczegółowości |

|---|---|---|

| Poziom systemu | Komunikacja między modułami | Wysokopoziomowe wymiany potwierdzeń |

| Poziom bloku | Wewnętrzne ścieżki danych | Specyficzne zależności sygnałów |

| Poziom bramki | Opóźnienia propagacji | Dokładne czasowanie w nanosekundach |

Organizując diagramy według tych poziomów, inżynierowie mogą utrzymać jasną hierarchię informacji. Ta struktura zapewnia, że odpowiedni poziom szczegółowości jest dostępny w odpowiednim etapie procesu projektowania.

Dekodowanie stanów i przejść sygnałów 📊

Po ustaleniu struktury modularnej następnym krokiem jest analiza konkretnych sygnałów. Nie wszystkie sygnały zachowują się tak samo. Niektóre są ciągłe, inne są wyzwalane po zboczeniu. Zrozumienie charakteru każdego sygnału jest kluczowe dla poprawnego tworzenia diagramów.

Typowe kategorie sygnałów obejmują:

- Sygnały zegarowe: Puls systemu. Są one okresowe i wywołują zmiany stanów. Zazwyczaj mają ścisłe wymagania dotyczące częstotliwości i cyklu roboczego.

- Sygnały danych: Prawdziwa informacja przesyłana przez system. Muszą one być stabilne w określonych oknach czasowych względem zegara.

- Sygnały sterujące: Sygnały umożliwiające lub wyłączające funkcjonalność, takie jak Chip Select lub Enable.

- Sygnały resetu: Sygnały inicjalizacji, które zmuszają system do przejścia do znanego stanu.

Przejścia na tych liniach są kluczowe. Wzrost poziomu często wywołuje działanie, podczas gdy spadek może je zakończyć. W systemach asynchronicznych relacja między tymi zboczeniami jest mniej przewidywalna, co wymaga bardziej szczegółowej analizy.

Wizualizacja opóźnienia propagacji

Żaden sygnał nie zmienia się natychmiast. Ograniczenia fizyczne powodują opóźnienie propagacji. Gdy sygnał opuszcza komponent, upływa czas, by przejść przez przewód i dotrzeć do następnego komponentu. Diagramy czasowe muszą uwzględniać tę opóźnienie. Jeśli diagram pokazuje zmianę sygnału w czasie T, odbiorca może go zobaczyć dopiero w T + Δt.

Ignorowanie opóźnienia propagacji może prowadzić do istotnych błędów w symulacji i implementacji. Inżynierowie muszą modelować te opóźnienia, aby zapewnić spełnienie czasów ustalania i utrzymywania na całym odcinku.

Krytyczne ograniczenia czasowe wyjaśnione ⚠️

Najczęstszy powód awarii w projektowaniu cyfrowym to naruszenie warunków czasowych. Takie naruszenia występują, gdy sygnały nie spełniają wymaganych okien stabilności. Dwa podstawowe ograniczenia regulują to zachowanie: czas ustawienia i czas utrzymania.

Czas ustawienia

Czas ustawienia to minimalny czas, przez który dane muszą być stabilne przed aktywnym zboczem zegara. Jeśli dane przyjdą zbyt późno, przerzutnik może nie zarejestrować poprawnej wartości. To ograniczenie ma kluczowe znaczenie przy określaniu maksymalnej częstotliwości pracy układu. Jeśli okres zegara jest krótszy niż opóźnienie propagacji plus czas ustawienia, układ nie zadziała.

Kluczowe aspekty dotyczące czasu ustawienia to:

- Wymagana jest analiza najdłuższej drogi, aby znaleźć najgorszy przypadek.

- Wahania procesu, napięcia i temperatury wpływają na opóźnienie.

- Zaszumienie zegara może zmniejszać dostępne okno czasu ustawienia.

Czas utrzymania

Czas utrzymania to minimalny czas, przez który dane muszą pozostać stabilne po aktywnym zboczu zegara. Jeśli dane zmienią się zbyt szybko, przerzutnik może zarejestrować niepoprawną wartość lub wejść w stan metastabilny. W przeciwieństwie do czasu ustawienia, czas utrzymania jest niezależny od częstotliwości zegara. Zależy od opóźnienia wewnętrznych komponentów oraz drogi zewnętrznej.

Naruszenia czasu utrzymania są często trudniejsze do naprawienia, ponieważ nie mogą być rozwiązane przez spowolnienie zegara. Zamiast tego wymagają dodania opóźnienia do drogi danych lub ponownego zaprojektowania logiki.

Podsumowanie ograniczeń czasowych

| Ograniczenie | Definicja | Wpływ na częstotliwość | Metoda rozwiązania |

|---|---|---|---|

| Czas ustawienia | Stabilne przed zboczem zegara | Ogranicza maksymalną częstotliwość | Optymalizuj drogę logiczną |

| Czas utrzymania | Stabilne po zboczem zegara | Niezależne od częstotliwości | Dodaj opóźnienie bufora |

| Opóźnienie propagacji | Czas potrzebny na przejście przez logikę | Wpływ na oba | Optymalizacja obwodu |

Powszechne pułapki i naruszenia 🚫

Nawet przy podejściu modularnym błędy mogą się pojawić. Rozpoznawanie powszechnych pułapek pomaga uniknąć ich w fazie projektowania. Weryfikacja sprzętu często napotyka na kilka rodzajów naruszeń.

- Metastabilność: Występuje, gdy sygnał zmienia się dokładnie w chwili krawędzi zegara. Wyjście przerzutnika staje się nieprzewidywalne. Jest to częste przy przekraczaniu domen zegarowych.

- Zakłócenia: Krótkie, niechciane impulsy spowodowane różnicami w ścieżkach logiki. Mogą one wywołać fałszywe zmiany stanu.

- Zeskok zegara: Gdy sygnał zegara dociera do różnych komponentów w różnych momentach. Zmniejsza to skuteczny okno czasowe.

- Warunki wyścigu: Gdy wynik zależy od kolejności zdarzeń, co jest nieprzewidywalne w projektach asynchronicznych.

Radzenie sobie z tymi problemami wymaga dokładnej analizy diagramu czasowego. Szukaj nakładających się okien, w których nie ma gwarancji stabilności. Upewnij się, że sekwencje resetowania są poprawnie przestrzegane, aby uniknąć nieokreślonych stanów.

Wdrażanie zmodularizowanego przepływu pracy 🛠️

Aby skutecznie zastosować tę metodologię, postępuj zgodnie z zorganizowanym przepływem pracy. Zapewnia to, że każdy aspekt czasowy jest objęty bez nadmiarowości.

- Zdefiniuj interfejsy: Jawnie wymień wszystkie wejścia i wyjścia dla każdego modułu.

- Zidentyfikuj domeny zegarowe: Określ, do której domeny zegarowej należy każdy sygnał.

- Zmapuj ścieżki danych: Prześledź ścieżkę od źródła do docelowego punktu.

- Zastosuj ograniczenia: Ustaw wymagania dotyczące czasu ustalania i utrzymywania dla każdego przerzutnika.

- Weryfikuj przejścia: Sprawdź dopasowanie krawędzi i szerokość impulsów.

- Przegląd integracji: Upewnij się, że diagramy modułów są zgodne po połączeniu.

Każdy krok opiera się na poprzednim. Pominięcie kroku może prowadzić do luk w pokryciu. Na przykład ignorowanie domen zegarowych może spowodować błędy synchronizacji, które są trudne do zdiagnozowania później.

Obsługa wielu domen zegarowych 🌐

Wraz z rozwojem projektów pojawia się potrzeba wielu częstotliwości zegarowych. Niektóre części systemu działają szybko, inne wolno. Synchronizacja tych domen jest jednym z najtrudniejszych aspektów analizy czasowej.

Gdy sygnały przechodzą z jednej domeny zegarowej do drugiej, diagram czasowy musi odzwierciedlać relację między tymi dwoma zegarami. Jeśli zegary są asynchroniczne, konieczna jest szczególna ostrożność, aby zapobiec metastabilności. Do bezpiecznego zarządzania tym przekazem stosuje się techniki takie jak łańcuchy synchronizujące lub protokoły wymiany sygnałów.

Kluczowe strategie projektowania z wieloma domenami zegarowymi obejmują:

- Kod Gray’a: Używanie kodów Gray’a do bezpiecznego przesyłania wielobitowych liczników między domenami.

- Bufory FIFO: Używanie kolejek First-In-First-Out do rozdzielenia zegarów odczytu i zapisu.

- Sygnały potwierdzenia: Używanie par żądanie/potwierdzenie w celu zapewnienia poprawności danych.

Diagramy czasowe dla tych scenariuszy muszą jasno pokazywać krawędzie zegarów obu domen. Pozwala to inżynierom sprawdzić, czy dane pozostają stabilne wystarczająco długo, aby zegar odbiorczy mógł je przechwycić.

Debugowanie przy użyciu danych wizualnych 🔍

Gdy projekt zawiedzie, pierwszym miejscem do sprawdzenia są diagramy czasowe. Debugowanie wymaga cierpliwości i systematycznego podejścia. Zacznij od izolacji modułu, który nie działa. Porównaj oczekiwany diagram z rzeczywistym przebiegiem sygnału.

Szukaj rozbieżności w:

- Czas trwania sygnału względem zegara.

- Szerokość impulsu sygnałów sterujących.

- Przejścia stanów podczas resetu.

- Zakłócenia na liniach danych.

Narzędzia często zapewniają możliwość powiększania, aby zbadać szczegóły na poziomie nanosekund. Używaj tych funkcji, aby zweryfikować dokładny moment naruszenia. Skoreluj dane wizualne z logiką, aby zrozumieć przyczynę pierwotną.

Ostateczne rozważania na temat integralności projektu 💡

Diagramy czasowe to więcej niż tylko rysunki techniczne; są one projektami dla niezawodnych systemów cyfrowych. Przyjmując podejście modularne, inżynierowie mogą zarządzać złożonością i utrzymywać przejrzystość. Ten sposób wspiera skalowalność i zmniejsza prawdopodobieństwo kosztownych błędów.

Sukces w projektowaniu sprzętu zależy od dokładności. Każda nanosekunda ma znaczenie. Każde przejście ma znaczenie. Stosując te zasady z należytą starannością, zespoły mogą tworzyć systemy działające przewidywalnie w warunkach rzeczywistych. Modularne podzielenie analizy czasowej zapewnia, że żaden szczegół nie zostanie pominięty, prowadząc do wytrzymały i efektywnych rozwiązań sprzętowych.

Nieustanne doskonalenie tych umiejętności jest konieczne wraz z postępem technologii. Nowe standardy i większe szybkości wymagają uaktualnionych technik analizy. Bądź na bieżąco z nowymi najlepszymi praktykami, aby utrzymać przewagę konkurencyjną w dziedzinie inżynierii cyfrowej.