W elektronice cyfrowej i inżynierii komputerowej zrozumienie relacji czasowej między sygnałami jest podstawą dla niezawodności systemu. Diagram czasowy pełni rolę podstawowego języka wizualnego opisującego te relacje. Przyporządkowuje stany sygnałów do osi czasu, umożliwiając inżynierom wizualizację przepływu danych, synchronizacji zegara oraz potencjalnych zagrożeń w obwodzie. Niniejszy przewodnik omawia elementy strukturalne, wzorce działania oraz kluczowe scenariusze występujące w analizie przebiegów sygnałów.

Niezależnie od projektowania układów scalonych czy debugowania systemów wbudowanych, umiejętność interpretowania oraz tworzenia dokładnych reprezentacji czasowych jest podstawową kompetencją. Niniejszy dokument zawiera przegląd techniczny interakcji sygnałów, ograniczeń, które muszą być spełnione, oraz typowych pułapek napotykanych podczas weryfikacji.

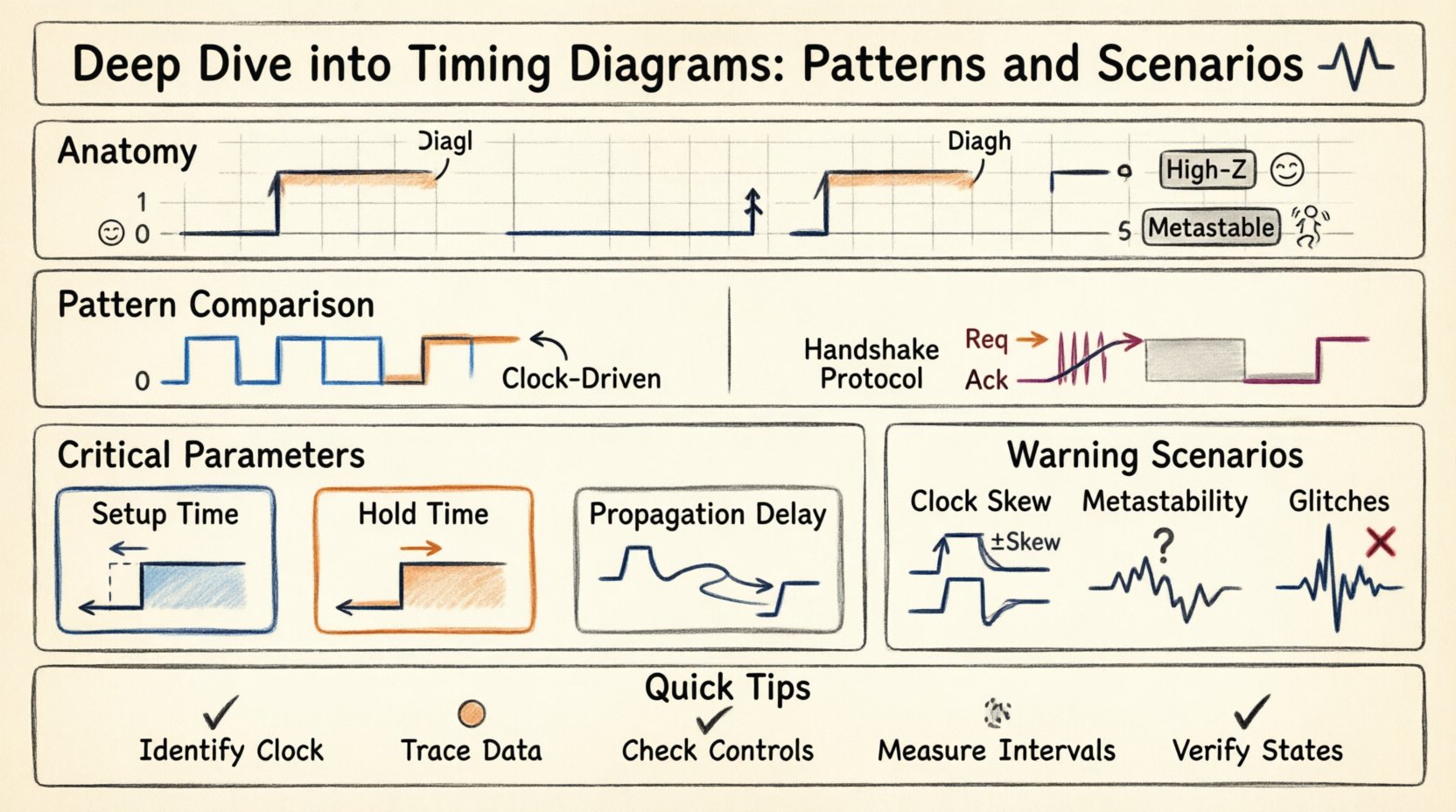

📐 Anatomia diagramu czasowego

Diagram czasowy to reprezentacja graficzna, w której oś pozioma oznacza czas, a oś pionowa poziomy sygnałów. Każdy poziomy odcinek odpowiada konkretnemu sygnałowi lub sieci w projekcie. Zrozumienie składników jest pierwszym krokiem w kierunku dokładnej analizy.

- Oś czasu: Zazwyczaj biegnie poziomo od lewej do prawej. Może być liniowa lub logarytmiczna, w zależności od skali zjawisk obserwowanych.

- Linie sygnałów: Oddzielne ślady reprezentujące poziomy napięcia. Wysokie napięcie zwykle oznacza stan logiczny 1, a niskie napięcie stan logiczny 0.

- Przejścia: Pionowe linie wskazujące zmianę stanu, taką jak zboczenie narastające (0 do 1) lub zboczenie spadające (1 do 0).

- Etykiety: Adnotacje tekstowe identyfikujące konkretne sygnały, wyprowadzenia lub linie sterujące.

- Znaczniki: Pionowe linie przerywane często używane do oznaczenia konkretnych zdarzeń, takich jak impuls zegara lub sygnał resetu.

🔢 Poziomy i stany logiczne

Sygnały cyfrowe nie zawsze istnieją ściśle na poziomie 0 lub 1. W praktyce sygnały mogą znajdować się w nieokreślonych stanach lub stanach wysokiego oporu. Pełny diagram powinien uwzględniać te różnice.

- Stan logiczny wysoki (1): Sygnał jest podawany na poziom napięcia uznawanego za wartość logiczną prawdziwą.

- Stan logiczny niski (0): Sygnał jest podawany na poziom napięcia uznawanego za wartość logiczną fałszywą.

- High-Z: Sygnał jest odłączony od źródła, efektywnie „płynie”. Jest to typowe w buforach trójstanowych.

- Metastabilny: Stan, w którym sygnał nie jest ani wysoki, ani niski, często występujący podczas przejść asynchronicznych.

⚙️ Powszechnie występujące wzorce czasowe

Projekty wykazują przewidywalne wzorce zapewniające integralność danych. Te wzorce określają sposób przemieszczania się danych względem sygnałów sterujących. Rozpoznawanie tych wzorców pomaga w weryfikacji, czy projekt spełnia swoje specyfikacje.

📌 Przesyłanie danych synchroniczne

Projekty synchroniczne opierają się na ogólnym sygnale zegarowym do koordynacji działań. Dane są próbkowane wyłącznie w określonych momentach, zazwyczaj w chwili zboczenia narastającego lub spadającego zegara.

- Sterowane zegarem: Wszystkie zmiany stanu występują w stosunku do krawędzi zegara.

- Poprawność danych: Dane muszą być stabilne przed krawędzią zegara i pozostawać stabilne po niej.

- Rozprzestrzenianie: Miedzy krawędzią zegara a zmianą wyjścia występuje opóźnienie.

📌 Asynchroniczne potwierdzanie

Komunikacja asynchroniczna nie opiera się na wspólnym zegarze. Zamiast tego używa sygnałów sterujących, aby wskazać, kiedy dane są gotowe, a kiedy zostały odbrane.

- Prośba (Req): Nadawca sygnalizuje, że dane są dostępne.

- Potwierdzenie (Ack): Odbiorca sygnalizuje, że dane zostały zaakceptowane.

- Stany oczekiwania: Nadawca może zatrzymać się, aż odbiorca będzie gotowy.

| Cecha | Wzorzec synchroniczny | Wzorzec asynchroniczny |

|---|---|---|

| Współpraca | Globalny sygnał zegara | Sygnały potwierdzenia sterowania |

| Prędkość | Zazwyczaj wyższa | Zmienne, zależne od odpowiedzi |

| Złożoność | Sieć dystrybucji zegara | Logika protokołu |

| Opóźnienie | Przewidywalne | Zmienne |

⏱️ Kluczowe parametry czasowe

Poza wizualnymi liniami, konkretne ograniczenia liczbowe określają, czy obwód będzie działał poprawnie. Te parametry są kluczowe dla analizy czasowej statycznej i muszą zostać zweryfikowane pod kątem ograniczeń fizycznych.

🛑 Czas ustalenia

Czas ustalenia to minimalny czas, przez który sygnał danych powinien być utrzymywany w stanie stabilnym przed krawędzią zegara. Jeśli dane zmieniają się zbyt blisko krawędzi zegara, przechwytywany rejestry może nie przechwycić poprawnej wartości.

- Pomiar:Mierzony od aktywnej krawędzi zegara wstecz w czasie.

- Ryzyko:Naruszenie prowadzi do niepoprawnego przechwytywania danych.

- Wymóg:Opóźnienie ścieżki danych musi być wystarczająco duże, aby spełnić okno ustalenia.

🛑 Czas utrzymania

Czas utrzymania to minimalny czas, przez który sygnał danych powinien być utrzymywany w stanie stabilnym po krawędzi zegara. Zapewnia to, że zatrzask ma wystarczająco dużo czasu, aby zablokować wartość wejściową.

- Pomiar:Mierzony od aktywnej krawędzi zegara do przodu w czasie.

- Ryzyko:Naruszenie prowadzi do metastabilności lub przechwycenia niepoprawnych danych.

- Wymóg:Opóźnienie ścieżki danych musi być wystarczająco małe, aby umożliwić okno utrzymania.

⚡ Opóźnienie propagacji

Jest to czas potrzebny sygnałowi na przejście od wejścia bramki logicznej do jej wyjścia. Wartość ta zależy od pojemności obciążenia oraz rezystancji wewnętrznej tranzystora.

- tpd (z wysokiego na niski): Czas przejścia z 1 na 0.

- tpd (z niskiego na wysoki): Czas przejścia z 0 na 1.

- Zniekształcenie: Różnice w opóźnieniu między równoległymi ścieżkami.

🚨 Krytyczne scenariusze czasowe

Pewne sytuacje stawiają przed nami istotne wyzwania wymagające dokładnej analizy. Te sytuacje często dotyczą wzajemnych oddziaływań między różnymi domenami zegarowymi lub fizycznych ograniczeń sprzętu.

🔄 Zegar przesunięcia

Przesunięcie zegara występuje, gdy sygnał zegara dociera do różnych komponentów w różnych momentach. Może to być spowodowane różnicami w trasowaniu lub odległością fizyczną.

- Przesunięcie dodatnie: Sygnał zegara docelowy przychodzi później niż sygnał zegara źródłowego.

- Przesunięcie ujemne: Sygnał zegara docelowy przychodzi wcześniej niż sygnał zegara źródłowego.

- Skutki: Może skutecznie zmniejszyć marginesy czasu ustawienia lub zwiększyć naruszenia czasu utrzymania.

🌊 Metastabilność

Metastabilność to stan, w którym wyjście przerzutnika nie jest ani wysokie, ani niskie. Zazwyczaj występuje, gdy naruszono czas ustawienia lub czas utrzymania, szczególnie w przekroczeniach asynchronicznych.

- Rozwiązanie: Obwód w końcu osiąga stan stabilny, ale czas potrzebny na to jest nieprzewidywalny.

- Rozwiązanie: Użyj synchronizatorów (przerzutników wielostopniowych), aby zmniejszyć prawdopodobieństwo awarii.

- MTBF: Średni czas między awariami obliczany jest na podstawie szybkości rozwiązywania metastabilności.

📉 Zaburzenia

Zaburzenia to krótkotrwałe szczyty w sygnale, które mogą zostać pomyłkowo uznane za poprawne przejścia. Zazwyczaj pojawiają się z powodu różnic w opóźnieniach propagacji w różnych ścieżkach.

- Przyczyny:Różne długości ścieżek lub warunki wyścigu.

- Skutki: Mogą wywołać niechciane zmiany stanu w logice dolnego poziomu.

- Zmniejszenie skutków: Użyj logiki filtrującej lub upewnij się, że zakończono poprawnie czasowanie.

🔍 Analiza przebiegów

Podczas przeglądu diagramu czasowego systematyczny podejście zapewnia, że żaden szczegół nie zostanie pominięty. Inżynierowie muszą śledzić przepływ sygnałów danych i sterujących, aby wykryć rozbieżności.

🔍 Analiza krok po kroku

- Zidentyfikuj zegar: Znajdź główny sygnał zegara. Ustal, czy jest aktywowy po zboczu narastającym czy spadającym.

- Śledź ścieżki danych:Śledź linie danych od źródła do miejsca docelowego.

- Sprawdź sygnały sterujące:Upewnij się, że sygnały włączania, resetowania i czyszczenia są poprawnie aktywne.

- Mierz przedziały czasu:Oblicz czas między określonymi zdarzeniami, aby zweryfikować wymagania dotyczące czasu ustalania i utrzymywania.

- Zweryfikuj przejścia stanów:Upewnij się, że stan wyjściowy odpowiada oczekiwanej funkcji logicznej.

🔍 Odczytywanie wyzwalaczy zboczy

Zrozumienie, jak komponent reaguje na zbocza sygnałów, jest kluczowe.

- Wyzwalanie po zboczu dodatnim:Działanie następuje w momencie przejścia od niskiego do wysokiego poziomu.

- Wyzwalanie po zboczu ujemnym:Działanie następuje w momencie przejścia od wysokiego do niskiego poziomu.

- Wyzwalanie po poziomie:Działanie następuje tak długo, jak sygnał pozostaje na określonym poziomie.

🛠️ Standardy dokumentacji

Jasna dokumentacja zapewnia, że projekty będą zrozumiałe dla inżynierów. Spójność w oznaczeniach i etykietach zapobiega nieporozumieniom podczas debugowania lub przekazywania projektu.

📝 Zasady oznaczania

- Nazwy sygnałów:Używaj spójnych zasad nadawania nazw (np.

clk,rst_n,data_in). - Polarity:Jasno zaznacz sygnały aktywne na niskim poziomie, często za pomocą kreski nad literą lub sufiksu.

- Jednostki:Jasno podaj jednostki czasu (ns, µs, ms) na osi czasu.

- Skalowanie: Upewnij się, że skala czasu jest odpowiednia dla wyświetlanych zdarzeń.

📝 Czytelność wizualna

- Odstępy: Unikaj nakładania się linii, jeśli to możliwe.

- Kontrast: Używaj różnych kolorów lub grubości linii dla różnych typów sygnałów.

- Adnotacje: Dodaj notatki wyjaśniające złożone zachowania lub konkretne ograniczenia.

- Siatka: Użyj tła siatki, aby ułatwić pomiar przedziałów czasowych.

🚧 Przepływ rozwiązywania problemów

Gdy projekt nie spełnia wymagań czasowych, systematyczny proces rozwiązywania problemów pomaga wyizolować przyczynę. Obejmuje to analizę diagramu pod kątem ograniczeń fizycznych.

🚧 Identyfikacja naruszeń

- Sprawdź czas ustalania: Czy dane przychodzą zbyt późno w stosunku do sygnału zegarowego?

- Sprawdź czas utrzymania: Czy dane zmieniają się zbyt szybko po sygnale zegarowym?

- Sprawdź częstotliwość zegara: Czy okres zegara jest krótszy niż wymagana minimalna wartość?

🚧 Strategie zmniejszania ryzyka

- Rejestry pipeline: Wstaw dodatkowe rejestry, aby rozbić długie ścieżki kombinacyjne.

- Zarządzanie zegarem (clock gating): Zmniejsz aktywność, aby zmniejszyć zużycie mocy i potencjalnie poprawić czas działania.

- Wstawianie buforów: Dodaj buforów, aby wyrównać opóźnienia na równoległych ścieżkach.

- Ograniczenia czasowe: Zdefiniuj fałszywe ścieżki, aby wykluczyć logikę, która nie wpływa na przepływ danych.

📈 Najlepsze praktyki projektowania

Przyjęcie najlepszych praktyk w fazie projektowania zmniejsza prawdopodobieństwo problemów z czasem w późniejszych etapach cyklu rozwoju. Proaktywne planowanie jest bardziej efektywne niż reaktywne naprawianie.

- Znormalizuj interfejsy:Używaj znanych protokołów przesyłania danych, aby uprościć weryfikację czasową.

- Minimalizuj ścieżki asynchroniczne:Utrzymuj interakcje asynchroniczne na minimum, aby zmniejszyć ryzyko metastabilności.

- Dokumentuj założenia:Jasno podaj częstotliwości zegarów i poziomy napięć w specyfikacji projektu.

- Regularnie przeprowadzaj przeglądy:Przeprowadzaj przeglądy czasowe na każdym kluczowym etapie projektu.

🎯 Podsumowanie kluczowych koncepcji

Diagramy czasowe to istotne narzędzia do wizualizacji zachowania czasowego układów cyfrowych. Pokazują, jak sygnały danych i sterujące oddziałują na siebie w czasie, wyróżniając kluczowe ograniczenia, takie jak czasy ustalania i utrzymywania. Zrozumienie struktury tych diagramów pozwala inżynierom identyfikować wzorce, przewidywać błędy i zapewniać niezawodną wydajność systemu.

Kluczowe wnioski obejmują różnicę między wzorcami synchronicznymi i asynchronicznymi, znaczenie zarządzania przesunięciem zegara oraz konieczność jasnych standardów dokumentacji. Przestrzeganie tych zasad ułatwia niezawodny projekt i upraszcza proces weryfikacji.

Ciągła analiza danych przebiegów zapewnia, że projekty pozostają w granicach dopuszczalnych. Wraz z postępem technologii i wzrostem częstotliwości zegarów, precyzja wymagana w analizie czasowej staje się jeszcze bardziej krytyczna. Opanowanie tych koncepcji pozwala tworzyć stabilne, wysokiej wydajności architektury cyfrowe.