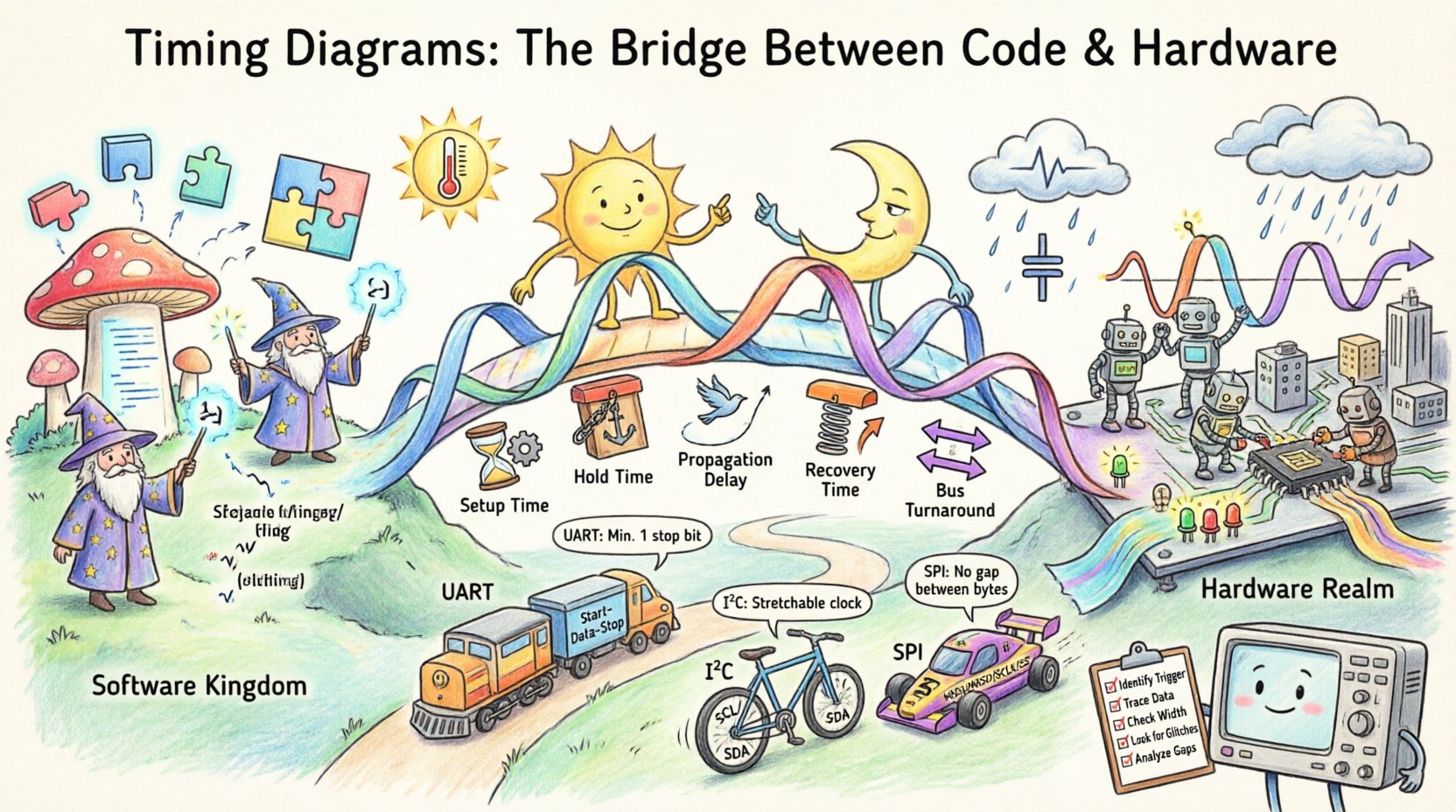

Kiedy inżynierowie oprogramowania piszą kod, myślą w kategoriach instrukcji, zmiennych i przepływów logicznych. Kiedy inżynierowie sprzętu projektują obwody, myślą w kategoriach poziomów napięcia, opóźnień propagacji i cykli zegara. Te dwa światy często istnieją w stanie napięcia. Kod oczekuje, że sygnał dotrze w określonym momencie logicznym, ale sprzęt działa w czasie fizycznym, który podlega zakłóceniom, temperaturze i oporowi elektrycznemu. Mostem między tymi dwoma dziedzinami jest diagram czasowy.

Diagram czasowy to nie tylko obrazek; to umowa. Określa dokładną relację między zdarzeniami w czasie. Informuje firmware, kiedy jest bezpiecznie odczytać pin, i mówi półprzewodnikowi, kiedy jest bezpiecznie prowadzić linię. Bez jasnego zrozumienia tych diagramów systemy wbudowane zawodzą nieprzewidywalnie. Zanieczyszczenie danych, warunki wyścigu i zawieszenia systemu stają się powszechnymi problemami. Ten przewodnik bada mechanikę diagramów czasowych, fizykę ich działania oraz sposób czytania i tworzenia ich skutecznie.

📊 Anatomia sygnału

W esencji logika cyfrowa opiera się na stanach binarnych. W świecie fizycznym te stany są jednak reprezentowane poziomami napięcia. Stan „Wysoki” może wynosić 3,3 wolta, a stan „Niski” 0 woltów. Jednak sygnały nie zmieniają się natychmiast. Podnoszą się i opadają w skończonym czasie. Diagram czasowy wizualizuje ten przejście.

Zrozumienie języka wizualnego tych diagramów to pierwszy krok ku opanowaniu. Kluczowe elementy obejmują:

- Oś czasu:Zazwyczaj pozioma, poruszająca się od lewej do prawej. Może być liniowa lub logarytmiczna, choć liniowa jest standardem dla większości analiz logiki.

- Linie sygnałów:Pionowe linie reprezentujące konkretne przewody, wyprowadzenia lub węzły wewnętrzne.

- Przejścia:Ruch od stanu Niskiego do Wysokiego (krawędź narastająca) lub od Wysokiego do Niskiego (krawędź spadająca). Te krawędzie często wywołują zmiany stanu w logice sekwencyjnej.

- Poziomy:Stabilny stan sygnału przed lub po przejściu.

- Etykiety:Tekstowe adnotacje wyjaśniające znaczenie konkretnego impulsu lub przedziału czasowego.

Rozważmy prosty sygnał zegara. Oscyluje między stanem Wysoki a Niski. Czas potrzebny na ukończenie jednego pełnego cyklu to okres. Odwrotność okresu to częstotliwość. W diagramie czasowym zegar działa jak bicie serca systemu. Każdy inny sygnał jest często synchronizowany z tymi krawędziami.

🕰️ Obszar zegara

Większość systemów cyfrowych działa w obszarze zegara. Jest to grupa obwodów dzielących ten sam odniesienie czasowe. Jednak sygnały często przechodzą między różnymi obszarami. To wprowadza złożoność. Sygnał wygenerowany w szybkim obszarze może dotrzeć zbyt późno do wolnego obszaru, albo zbyt wcześnie, powodując naruszenie warunku utrzymania.

Podczas analizy czasu należy wziąć pod uwagę:

- Zachodzenie zegara (clock skew):Różnica w czasie przybycia sygnału zegara do różnych komponentów. Jeśli zegar dotrze do nadawcy wcześniej niż do odbiorcy, zapasy czasowe się zmniejszają.

- Przesunięcie fazowe:W niektórych systemach sygnały nie są zgodne z krawędzią zegara, ale występują w środku cyklu.

- Drganie (jitter):Wahania w czasie sygnału. Drganie może być losowe lub deterministyczne. Zmniejsza margines szumu i sprawia, że diagram jest mniej przewidywalny.

Kod napisany do interfejsu z hardware’em zakłada stabilny zegar. Jeśli fizyczny zegar ucieka z powodu zmian temperatury lub napięcia, diagram czasowy już nie odpowiada rzeczywistości. Dlatego diagramy czasowe muszą zawierać pasma tolerancji lub scenariusze najgorszych przypadków.

⚙️ Kluczowe parametry czasowe

Pewne parametry określają granice integralności sygnału. Te wartości często znajdują się w dokumentacji technicznej, ale najlepiej je zrozumieć w kontekście diagramu czasowego. Poniższa tabela przedstawia najważniejsze parametry, które inżynierowie muszą ocenić.

| Parametr | Definicja | Wpływ na system |

|---|---|---|

| Czas ustawienia | Minimalny czas, przez który dane muszą być stabilneprzed krawędzi zegara. | W przypadku naruszenia, przechwytywany rejesterek nie może przechwycić poprawnej wartości. |

| Czas utrzymania | Minimalny czas, przez który dane muszą pozostawać stabilnepo krawędzi zegara. | W przypadku naruszenia, rejesterek może wejść w stan metastabilny. |

| Opóźnienie propagacji | Czas potrzebny sygnałowi na przejście od wejścia do wyjścia. | Opóźnienia gromadzą się przez bramki logiczne, co może prowadzić do pominięcia cykli zegara. |

| Czas odzyskania | Czas potrzebny sygnałowi sterującemu, aby wrócić do stanu normalnego po zdarzeniu asynchronicznym. | Wpływ na szybkość odzyskania systemu po zresetowaniu lub przerwaniu. |

| Czas przełączenia magistrali | Czas potrzebny do przełączenia magistrali z trybu wyjściowego na tryb wejściowy. | Kluczowe dla magistral dwukierunkowych, takich jak I2C lub 1-Wire. |

Naruszenie tych parametrów nie zawsze powoduje natychmiastowy awarię. Czasem system działa 99% czasu i zawodzi tylko w określonych warunkach. Dlatego analiza czasowa jest procesem iteracyjnym. Musisz zweryfikować, czy schemat pozostaje poprawny w warunkach najgorszych napięć i temperatur.

👀 Odczytywanie przebiegu

Odczytywanie diagramu czasowego wymaga systematycznego podejścia. Podczas debugowania problemu sprzętowego nie patrz tylko na poziomy sygnałów. Patrz na relacje między sygnałami.

Postępuj zgodnie z poniższymi krokami, aby przeanalizować przebieg:

- Zidentyfikuj wyzwalacz: Znajdź zdarzenie, które rozpoczyna sekwencję. Zazwyczaj jest to krawędź zegara lub zewnętrzne przerwanie.

- Śledź dane: Śledź linie danych względem wyzwalacza. Czy dane pojawiają się przed czy po krawędzi zegara?

- Sprawdź szerokość Zmierz czas trwania impulsów. Czy sygnał „Wysoki” jest wystarczająco długi, aby został rozpoznany przez odbiorcze logikę?

- Szukaj zakłóceń: Pseudosygnalne impulsy pojawiające się między stanami stabilnymi. Mogą być spowodowane zakłóceniem przekrocznym lub zagrożeniami logicznymi.

- Analizuj przerwę: Spójrz na czas pomiędzy końcem jednej transakcji a rozpoczęciem następnej. Czy jest wystarczająco dużo czasu, aby sprzęt się zresetował?

Często problem tkwi w przerwie. Jeśli mikrokontroler zakończy zapis danych do urządzenia peripheralnego, może wymagać określonego opóźnienia przed wysłaniem kolejnego bajtu. Jeśli schemat pokazuje te bajty jeden za drugim bez przerwy, kod prawdopodobnie jest zbyt agresywny w stosunku do sprzętu.

🔌 Powszechnie stosowane protokoły i zasady czasowe

Różne protokoły komunikacyjne nakładają różne ograniczenia czasowe. Zrozumienie tych ograniczeń jest kluczowe do pisania oprogramowania firmware, które komunikuje się niezawodnie.

| Protokół | Kluczowa cecha czasowa | Typowy sposób awarii |

|---|---|---|

| UART | Bit startowy, po którym następują bity danych i bit stopu. Zależny od szybkości transmisji (baud rate). | Błędy bitów spowodowane przesunięciem zegara między nadawcą a odbiorcą. |

| I2C | Linie SCL i SDA. Wymaga rezystorów przyłączających. SDA musi być stabilna podczas stanu wysokiego SCL. | Problemy z utrzymaniem magistrali lub rozciąganiem zegara powodujące przekroczenie czasu oczekiwania. |

| SPI | Linie zegara i danych są oddzielne. Wyzwalane przez krawędź (ustawienia CPOL/CPHA). | Urządzenia zewnętrzne (slave) odpowiedziane zbyt wolno w stosunku do szybkości zegara głównego. |

| Przerwania GPIO | Wrażliwość na krawędź. Wymaga minimalnego czasu przetwarzania w procedurze obsługi przerwania (ISR). | Pominięte przerwania spowodowane długim wykonaniem poprzednich procedur obsługi. |

Na przykład w SPI czas wystąpienia krawędzi zegara względem linii danych decyduje, czy dane zostaną zapisane na zboczu narastającym czy spadającym. Jeśli firmware zakłada jedną tryb, a sprzęt jest skonfigurowany na inny, dane zostaną odczytane niepoprawnie. Schemat czasowy jasno pokazuje tę relację wizualnie, zapobiegając błędom konfiguracji.

🔍 Debugowanie problemów związanych z czasem

Gdy system zachowuje się niestabilnie, pierwszym narzędziem, do którego należy sięgnąć, nie jest debuger, ale schemat czasowy. Debugowanie z wykorzystaniem czasu polega na zapisaniu rzeczywistego zachowania elektrycznego i porównaniu go z oczekiwanym projektem.

Typowe problemy związane z czasem obejmują:

- Metastabilność: Gdy sygnał przychodzi do przerzutnika zbyt blisko krawędzi zegara, wyjście staje się nieprzewidywalne. Może ustalić się na poziomie wysokim, niskim lub pozostać w stanie pośrednim przez nieokreślony czas.

- Warunki wyścigu: Gdy wynik zależy od względnego czasu wystąpienia zdarzeń. Jeśli dwa sygnały zmieniają się jednocześnie, kolejność przetwarzania ma znaczenie.

- Integralność sygnału: Odbicia i drgania na długich śladach mogą powodować fałszywe przejścia. Na diagramie mogą pojawić się oscylacje tam, gdzie powinien być czysty sygnał prostokątny.

- Naruszenia czasu ustalenia/zachowania: Dane zmieniają się zbyt blisko krawędzi zegara. Często jest to spowodowane zbyt wysoką prędkością zegara dla danej drogi logicznej.

Aby rozwiązać te problemy, może być konieczne dodanie opóźnień w kodzie, zmiana częstotliwości zegara lub dostosowanie układu sprzętowego. Diagram czasowy dostarcza dowodów potrzebnych do podejmowania tych zmian z pewnością.

📝 Najlepsze praktyki dokumentacji

Tworzenie diagramów czasowych do dokumentacji jest tak samo ważne, jak ich odczytywanie. Zła dokumentacja czasów prowadzi do koszmarów utrzymaniowych. Przyszli inżynierowie będą mieli trudności z zrozumieniem, dlaczego do kodu dodano określone opóźnienie.

Postępuj zgodnie z tymi wskazówkami podczas tworzenia własnych diagramów:

- Używaj standardowych symboli:Unikaj niestandardowych ikon, chyba że są zdefiniowane w legendzie. Używaj standardowej notacji krawędzi narastającej/spadającej.

- Oznacz wszystko:Nie zakładaj, że czytelnik wie, co oznacza każdy sznur. Jasno oznacz wyprowadzenia, sygnały i stany.

- Zawieraj kontekst: Pokaż stan sygnałów sterujących (np. Chip Select lub Enable) obok linii danych.

- Wskazuj jednostki: Zawsze wskazuj skalę czasu. Czy to mikrosekundy, nanosekundy czy cykle zegara?

- Wyróżnij krytyczne ścieżki: Używaj pogrubionych linii lub innych kolorów, aby wyróżnić sygnały wpływające na stabilność systemu.

- Kontrola wersji: Aktualizuj diagramy, gdy zmienia się sprzęt lub firmware. Używanie przestarzałego diagramu to ryzyko.

Dokumentacja nie powinna pokazywać tylko „szczęśliwego przebiegu”. Powinna również pokazywać stany błędów. Jak wygląda diagram, gdy występuje przekroczenie czasu oczekiwania? Jak wygląda, gdy zostanie wyzwolony reset? Te scenariusze to często miejsca, gdzie kryją się najwięksi błędy.

🌡️ Czynniki środowiskowe

Diagram czasowy często generowany jest w idealnych warunkach laboratoryjnych. Środowiska rzeczywiste rzadko są idealne. Temperatura, napięcie i zakłócenia elektromagnetyczne wszystkie wpływają na propagację sygnału.

Zważ na następujące czynniki:

- Temperatura:Wydajność krzemu pogarsza się przy wysokich temperaturach. Opóźnienie propagacji rośnie. System działający przy 25°C może zawieść przy 85°C.

- Napięcie:Niższe napięcie zasilania zwiększa opóźnienie. Wyższe napięcie może zmniejszyć opóźnienie, ale zwiększa zużycie mocy i ciepło.

- Pojemność obciążenia: Długi przewody dodają pojemność. Powoduje to spowolnienie czasów narastania i spadania sygnałów, efektywnie rozszerzając szerokość impulsu, ale spowalniając przejście.

Wytrzymały projekt uwzględnia te zmiany. Przy tworzeniu diagramu czasowego dla produkcji należy rozważyć „najgorszy przypadek”. Oznacza to, że diagram przedstawia najwolniejsze możliwe przejścia sygnałów i najprędkiejsze możliwe krawędzie zegara. Jeśli system działa w tych warunkach, będzie działał w większości warunków.

🛠️ Tworzenie i weryfikacja diagramów

Choć ręczne rysowanie jest możliwe, współczesna inżynieria opiera się na narzędziach automatycznych do zapisywania i weryfikacji czasów. Jednak zasady pozostają takie same niezależnie od użytego narzędzia. Celem jest wizualizacja przepływu czasu.

Podczas weryfikacji diagramu:

- Porównaj z danymi technicznymi: Upewnij się, że wartości czasowe w Twoim diagramie odpowiadają specyfikacji producenta dla użytych układów.

- Uruchom symulacje: Użyj środowisk symulacyjnych do modelowania logiki przed budową rzeczywistego obwodu.

- Pomiar sprzętu rzeczywistego: Nic nie zastępuje rzeczywistego pomiaru. Zapisz przebiegi z fizycznego płytki i nakładaj je na diagram projektu.

- Sprawdź zapasy: Czy jest wystarczająco dużo czasu zapasowego między sygnałami? Jeśli zapas wynosi zero, każda zmiana spowoduje awarię.

Weryfikacja to ciągły proces. W miarę rozwoju oprogramowania wymagania czasowe mogą się zmieniać. Nowy obsługujący przerwania może wprowadzić opóźnienie, które przesunie sygnał poza jego termin. Ciągła weryfikacja zapewnia, że most między kodem a sprzętem pozostaje niezawodny.

🔗 Przecięcie logiki i fizyki

Na końcu diagram czasowy reprezentuje przecięcie logiki i fizyki. Logika określa, co powinno się zdarzyć; fizyka określa, co naprawdę się dzieje. Zadaniem inżyniera jest dopasowanie tych dwóch rzeczywistości.

Opanowanie interpretacji i tworzenia tych diagramów daje Ci możliwość diagnozowania skomplikowanych awarii, które inni mogą pominąć. Przestajesz zgadywać, dlaczego system zawiesza się, i zaczynasz dokładnie widzieć, gdzie naruszone zostało ograniczenie czasowe. Takie zrozumienie przekształca programistę w projektanta.

Niezależnie od tego, czy projektujesz prosty interfejs czujnika, czy szybki magistralę komunikacyjną, diagram czasowy jest Twoim głównym źródłem informacji. Zapewnia, że kod, który piszesz, wykonuje się w czasie oczekiwanym przez sprzęt. Zapewnia, że sygnały widoczne na ekranie odpowiadają napięciom na wyprowadzeniach. To język synchronizacji.

Inwestuj czas w zrozumienie tych diagramów. Traktuj je z taką samą powagą jak sam kod. W systemach wbudowanych czas nie jest tylko szczegółem, ale fundamentem niezawodności. Gdy kod i sprzęt mówią tym samym językiem czasu, system działa z precyzją i stabilnością.