时序图是可视化数字信号在特定时间段内行为的重要工具。在数字电子和计算机工程领域,理解信号之间的相互作用对于系统的稳定性和性能至关重要。本指南将详细解析时序图符号,确保您能够精确地阅读、创建和解读波形。我们将探讨信号电平、时间轴、信号转换以及关键时序参数,且不依赖于特定的软件工具。

🔍 理解时序图的核心组成部分

从根本上说,时序图表示信号相对于时间的逻辑状态。它充当数据在系统中流动的蓝图。要正确解读这些图表,必须理解基本的坐标轴和信号表示方法。

- 水平轴: 表示时间。该轴从左向右流动,表示事件的顺序。

- 垂直轴: 表示特定信号线的逻辑状态或电压电平。

- 信号线: 每条水平线对应电路中的特定导线、网络或逻辑变量。

- 逻辑电平: 信号通常在两种状态之间切换,通常称为高电平和低电平。

在分析时序图时,观察者会寻找一个信号变化与另一个信号变化之间的关系。这种关系决定了数据是否被正确捕获,或是否出现错误。正确的符号表示可确保这些关系对审查设计的工程师来说清晰无歧义。

⚡ 信号逻辑电平与状态

数字系统基于二进制原理运行,但其物理表示方式各不相同。符号必须明确界定逻辑1和逻辑0的定义。误解这些电平可能导致灾难性的设计失败。

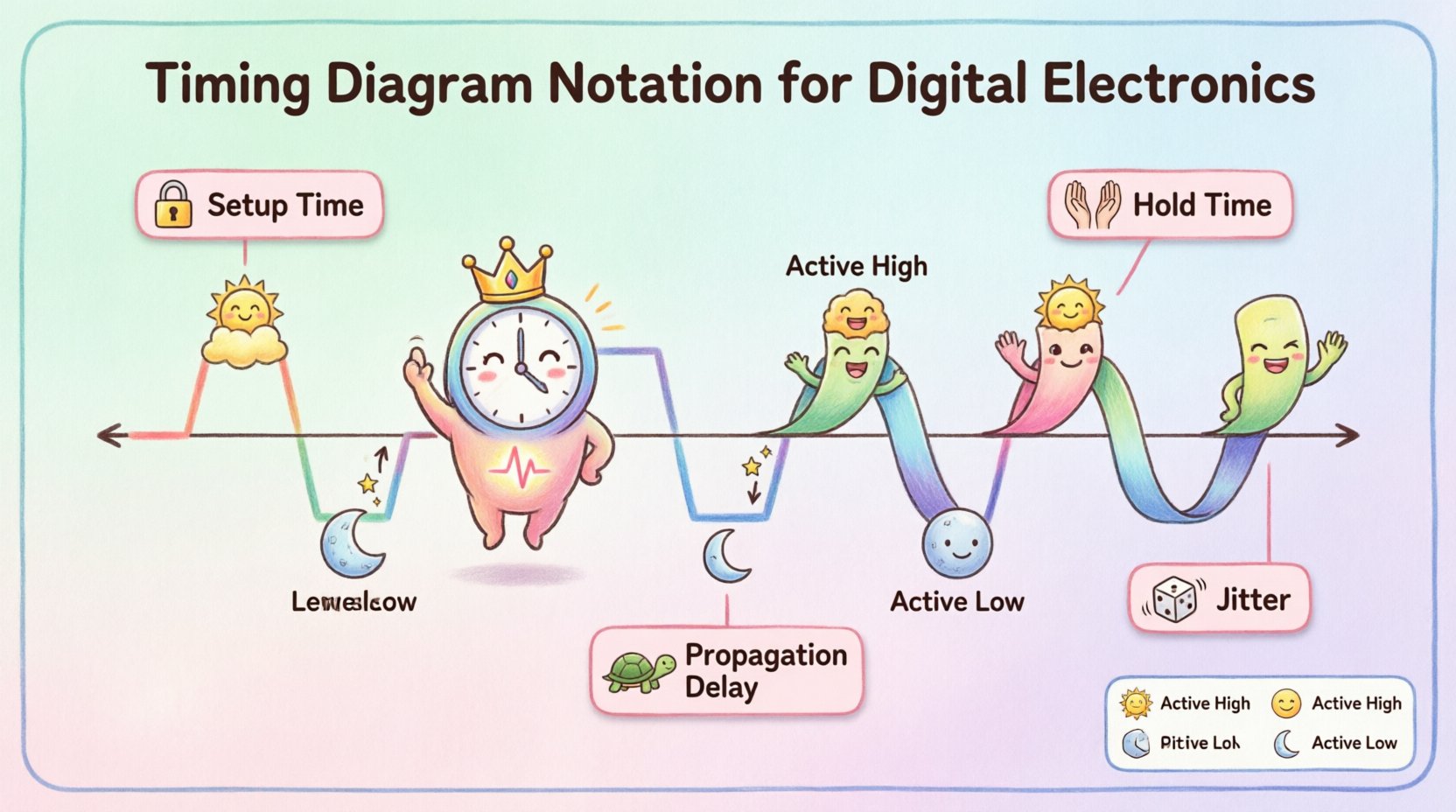

高电平有效与低电平有效

信号在高电平时可为有效,或在低电平时可为有效。这一概念对于复位或使能等控制信号至关重要。

- 高电平有效: 当电压为高电平时(逻辑1),信号执行其功能。这是大多数数据线的标准。

- 低电平有效: 当电压为低电平时(逻辑0),信号执行其功能。控制信号通常采用此表示方式以减少噪声或满足特定硬件需求。

- 符号指示: 低电平有效的信号通常在名称上方加一横线,或在原理图中信号线末端加一个圆圈来标记。

逻辑电压电平

尽管逻辑0和1是抽象概念,但时序图表示的是物理电压。符号应尽可能明确指定电压阈值。

- 逻辑高电平: 通常用高于特定阈值的电压表示(例如3.3V或5V)。

- 逻辑低电平: 通常用低于特定阈值的电压表示(例如0V)。

- 未定义区域: 高阈值和低阈值之间的区域,信号状态不确定。图表应避免停留在该区域。

⏱️ 时间轴与同步

时间的表示是时序图中第二重要的方面。与电压不同,时间是连续的,但数字信号在离散时刻发生变化。符号表示必须能够处理同步和异步事件。

时钟信号

大多数数字系统依赖时钟来同步操作。时钟信号是系统的脉搏。

- 周期: 时钟一个完整周期所需的时间。

- 频率: 每秒的周期数,通常以赫兹为单位测量。

- 占空比: 信号处于高电平的周期百分比。

- 符号表示: 时钟信号通常以方波形式绘制。

相对时间与绝对时间

时序图可以使用相对时间或绝对时间。

- 相对时间: 测量从一个参考点(如特定时钟边沿)开始。这在建立时间和保持时间分析中很常见。

- 绝对时间: 为事件分配具体的时戳,对于长时间调试通信协议非常有用。

时间尺度

选择正确的时间尺度对于清晰表达至关重要。

- 纳秒: 用于高速逻辑,信号变化迅速。

- 微秒: 用于较慢的外设交互。

- 毫秒: 用于系统级电源管理或低频事件。

🔄 边沿跳变与符号表示

信号状态发生变化的瞬间,与状态本身同样重要。符号表示必须清晰地展示这些跳变发生的方式和时间。

上升沿与下降沿

边表示逻辑电平之间的转换。

- 上升沿: 从低电平到高电平的转换。通常用垂直线或指向上的箭头表示。

- 下降沿: 从高电平到低电平的转换。通常用垂直线或指向下的箭头表示。

- 斜率: 在理想图中,边是垂直的。在实际图中,边具有斜率,表示上升时间或下降时间。

转换延迟

信号不会立即切换。符号必须考虑传播延迟。

- 传播延迟: 输入发生变化到输出发生变化所需的时间。

- 符号表示: 通常用输入转换和输出转换之间的间隙来表示。

毛刺和竞争冒险

由于电路延迟,可能会出现意外的转换。这些通常表现为短暂的尖峰。

- 毛刺: 本不应存在的短暂脉冲。符号可能使用虚线或不同颜色表示。

- 竞争冒险: 由于时序差异可能导致输出错误的潜在风险。

📏 关键时序参数

某些参数定义了数字接口的可靠性。这些是工程师用来确保数据完整性的测量指标。

| 参数 | 描述 | 单位 |

|---|---|---|

| 建立时间 | 数据必须在时钟边沿之前保持稳定。 | 时间(ns) |

| 保持时间 | 数据必须在时钟边沿之后保持稳定。 | 时间(ns) |

| 传播延迟 | 从输入变化到输出变化的时间。 | 时间(ns) |

| 时钟到输出 | 从时钟边沿到输出变化的时间。 | 时间(ns) |

| 抖动 | 信号边沿定时的波动。 | 时间(ps/ns) |

建立时间和保持时间

这些是同步系统中最关键的约束条件。

- 建立时间违规: 如果数据在时钟边沿附近变化过快,系统可能无法捕获正确的值。

- 保持时间违规: 如果数据在时钟边沿之后过快变化,系统可能会丢失该值。

- 符号表示: 通常以时钟边沿附近的时间窗口形式表示,数据线在此期间不得变化。

传播延迟

此延迟会影响系统的最大频率。

- 高电平到低电平: 信号从高电平变为低电平所需的时间。

- 低电平到高电平: 信号从低电平变为高电平所需的时间。

- 符号表示: 通常以输入和输出波形之间的水平间隙表示。

🛠️ 控制信号与有效状态

控制信号用于管理数据的流动。其符号必须明确表示出何时处于有效状态。

| 信号类型 | 有效状态 | 符号示例 |

|---|---|---|

| 复位 | 低电平有效 | 复位# 或 复位_bar |

| 使能 | 高电平有效 | 使能 |

| 中断 | 高电平或低电平有效 | IRQ 或 IRQ_bar |

| 片选 | 低电平有效 | CS# |

复位信号

复位信号用于初始化系统。它们可以是异步的或同步的。

- 异步复位:无论时钟如何,立即生效。符号表示复位线在任何时间变为有效。

- 同步复位:仅在时钟边沿时生效。符号表示复位线在时钟边沿前已处于有效状态。

使能信号

使能信号用于允许或阻止操作。

- 高电平使能:当信号为高电平时执行操作。

- 低电平使能:当信号为低电平时执行操作。

📖 读取和分析波形

读取时序图需要系统化的方法。工程师应遵循特定步骤,以避免误解。

分步分析

- 识别时钟:找到主要的时序参考。所有同步事件都与之相关。

- 追踪数据流: 跟随数据线从源到目标。

- 检查时序窗口: 验证建立时间和保持时间是否符合时钟边沿。

- 查找异常: 识别毛刺、尖峰或意外的电平跳变。

- 验证逻辑电平: 确保有效状态与器件规格相符。

常见误解

- 假设瞬时变化: 实际信号具有上升时间和下降时间。假设垂直边沿可能会掩盖时序违规。

- 忽略异步信号: 未被时钟同步的控制信号可能在任何时间出现,必须独立检查。

- 误读有效状态: 将高电平有效与低电平有效混淆是设计错误的常见原因。

🚀 高级时序考虑

随着系统速度的提升,时序分析变得更加复杂。高级符号用于应对这些挑战。

亚稳态

当信号在建立或保持窗口期间发生变化时,输出可能进入亚稳态。

- 定义: 信号稳定在中间电压电平。

- 符号表示: 通常用问号或高低电平之间的阴影区域表示。

- 解决: 信号最终会稳定为高电平或低电平,但具体时间不可预测。

同步偏差

不同路径到达目标所需的时间可能不同。

- 时钟偏差: 时钟信号在不同组件上以不同时间到达。

- 数据偏差: 数据信号在不同时间到达不同的目的地。

- 符号:以预期到达时间与实际到达时间之间的水平偏移来表示。

抖动

抖动是信号边沿与其理想位置之间的偏差。

- 周期间抖动:一个时钟周期与下一个时钟周期之间的变化。

- 周期抖动:时钟周期总持续时间的变化。

- 符号:通常以理想边沿位置周围的阴影区域表示。

📝 文档编写最佳实践

创建清晰的时序图可确保他人理解你的设计。遵循最佳实践可减少歧义。

- 命名一致:为所有信号使用清晰且唯一的名称。避免使用 Signal1 或 Signal2 等通用名称。

- 标准符号:使用标准符号表示边沿、电平和延迟,以确保行业兼容性。

- 清晰的时间尺度:明确标注时间轴单位(ns、µs、ms)。

- 分组相关信号:将属于同一协议或子系统的信号分组在一起。

- 突出关键时间点:使用粗线或颜色突出显示建立时间和保持时间窗口。

- 提供图例:为图中使用的任何自定义符号或缩写提供说明。

🔚 关键要点总结

时序图符号是数字设计领域任何人员的基本技能。通过理解核心组件、信号电平和时序参数,工程师可以确保系统的稳健性能。正确的符号使用可消除歧义,防止昂贵的设计错误。请记住,要重点关注建立时间和保持时间,明确界定有效状态,并考虑传播延迟和抖动等实际信号特性。遵循这些指南将带来清晰且高效的文档。

在创建或审查这些图表时,务必根据硬件规格验证逻辑电平。确保时间轴反映系统实际的工作频率。最后,在所有文档中保持符号风格的一致性,以促进协作。通过实践,解读和创建这些图表将成为设计流程中的自然组成部分。

实施的最后说明

尽管本指南涵盖了理论和符号方面的内容,但实际实施需要关注物理层。信号完整性、噪声裕量和电源传输都会影响时序行为。务必结合数据手册和仿真结果来核对时序图,以验证设计。持续学习并遵循行业标准,将使您的设计保持可靠和高效。