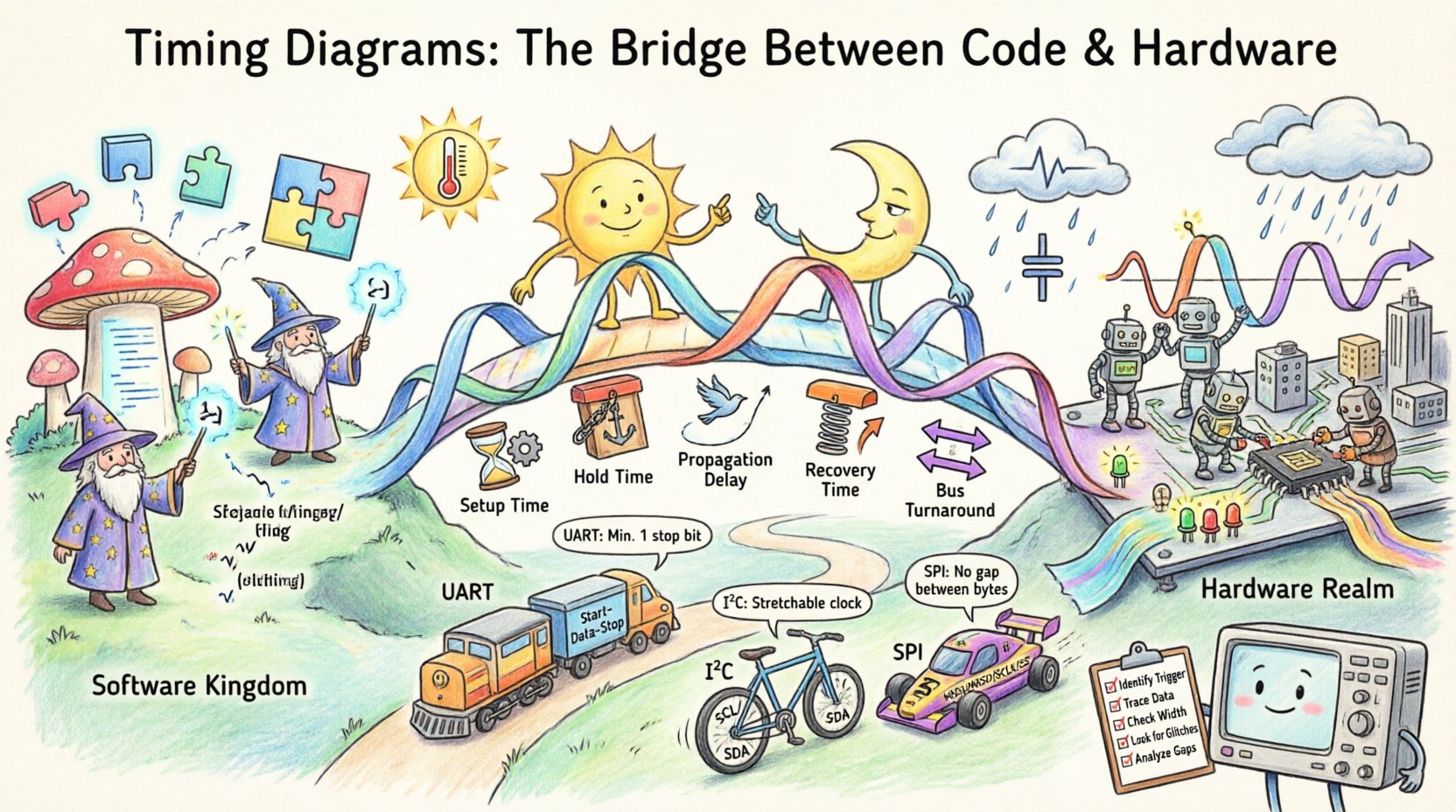

Wenn Softwareingenieure Code schreiben, denken sie in Anweisungen, Variablen und Logikflüssen. Wenn Hardwareingenieure Schaltungen entwerfen, denken sie in Spannungsniveaus, Ausbreitungsverzögerungen und Taktrunden. Diese beiden Welten befinden sich oft in einem Zustand der Spannung. Der Code erwartet, dass ein Signal zu einem bestimmten logischen Zeitpunkt eintrifft, doch die Hardware arbeitet mit physischer Zeit, die Störungen, Temperatur und elektrischem Widerstand unterliegt. Die Brücke zwischen diesen beiden Bereichen ist das Zeitdiagramm.

Ein Zeitdiagramm ist nicht bloß ein Bild; es ist ein Vertrag. Es definiert die genaue Beziehung zwischen Ereignissen in der Zeit. Es sagt der Firmware, wann es sicher ist, einen Pin zu lesen, und sagt dem Silizium, wann es sicher ist, eine Leitung zu treiben. Ohne ein klares Verständnis dieser Diagramme versagen eingebettete Systeme unvorhersehbar. Datenkorruption, Rennbedingungen und Systemhängen werden zu häufigen Problemen. Dieser Leitfaden untersucht die Mechanik von Zeitdiagrammen, die zugrundeliegende Physik und wie man sie effektiv liest und erstellt.

📊 Die Anatomie eines Signals

Im Kern beruht die digitale Logik auf binären Zuständen. In der physischen Welt werden diese Zustände jedoch durch Spannungsniveaus dargestellt. Ein „High“ könnte 3,3 Volt betragen, ein „Low“ 0 Volt. Doch Signale wechseln nicht sofort. Sie steigen und fallen über einen endlichen Zeitraum. Ein Zeitdiagramm visualisiert diesen Übergang.

Das Verständnis der visuellen Sprache dieser Diagramme ist der erste Schritt hin zur Meisterschaft. Zu den zentralen Elementen gehören:

- Zeitachse: Meist horizontal und von links nach rechts verlaufend. Sie kann linear oder logarithmisch sein, wobei linear für die meisten Logikanalysen Standard ist.

- Signallinien: Vertikale Linien, die spezifische Leitungen, Pins oder interne Knoten darstellen.

- Übergänge: Die Bewegung von Low nach High (steigender Flank) oder von High nach Low (fallender Flank). Diese Flanken lösen oft Zustandsänderungen in der sequenziellen Logik aus.

- Niveaus: Der stabile Zustand eines Signals vor oder nach einem Übergang.

- Beschriftungen: Textliche Anmerkungen, die die Bedeutung eines bestimmten Pulses oder Intervalls klären.

Betrachten wir ein einfaches Taktsignal. Es oszilliert zwischen High und Low. Die Zeit, die benötigt wird, um eine volle Schwingung zu vollenden, ist die Periode. Der Kehrwert der Periode ist die Frequenz. In einem Zeitdiagramm fungiert der Takt als Herzschlag des Systems. Jedes andere Signal ist oft an diese Flanken synchronisiert.

🕰️ Der Taktdomäne

Die meisten digitalen Systeme arbeiten innerhalb einer Taktdomäne. Dies ist eine Gruppe von Schaltungen, die sich die gleiche Zeitreferenz teilen. Doch Signale überschreiten häufig verschiedene Domänen. Dies führt zu Komplexität. Ein Signal, das in einer schnellen Domäne erzeugt wird, könnte für eine langsame Domäne zu spät oder zu früh eintreffen, was eine Halteverletzung verursacht.

Beim Analyse der Zeitverläufe müssen Sie berücksichtigen:

- Taktverzögerung (Clock Skew): Der Unterschied in der Ankunftszeit des Taktsignals an verschiedenen Komponenten. Wenn der Takt beim Sender früher eintrifft als beim Empfänger, verkleinern sich die Zeitmargen.

- Phasenverschiebung: In einigen Systemen sind Signale nicht mit der Taktränder ausgerichtet, sondern treten in der Mitte des Zyklus auf.

- Jitter: Schwankungen in der Zeitgestaltung eines Signals. Jitter kann zufällig oder deterministisch sein. Er verringert die Rauschmarke und macht das Diagramm weniger vorhersehbar.

Code, der zur Schnittstelle mit der Hardware geschrieben wird, geht von einem stabilen Takt aus. Wenn der physische Takt aufgrund von Temperatur- oder Spannungsfluktuationen driftet, stimmt das Zeitdiagramm nicht mehr mit der Realität überein. Deshalb müssen Zeitdiagramme Toleranzbereiche oder Worst-Case-Szenarien enthalten.

⚙️ Kritische Zeitparameter

Bestimmte Parameter definieren die Grenzen der Signalintegrität. Diese Werte finden sich oft in Datenblättern, sind aber am besten im Kontext eines Zeitdiagramms zu verstehen. Die folgende Tabelle fasst die wichtigsten Parameter zusammen, die Ingenieure bewerten müssen.

| Parameter | Definition | Einfluss auf das System |

|---|---|---|

| Setup-Zeit | Die minimale Zeit, in der die Daten stabil sein müssenvor der Taktflanke. | Wenn verletzt, kann der empfangende Flip-Flop den korrekten Wert nicht erfassen. |

| Hold-Zeit | Die minimale Zeit, in der die Daten stabil bleiben müssennach der Taktflanke. | Wenn verletzt, kann der Flip-Flop in einen metastabilen Zustand geraten. |

| Propagationsverzögerung | Zeit, die benötigt wird, damit ein Signal von der Eingabe zur Ausgabe gelangt. | Verzögerungen addieren sich über Logikgatter und können dazu führen, dass Taktzyklen verpasst werden. |

| Recovery-Zeit | Zeit, die benötigt wird, damit ein Steuersignal nach einem asynchronen Ereignis wieder normal wird. | Bestimmt, wie schnell das System von Resets oder Unterbrechungen wiederhergestellt wird. |

| Bus-Umschaltzeit | Zeit, die benötigt wird, um einen Bus von Ausgangs- in Eingangsmodus umzuschalten. | Wesentlich für bidirektionale Busse wie I2C oder 1-Wire. |

Die Verletzung dieser Parameter verursacht nicht immer sofort einen Absturz. Manchmal funktioniert das System 99 % der Zeit und versagt nur unter bestimmten Bedingungen. Deshalb ist die Zeitanalyse ein iterativer Prozess. Sie müssen sicherstellen, dass das Diagramm auch unter ungünstigsten Spannungs- und Temperaturbedingungen gültig bleibt.

👀 Die Wellenform lesen

Das Lesen eines Zeitdiagramms erfordert einen systematischen Ansatz. Beim Debuggen eines Hardwareproblems sollten Sie nicht nur die Signalpegel betrachten. Betrachten Sie vielmehr die Beziehungen zwischen den Signalen.

Folgen Sie diesen Schritten zur Analyse einer Wellenform:

- Identifizieren Sie den Auslöser: Finden Sie das Ereignis, das die Sequenz startet. Dies ist normalerweise eine Taktflanke oder eine externe Unterbrechung.

- Verfolgen Sie die Daten: Verfolgen Sie die Datenleitungen im Verhältnis zum Auslöser. Tauchen die Daten vor oder nach der Taktflanke auf?

- Prüfen Sie die Breite: Messen Sie die Dauer von Pulsen. Ist ein „High“-Signal lang genug, um von der empfangenden Logik erkannt zu werden?

- Suchen Sie nach Störimpulsen: Fehlpulse, die zwischen stabilen Zuständen auftreten. Sie können durch Crosstalk oder Logikhazards verursacht werden.

- Analysieren Sie die Lücke: Betrachten Sie die Zeit zwischen dem Ende einer Transaktion und dem Beginn der nächsten. Gibt es ausreichend Zeit, damit die Hardware zurückgesetzt werden kann?

Oft liegt das Problem in der Lücke. Wenn ein Mikrocontroller die Datenübertragung an ein Peripheriegerät abgeschlossen hat, könnte er eine bestimmte Verzögerung benötigen, bevor er das nächste Byte sendet. Wenn das Diagramm zeigt, dass diese Bytes ohne Lücke direkt hintereinander folgen, ist der Code wahrscheinlich zu aggressiv für die Hardware.

🔌 Häufige Protokolle und Taktsignale

Verschiedene Kommunikationsprotokolle setzen unterschiedliche zeitliche Anforderungen. Das Verständnis dieser Anforderungen ist entscheidend für die Entwicklung von Firmware, die zuverlässig kommuniziert.

| Protokoll | Wichtige zeitliche Eigenschaft | Häufiger Ausfallzustand |

|---|---|---|

| UART | Startbit gefolgt von Datenbits und Stopbit. Abhängig von der Baudrate. | Bitfehler aufgrund von Taktdrift zwischen Sender und Empfänger. |

| I2C | SCL- und SDA-Leitungen. Erfordert Pull-up-Widerstände. SDA muss während SCL-Hoch stabil sein. | Bus-Hold-up- oder Clock-Stretching-Probleme, die zu Timeouts führen. |

| SPI | Taktsignal- und Datenleitung sind getrennt. Flankenauslösend (CPOL/CPHA-Einstellungen). | Slave-Geräte antworten zu langsam für die Taktfrequenz des Masters. |

| GPIO-Interrupts | Flankenempfindlichkeit. Erfordert minimale Verarbeitungszeit im ISR. | Verpasste Interrupts aufgrund langer Ausführung vorheriger Dienstprogramme. |

Zum Beispiel bestimmt in SPI die Timing-Beziehung zwischen der Taktkante und der Datenleitung, ob die Daten an der steigenden oder fallenden Flanke erfasst werden. Wenn die Firmware einen Modus annimmt, der Hardware jedoch auf den anderen eingestellt ist, wird die Daten falsch gelesen. Ein Zeitdiagramm klärt diese Beziehung visuell und verhindert Konfigurationsfehler.

🔍 Debuggen von Zeitproblemen

Wenn ein System unstabil reagiert, ist das erste Werkzeug, das man greifen sollte, kein Debugger, sondern ein Zeitdiagramm. Das Debuggen mit Zeitbezug beinhaltet das Erfassen des tatsächlichen elektrischen Verhaltens und dessen Vergleich mit dem erwarteten Entwurf.

Häufige zeitbezogene Probleme sind:

- Metastabilität: Wenn ein Signal zu nahe an der Taktkante bei einem Flip-Flop eintrifft, wird die Ausgabe vorhersehbar. Sie kann sich auf High, Low oder in einem Zwischenzustand für eine unbestimmte Zeit einstellen.

- Rennbedingungen: Wenn das Ergebnis von der relativen Abfolge der Ereignisse abhängt. Wenn zwei Signale gleichzeitig wechseln, ist die Reihenfolge der Verarbeitung von Bedeutung.

- Signalintegrität:Reflexionen und Ringing auf langen Spuren können falsche Übergänge verursachen. Das Diagramm kann Oszillationen zeigen, wo ein sauberer Rechteckwellenverlauf erwartet wird.

- Setup/Hold-Verletzungen:Der Datenwert ändert sich zu nahe am Taktflankengrenzwert. Dies wird oft durch eine zu hohe Taktfrequenz für den Logikpfad verursacht.

Um diese Probleme zu beheben, müssen Sie möglicherweise Verzögerungen im Code hinzufügen, die Taktfrequenz ändern oder die Hardwareanordnung anpassen. Das Zeitdiagramm liefert die Beweise, die erforderlich sind, um diese Änderungen selbstsicher vorzunehmen.

📝 Best Practices für die Dokumentation

Das Erstellen von Zeitdiagrammen zur Dokumentation ist ebenso wichtig wie das Lesen davon. Schlecht dokumentierte Zeitabläufe führen zu Wartungs-Albträumen. Zukünftige Ingenieure werden Schwierigkeiten haben zu verstehen, warum eine bestimmte Verzögerung in den Code eingefügt wurde.

Beachten Sie diese Richtlinien beim Erstellen Ihrer eigenen Diagramme:

- Verwenden Sie Standard-Symbole:Vermeiden Sie benutzerdefinierte Symbole, es sei denn, sie sind in einer Legende definiert. Verwenden Sie die Standardnotation für steigende/abfallende Flanken.

- Beschriften Sie alles:Gehen Sie nicht davon aus, dass der Leser weiß, was jede Linie darstellt. Beschriften Sie Pins, Signale und Zustände klar.

- Fügen Sie Kontext hinzu: Zeigen Sie den Zustand der Steuersignale (wie Chip Select oder Enable) neben den Datenleitungen an.

- Geben Sie Einheiten an: Geben Sie immer die Zeitskala an. Handelt es sich um Mikrosekunden, Nanosekunden oder Taktzyklen?

- Markieren Sie kritische Pfade:Verwenden Sie fett gedruckte Linien oder verschiedene Farben, um die Signale hervorzuheben, die die Systemstabilität bestimmen.

- Versionskontrolle:Aktualisieren Sie die Diagramme, wenn sich die Hardware oder die Firmware ändert. Ein veraltetes Diagramm ist eine Gefahr.

Die Dokumentation sollte nicht nur den „glücklichen Pfad“ zeigen. Sie sollte auch Fehlerzustände darstellen. Wie sieht das Diagramm aus, wenn ein Timeout eintritt? Wie sieht es aus, wenn ein Reset ausgelöst wird? Diese Szenarien sind oft die Orte, an denen die meisten Fehler lauern.

🌡️ Umweltfaktoren

Ein Zeitdiagramm wird oft unter idealen Laborbedingungen erstellt. Realitätsnahe Umgebungen sind selten ideal. Temperatur, Spannung und elektromagnetische Störungen beeinflussen alle die Signalübertragung.

Berücksichtigen Sie folgende Faktoren:

- Temperatur:Die Leistung von Silizium nimmt bei hohen Temperaturen ab. Die Ausbreitungsverzögerung steigt. Ein System, das bei 25 °C funktioniert, könnte bei 85 °C versagen.

- Spannung:Eine niedrigere Versorgungsspannung erhöht die Verzögerung. Höhere Spannung könnte die Verzögerung verringern, erhöht aber den Stromverbrauch und die Wärmeentwicklung.

- Lastkapazität: Lange Leitungen fügen Kapazität hinzu. Dies verlangsamt die Anstiegs- und Abfallzeiten der Signale und vergrößert effektiv die Pulsbreite, verlangsamt jedoch die Übergänge.

Ein robustes Design berücksichtigt diese Variationen. Beim Erstellen eines Zeitdiagramms für die Produktion sollte der „schlechteste Fall“ berücksichtigt werden. Das bedeutet, dass das Diagramm die langsamsten möglichen Signalübergänge und die schnellsten möglichen Taktränder darstellt. Wenn das System unter diesen Bedingungen funktioniert, wird es in den meisten Fällen funktionieren.

🛠️ Erstellen und Überprüfen von Diagrammen

Obwohl manuelle Zeichnungen möglich sind, stützt sich die moderne Ingenieurarbeit auf automatisierte Werkzeuge zur Erfassung und Überprüfung der Zeitabläufe. Die Prinzipien bleiben jedoch unabhängig vom eingesetzten Werkzeug gleich. Ziel ist es, den Ablauf der Zeit visuell darzustellen.

Beim Überprüfen eines Diagramms:

- Vergleichen mit Datenblättern: Stellen Sie sicher, dass die Zeitwerte in Ihrem Diagramm den Spezifikationen des Herstellers für die verwendeten Chips entsprechen.

- Simulationen durchführen: Verwenden Sie Simulationsumgebungen, um die Logik zu modellieren, bevor die physische Schaltung aufgebaut wird.

- Messung an echter Hardware: Nichts ersetzt die eigentliche Messung. Erfassen Sie Wellenformen von der physischen Platine und legen Sie sie über das Entwurfsdiagramm.

- Randbedingungen prüfen: Gibt es ausreichend Pufferzeit zwischen den Signalen? Wenn der Puffer null ist, führt jede Variation zu einem Ausfall.

Die Überprüfung ist ein fortlaufender Prozess. Während sich die Firmware weiterentwickelt, können sich die Zeitbedingungen ändern. Ein neuer Interrupt-Handler könnte eine Verzögerung einführen, die ein Signal über seine Frist hinaus verschiebt. Die kontinuierliche Überprüfung stellt sicher, dass die Brücke zwischen Code und Hardware stabil bleibt.

🔗 Der Schnittpunkt von Logik und Physik

Letztendlich stellt ein Zeitdiagramm den Schnittpunkt von Logik und Physik dar. Die Logik bestimmt, was passieren sollte; die Physik bestimmt, was tatsächlich passiert. Die Aufgabe des Ingenieurs besteht darin, diese beiden Realitäten zu vereinbaren.

Durch die Beherrschung der Interpretation und Erstellung dieser Diagramme erlangen Sie die Fähigkeit, komplexe Ausfälle zu diagnostizieren, die andere übersehen könnten. Sie hören auf, zu raten, warum das System hängt, und beginnen, genau dort zu sehen, wo die Zeitbedingung verletzt wurde. Diese Erkenntnisstufe verwandelt einen Entwickler in einen Designer.

Unabhängig davon, ob Sie eine einfache Sensoreinheit oder einen Hochgeschwindigkeitskommunikationsbus entwerfen, ist das Zeitdiagramm Ihre primäre Referenz. Es stellt sicher, dass der von Ihnen geschriebene Code in der Zeit ausgeführt wird, die die Hardware erwartet. Es stellt sicher, dass die Signale, die Sie auf dem Bildschirm sehen, den Spannungen an den Pins entsprechen. Es ist die Sprache der Synchronisation.

Investieren Sie Zeit, um diese Diagramme zu verstehen. Behandeln Sie sie mit der gleichen Ernsthaftigkeit wie den Code selbst. In eingebetteten Systemen ist Zeitverhalten nicht nur eine Detailfrage, sondern die Grundlage der Zuverlässigkeit. Wenn Code und Hardware dieselbe Sprache der Zeit sprechen, funktioniert das System präzise und stabil.