Das Verständnis des Signalverlaufs über die Zeit ist grundlegend für die Digitalelektronik. Für Ingenieurstudenten ist die Beherrschung der Interpretation von Zeitdiagrammen nicht nur eine akademische Übung; es ist eine entscheidende Fähigkeit zur Entwicklung zuverlässiger Systeme. Diese visuellen Darstellungen zeigen das Verhalten von Signalen entlang einer Zeitachse auf und offenbaren Beziehungen zwischen Taktrunden, Datengültigkeit und Steuersignalen. Ohne ein sicheres Verständnis dieser Techniken können selbst einfache Schaltungen unter realen Bedingungen versagen.

Dieser Leitfaden behandelt die zentralen Prinzipien, die erforderlich sind, um Zeitdiagramme effektiv zu lesen, zu erstellen und zu analysieren. Wir werden die Mechanismen der synchronen und asynchronen Schaltungstechnik untersuchen, die Bedeutung von Setup- und Hold-Zeiten erläutern und zeigen, wie häufige Fehler vermieden werden können, die zu Schaltungsfehlern führen. Am Ende dieses Artikels werden Sie über eine solide Grundlage verfügen, um komplexe Probleme der digitalen Logik zu bewältigen.

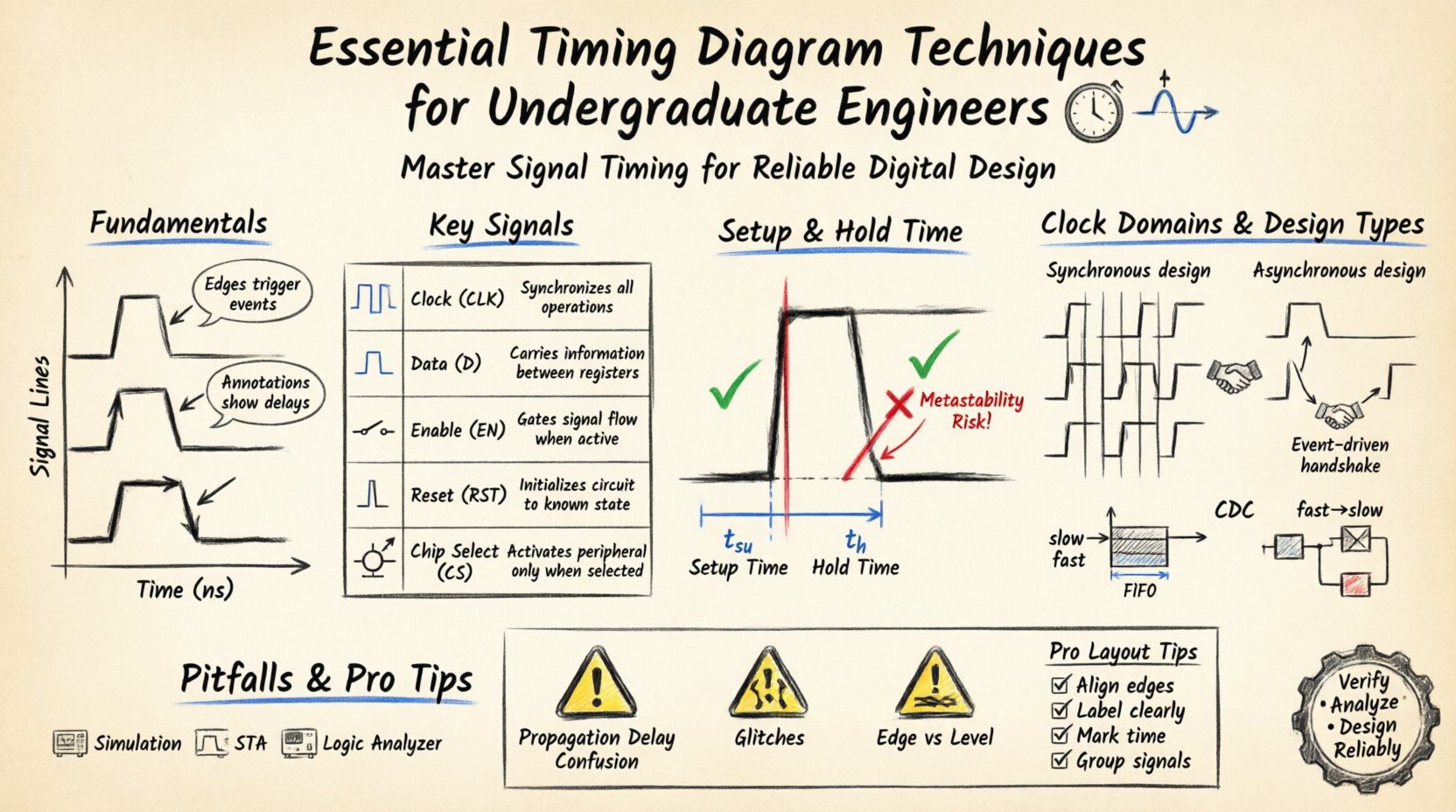

1. Grundlagen der Zeitdiagramme 📐

Ein Zeitdiagramm ist eine grafische Darstellung von Signalen über die Zeit. Es ermöglicht Ingenieuren, den Zustand verschiedener Leitungen in einer digitalen Schaltung zu visualisieren. Im Gegensatz zu Logikdiagrammen, die die Verbindungen zeigen, verdeutlichen Zeitdiagramme das Verhalten. Sie sind unverzichtbar für die Fehlersuche, die Überprüfung von Entwürfen und die Kommunikation von Signalwechselwirkungen zwischen Hardwaremodulen.

Wichtige Bestandteile eines Zeitdiagramms

- Zeitachse (X-Achse):Stellt den Fortschritt der Zeit dar. Sie ist typischerweise in Nanosekunden (ns) oder Taktrunden markiert.

- Signalleitungen (Y-Achse):Horizontale Linien, die einzelne Leitungen oder Bussysteme darstellen. Jede Linie entspricht einem bestimmten Signalnamen.

- Logische Pegel:Signale sind in der Regel binär und werden als High (1) oder Low (0) dargestellt. In Bus-Designs treten manchmal Zustände mit ‘High-Z’ (Hochimpedanz) auf.

- Kanten:Vertikale Übergänge deuten auf einen Zustandswechsel hin. Ansteigende Kanten (Low zu High) und absteigende Kanten (High zu Low) sind entscheidend für die Auslösung von Ereignissen.

- Anmerkungen:Textmarkierungen deuten oft auf Verzögerungen, bestimmte Zeiten oder Bedingungen hin, die das Signal beeinflussen.

Warum die Zeitmessung in der digitalen Logik wichtig ist

Digitale Systeme beruhen auf präziser Synchronisation. Wenn ein Signal zu früh oder zu spät im Verhältnis zu einer Taktränderung eintrifft, kann das System die Daten falsch deuten. Zeitdiagramme machen diese Einschränkungen sichtbar. Sie helfen dabei, Fragen wie folgende zu beantworten:

- Ist der Datenwert vor der Taktränderung stabil?

- Wie lange dauert es, bis ein Signal durch ein Gatter propagiert?

- Stören sich zwei Takte aus unterschiedlichen Bereichen gegenseitig?

2. Wichtige Signale und Komponenten ⚡

Bevor Sie komplexe Wellenformen analysieren, müssen Sie die gängigen Signale in der digitalen Technik erkennen. Diese Signale bestimmen, wie Daten fließen und wann sie als gültig gelten.

Häufige Signaltypen

| Signalname | Funktion | Typisches Verhalten |

|---|---|---|

| Takt (CLK) | Synchronisationsquelle | Regelmäßiges Pulsieren zwischen 0 und 1 |

| Daten (D) | Informationsträger | Ändert den Zustand basierend auf Eingabe oder Logik |

| Aktivieren (EN) | Aktiviert ein Modul | Hoch zum Zulassen der Operation, Low zum Deaktivieren |

| Rücksetzen (RST) | Initialisiert den Zustand | Aktiv-Niedrig- oder Aktiv-Hoch-Puls am Start |

| Chip-Auswahl (CS) | Wählt ein Gerät aus | Aktiv-Niedrig, um eine spezifische Komponente anzusprechen |

Das Verständnis des aktiven Zustands von Steuersignalen ist entscheidend. Einige Signale sind aktiv hoch, was bedeutet, dass sie funktionieren, wenn die Spannung hoch ist. Andere sind aktiv niedrig, was durch einen Strich über dem Namen gekennzeichnet ist (z. B. /RESET oder RST_N), was bedeutet, dass sie funktionieren, wenn die Spannung niedrig ist.

3. Analyse von Setup- und Hold-Zeiten 🕒

Einer der wichtigsten Aspekte der Zeitanalyse beinhaltet Setup- und Hold-Zeiten. Diese Parameter definieren das Fenster, in dem die Daten stabil bezüglich einer Taktränder sein müssen. Die Verletzung dieser Einschränkungen führt zu Datenkorruption oder Metastabilität.

Setup-Zeit (tsu)

Die Setup-Zeit ist die minimale Dauer, während der die Daten stabil sein müssenvordie aktive Taktränder eintrifft. Wenn die Daten zu nahe an der Taktränder ändern, kann der Flip-Flop den korrekten Wert möglicherweise nicht erfassen.

- Anforderung:Die Daten müssen für tsuvor dem steigenden Edge stabil sein.

- Folge der Verletzung: Der Register kann falsche Daten erfassen oder in einen undefinierten Zustand gelangen.

Haltezeit (th)

Die Haltezeit ist die minimale Dauer, während der die Daten stabil bleiben müssennachder aktiven Taktkante. Der Flip-Flop benötigt einen Moment, um den Wert zu erfassen, bevor neue Daten möglicherweise eintreffen.

- Anforderung:Die Daten müssen für thnach der steigenden Flanke stabil bleiben.

- Folge einer Verletzung:Ähnlich wie Setup-Verletzungen verursacht dies Datenfehler oder Metastabilität.

Visualisierung von Setup- und Haltezeiten

Beim Lesen eines Zeitdiagramms achten Sie auf das Datenignal im Verhältnis zur Taktkante. Die Datenleitung sollte während des Setup-Fensters (vorher) und des Haltefensters (danach) flach und unverändert sein. Wenn die Datenleitung innerhalb dieser Fenster wechselt, ist das Design wahrscheinlich fehlerhaft.

4. Clock Domain Crossing ⏱️

In komplexen Systemen können verschiedene Teile der Schaltung mit unterschiedlichen Taktfrequenzen oder Taktraten arbeiten. Der Datentransfer zwischen diesen unterschiedlichen Taktdomänen wird als Clock Domain Crossing (CDC) bezeichnet. Dieser Prozess bringt erhebliche zeitliche Herausforderungen mit sich.

Arten von Taktdomänen

- Gleiche Frequenz, gleiche Phase:Synchrones Design. Einfache Zeitanalyse gilt.

- Gleiche Frequenz, unterschiedliche Phase: Erfordert Phasenabstimmungsprüfungen.

- Unterschiedliche Frequenzen: Erfordert Synchronisationstechniken wie Handshakes oder FIFO-Puffer.

Behandlung von CDC in Zeitdiagrammen

Beim Analysieren von Diagrammen mit mehreren Taktdomänen stellen Sie sicher, dass Sie die Taktsignale klar voneinander unterscheiden. Datenübertragungen von einer langsamen in eine schnelle Domäne können riskant sein, wenn sie nicht korrekt behandelt werden. Umgekehrt kann eine Übertragung von schnell zu langsam zu Datenverlust führen, wenn der Empfänger zu schnell abtastet.

- Handshake-Protokolle:Verwenden Sie gültige/bereite Signale, um die Fertigstellung der Datenübertragung zu bestätigen.

- FIFO-Puffer:Entkoppeln Sie die Produktions- und Verbrauchsrate.

- Synchronisierer: Verwenden Sie mehrstufige Flip-Flops, um das Risiko von Metastabilität zu reduzieren.

5. Synchrones vs. asynchrones Design 🔄

Die Designarchitektur bestimmt, wie Timing-Diagramme aussehen. Das Verständnis des Unterschieds hilft dabei, das Signalverhalten vorherzusagen.

Synchrones Design

Die meisten digitalen Logiken sind synchron. Alle Zustandsänderungen finden am Rand eines zentralen Taktsignals statt.

- Vorhersagbarkeit: Einfacher zu analysieren, da die Zeitsteuerung kontrolliert ist.

- Zeitdiagramme: Regelmäßige, rasterartige Muster. Datenänderungen stimmen mit Takträndern überein.

- Einschränkungen: Taktschiefe kann bei großen Designs zu Problemen führen.

Asynchrones Design

Zustandsänderungen finden aufgrund des Eintreffens von Signalen statt, nicht aufgrund eines globalen Taktsignals. Dies ist bei Handshake-Protokollen und Interrupt-Behandlung üblich.

- Flexibilität: Kann für bestimmte Aufgaben schneller sein, da nur auf Daten gewartet wird.

- Zeitdiagramme: Unregelmäßig. Signale hängen von vorherigen Ereignissen ab, nicht von festen Zeitintervallen.

- Risiken: Kann bei unsachgemäßer Gestaltung an Rennbedingungen und Gefahren leiden.

6. Häufige Fallen und Fehler ❌

Sogar erfahrene Ingenieure begehen Fehler bei der Interpretation oder Erstellung von Zeitdiagrammen. Die Aufmerksamkeit auf diese häufigen Fehler kann viel Debugging-Zeit sparen.

1. Ignorieren der Ausbreitungsverzögerung

Signale ändern sich nicht sofort. Gatter weisen eine Ausbreitungsverzögerung auf. Wenn Sie ein Diagramm zeichnen, das sofortige Änderungen annimmt, wird Ihre Simulation der Realität nicht entsprechen.

- Korrektur: Fügen Sie immer Verzögerungswerte zwischen logischen Übergängen in Ihren Diagrammen hinzu.

2. Falsche Deutung von aktiven-low-Signalen

Ein Signal mit der Bezeichnung /CS ist aktiv, wenn es niedrig ist. Wenn Sie annehmen, dass es hoch ist, wird Ihre Logik umgekehrt sein.

- Beheben: Überprüfen Sie die Datenblätter oder Schaltpläne auf die aktiven Zustände. Suchen Sie nach Bubbles an Logikgattern.

3. Übersehen von Störimpulsen

Störimpulse sind kurze, unbeabsichtigte Impulse. Sie können auftreten, wenn Signale über verschiedene Pfade mit unterschiedlichen Verzögerungen laufen.

- Beheben: Verwenden Sie gefahrenfreie Logik oder fügen Sie Filterstufen in die Schaltung ein.

4. Verwechseln von Flanke und Pegel

Einige Schaltungen werden auf der steigenden Flanke ausgelöst, andere auf der fallenden Flanke und wieder andere auf dem Pegel selbst.

- Beheben: Überprüfen Sie die Auslösebedingung in der Bauteilbeschreibung.

7. Lesen und Erstellen professioneller Diagramme 📝

Klare Kommunikation ist in der Ingenieurwissenschaft entscheidend. Ein gut gezeichnetes Zeitdiagramm vermittelt komplexe Informationen auf einen Blick. Hier sind Best Practices für ihre Erstellung.

Best Practices für die Anordnung

- Kanten ausrichten: Stellen Sie sicher, dass verwandte Signale zu konsistenten Zeitintervallen wechseln.

- Klar beschriften: Verwenden Sie Signalnamen, nicht nur generische Linien.

- Zeit markieren: Geben Sie die Dauer von Zyklen oder spezifischen Verzögerungen an.

- Signale gruppieren: Ordnen Sie verwandte Signale (wie Datenbusleitungen) zusammen.

Schritt-für-Schritt-Erstellungsprozess

- Uhrsignale identifizieren: Zeichnen Sie zuerst die Taktsignale. Sie bilden die Grundlage der Zeitsteuerung.

- Steuerungssignale hinzufügen: Platzieren Sie Enable-, Reset- und Chip-Select-Leitungen.

- Daten darstellen: Fügen Sie Datenleitungen basierend auf dem Logikfluss hinzu.

- Annotieren: Fügen Sie Notizen zu Setup-/Hold-Zeiten oder spezifischen Verzögerungen hinzu.

- Überprüfung: Auf Verstöße und logische Konsistenz prüfen.

8. Analyse von realen Szenarien 🔍

Betrachten wir ein Szenario im Zusammenhang mit einem Speicher-Lesevorgang. Dies ist eine häufige Aufgabe für Ingenieure, die mit Mikrocontrollern arbeiten.

Speicher-Lesezyklus

Beim Speicher-Lesen sendet der Prozessor eine Adresse, aktiviert eine Leseanforderung und wartet auf Daten.

- Adressbus: Gültig vor der Taktränder.

- Chip Select: Geht auf Low, um den Speicher zu aktivieren.

- Lesebefehl: Geht auf Low, um die Übertragung zu starten.

- Datenbus: Bleibt in High-Z, bis der Speicher ihn treibt.

- Zeitplanung: Die Daten müssen stabil sein, bevor der Prozessor sie abtastet.

Berücksichtigung der Signalintegrität

Mit steigender Frequenz wird die Signalintegrität zu einem entscheidenden Faktor. Reflexionen, Koppelungen und Rauschen können Wellenformen verzerren. Zeitdiagramme in Hochgeschwindigkeitsdesigns müssen diese physischen Schichten berücksichtigen.

- Anstiegsrate: Wie schnell das Signal wechselt. Zu schnell verursacht Rauschen; zu langsam führt zu Zeitverzögerungen.

- Spannungsniveaus: Stellen Sie sicher, dass die Logikschwellen bei Temperatur- und Spannungsänderungen eingehalten werden.

9. Erweiterte Zeitkonzepte 🧠

Für diejenigen, die ihr Fachwissen vertiefen möchten, erweitern mehrere fortgeschrittene Konzepte die grundlegende Zeitanalyse.

Metastabilität

Metastabilität tritt auf, wenn ein Flip-Flop innerhalb der erforderlichen Zeit nicht in einen stabilen Zustand 0 oder 1 übergehen kann. Dies geschieht meist, wenn die Daten zu nahe an der Taktränder wechseln.

- Wahrscheinlichkeit: Es handelt sich um ein wahrscheinliches Ereignis, nicht um ein deterministisches.

- Minderung: Verwenden Sie Synchronisierketten (mehrere Flip-Flops in Reihe), um die Wahrscheinlichkeit auf nahezu null zu reduzieren.

Taktschiefe

Taktschiefe ist die Differenz in den Ankunftszeiten des Taktsignals an verschiedenen Teilen der Schaltung. Positive Schiefe (ankommt später) kann die Setup-Zeit unterstützen, aber die Hold-Zeit beeinträchtigen. Negative Schiefe hat das Gegenteil zur Folge.

- Auswirkungen auf das Design:Schiefe muss in den Zeitbudgets berücksichtigt werden.

- Messung:Verwenden Sie Oszilloskope oder Simulationswerkzeuge, um die Schiefe zu messen.

Jitter

Jitter ist die Abweichung der Taktränder von ihrer idealen Position. Er verringert die effektiven Setup- und Hold-Margen.

- Arten:Periodenjitter, Zyklus-zu-Zyklus-Jitter und zufälliger Jitter.

- Auswirkungen:Hoher Jitter begrenzt die maximale Betriebsfrequenz eines Systems.

10. Werkzeuge und Methoden 🛠️

Während die manuelle Analyse lehrreich ist, stützt sich die moderne Ingenieurarbeit auf Werkzeuge. Doch das Verständnis der zugrundeliegenden Theorie ermöglicht es Ihnen, diese Werkzeuge effektiv einzusetzen.

Simulationssoftware

Hardware-Beschreibungssprachen (HDL) ermöglichen die Simulation. Diese Werkzeuge generieren automatisch Zeitdiagramme aus dem Code. Sie müssen die Ausgabe verstehen, um die Richtigkeit des Codes zu überprüfen.

Statische Zeitanalyse (STA)

STA-Werkzeuge überprüfen mathematisch, ob alle Pfade die Zeitvorgaben erfüllen, ohne Simulation. Sie prüfen Setup- und Hold-Verstöße über alle Betriebsbedingungen (Temperatur, Spannung).

Debugging mit Logikanalysatoren

Hardware-Debugger erfassen echte Signale von einer Platine. Sie zeigen Zeitdiagramme an, die der Realität entsprechen, und helfen dabei, physische Schichtenprobleme zu erkennen, die die Simulation übersehen könnte.

Fazit 🏁

Zeitdiagramme sind die Sprache des Verhaltens digitaler Signale. Sie schließen die Lücke zwischen abstraktem Logik und physischer Realität. Für Ingenieurstudierende lohnt sich die Investition in die Beherrschung dieser Techniken über die gesamte Karriere hinweg. Egal, ob Sie einen einfachen Zähler oder einen komplexen Prozessor entwerfen, die Fähigkeit, Zeitbedingungen zu lesen und zu analysieren, ist unverzichtbar.

Durch die Fokussierung auf Setup- und Hold-Zeiten, das Verständnis von Taktdomänen und die Vermeidung häufiger Fehler bauen Sie eine solide Grundlage auf. Denken Sie daran, stets aktive Zustände zu überprüfen und Propagationsverzögerungen zu berücksichtigen. Während Sie Fortschritte machen, werden Sie komplexere Szenarien kennenlernen, aber die grundlegenden Prinzipien bleiben gleich. Üben Sie weiterhin die Diagrammanalyse, und Ihre Entwürfe werden zuverlässiger und effizienter.

Verfeinern Sie Ihre Fähigkeiten weiterhin durch das Studium von Datenblättern und die Analyse von realen Schaltungs-Signalformen. Das Feld der digitalen Ingenieurwissenschaft entwickelt sich schnell, aber die Grundlagen der Zeitanalyse bleiben unverändert.