Zeitdiagramme sind die Grundlage der digitalen Systemgestaltung. Sie fungieren als visueller Vertrag zwischen Logik, Hardware und Software und definieren genau, zu welchem Zeitpunkt Signale ihren Zustand ändern sollten. Trotz ihrer Verbreitung in der Ingenieurwelt besteht jedoch ein anhaltender Missstand hinsichtlich der Erstellung, Interpretation und Nutzung dieser Diagramme. Viele Fachleute betrachten sie als statische Abbildungen, anstatt als dynamische Darstellungen des Systemverhaltens.

Dieser Leitfaden zielt darauf ab, Klarheit zu schaffen. Wir werden verbreitete Missverständnisse analysieren, die technischen Realitäten der Signalpropagation untersuchen und ein Rahmenwerk für die Erstellung genauer Zeitdiagrammdokumentation aufbauen. Indem wir Tatsachen von Fiktion trennen, können Ingenieure die Fehlersuche verkürzen und die Systemzuverlässigkeit verbessern.

Was ist ein Zeitdiagramm? 🤔

Ein Zeitdiagramm ist eine grafische Darstellung des Verhaltens von Signalen in einer digitalen Schaltung über die Zeit. Im Gegensatz zu einer Schaltungszeichnung, die die Verbindungen zeigt, verdeutlicht ein Zeitdiagramm Kausalität und zeitliche Beziehungen. Es stellt Signalpegel (hoch, niedrig oder schwimmend) entlang einer Zeitachse dar, sodass Designer überprüfen können, ob Daten zum richtigen Zeitpunkt stabil sind.

Zu den wesentlichen Merkmalen gehören:

- Zeitachse: Sie verläuft typischerweise horizontal und stellt den Ablauf von Ereignissen dar.

- Signalleitungen: Vertikale Linien, die spezifische Leitungen, Bussysteme oder Logikzustände darstellen.

- Kanten: Übergänge von niedrig nach hoch (steigend) oder von hoch nach niedrig (fallend).

- Beschriftungen: Anmerkungen, die Setup-Zeiten, Haltezeiten oder Verzögerungen anzeigen.

Ohne ein klares Verständnis dieser Komponenten wird das Diagramm eher zur Quelle der Verwirrung als zur Klarheit.

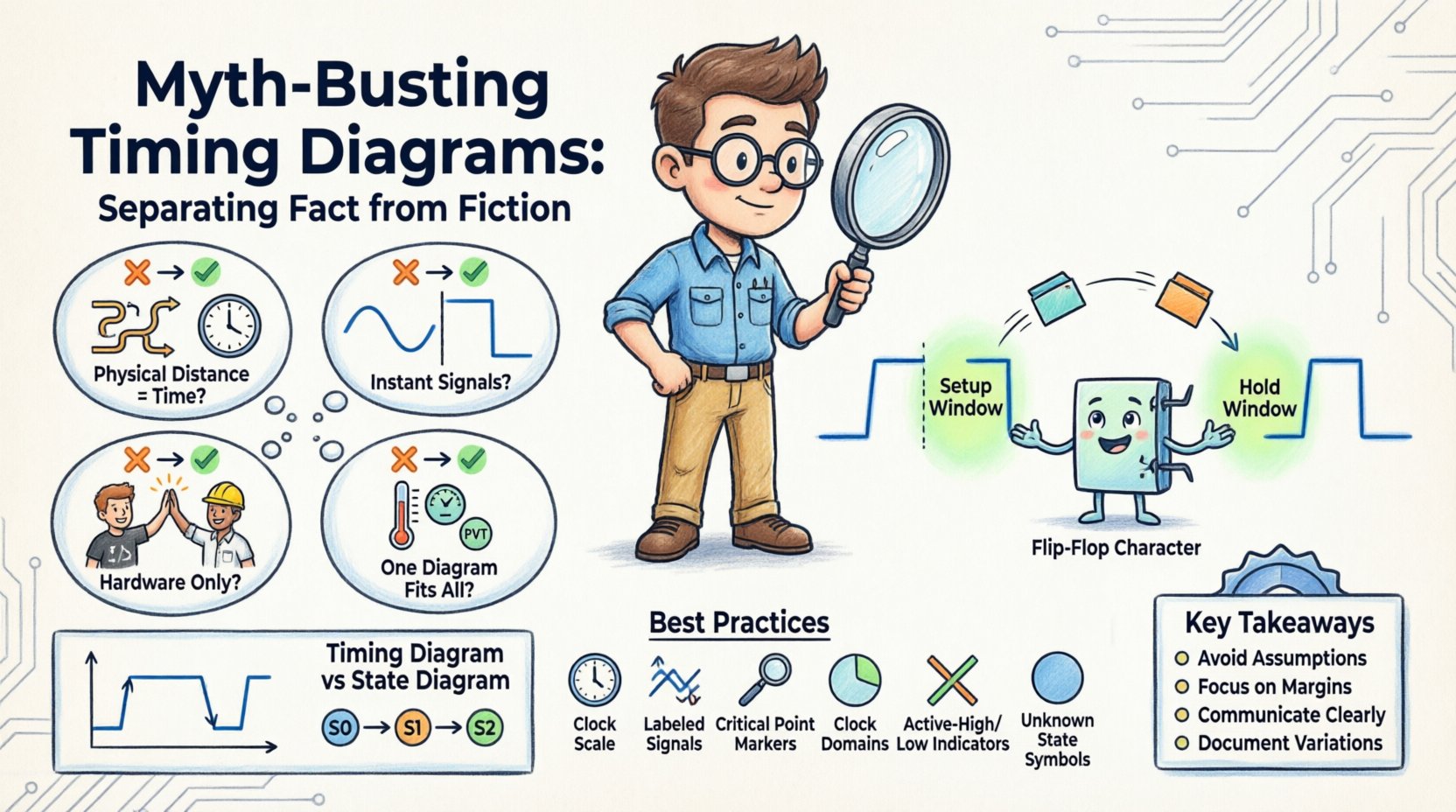

Häufige Mythen über Zeitdiagramme 🚫

Um die Designqualität zu verbessern, müssen wir zunächst die falschen Überzeugungen identifizieren, die zu Fehlern führen. Nachfolgend finden Sie die verbreitetsten Mythen, die in technischen Kreisen kursieren.

Mythos 1: Zeitdiagramme zeigen exakte physikalische Distanz 📏

Die Fiktion: Ingenieure nehmen oft an, dass der horizontale Abstand zwischen zwei Kanten in einem Diagramm direkt mit der physikalischen Spuränge auf einer Leiterplatte korreliert.

Die Wahrheit:Zeitdiagramme stellen logische oder elektrische Zeit dar, nicht physischen Raum. Obwohl die Spuränge die Propagationsverzögerung beeinflusst, konzentriert sich das Diagramm auf das Ergebnis dieser Verzögerung, nicht an der Geometrie selbst. Eine Verzögerung von 1 Nanosekunde könnte einer 15 cm langen Spur auf einer FR4-Platine oder einer 10 cm langen Kupferleitung mit unterschiedlichen Dielektrizitätskonstanten entsprechen. Das Diagramm abstrahiert das physikalische Medium, um sich auf das Zeitfenster zu konzentrieren.

- Die physikalische Länge bestimmt die Verzögerung, aber das Diagramm zeigt den Verzögerungswert.

- Die Routing-Komplexität bleibt verborgen; nur das Endergebnis ist relevant.

- Die Annahme eines 1:1-Verhältnisses zwischen Zeit und Distanz führt zu Layout-Fehlern.

Mythos 2: Signale überspringen ihre Übergänge sofort ⚡

Die Fiktion: In vielen Diagrammen zeigen senkrechte Linien an, dass ein Signal sofort seinen Zustand wechselt.

Die Tatsache:Kein physikalisches Signal ändert seinen Zustand sofort. Es gibt immer eine Anstiegszeit und eine Abfallzeit. Wenn ein Diagramm eine vertikale Kante zeigt, stellt er eine Übergangsdauer dar, die relativ zur Taktfrequenz schnell ist, aber nicht null. Das Ignorieren von Übergangszeiten kann zu Problemen mit der Signalintegrität führen, wie zum Beispiel Ringing oder Crosstalk, die in idealisierten Diagrammen nicht sichtbar sind.

- Die Anstiegszeit ist die Dauer, um von 10 % auf 90 % der Spannung zu wechseln.

- Diagramme vereinfachen dies oft zur besseren Lesbarkeit, aber die Simulation muss dies berücksichtigen.

- Hochgeschwindigkeitsentwürfe erfordern eine explizite Modellierung der Übergangsgeschwindigkeiten.

Mythos 3: Zeitdiagramme dienen nur Hardware-Ingenieuren 🛠️

Die Fiktion:Softwareentwickler und Systemarchitekten ignorieren Zeitdiagramme oft, da sie annehmen, dass sie für die Code-Logik irrelevant sind.

Die Tatsache:Die Software muss den Hardware-Zeitvorgaben folgen. Unterbrechungen, DMA-Übertragungen und speicherabgeleitete E/A-Operationen hängen alle von der durch die Hardware festgelegten Zeitplanung ab. Wenn ein Treiber versucht, Daten zu lesen, bevor die Hardware das „Ready“-Signal setzt, tritt ein Busfehler auf. Zeitdiagramme sind für die Kommunikation zwischen Fachgebieten unerlässlich.

- Software-Unterbrechungen müssen mit den Hardware-Taktkreisen synchronisiert sein.

- Die Zugriffszeiträume für den Speicher werden durch Zeitvorgaben definiert.

- Sowohl Hardware- als auch Software-Teams benötigen ein gemeinsames Verständnis der Zeitachse.

Mythos 4: Ein Diagramm passt für alle Kontexte 🌍

Die Fiktion:Ein einziges Zeitdiagramm kann ein gesamtes System beschreiben, unabhängig von den Betriebsbedingungen.

Die Tatsache:Die Zeitplanung variiert mit Temperatur, Spannung und Prozessvariationen (PVT). Ein Diagramm, das für Nennbedingungen erstellt wurde, kann an den Extremen versagen. Designer müssen die ungünstigsten Szenarien berücksichtigen. Ein Diagramm, das das Best-Case-Verhalten zeigt, ist oft weniger nützlich als eines, das die Betriebsgrenzen hervorhebt.

- Die ungünstigste Verzögerung bestimmt die minimale Taktfrequenz.

- Die Temperatur beeinflusst Widerstand und Kapazität.

- Prozessvariationen verändern die Schaltgeschwindigkeit der Transistoren.

Tiefgang: Setup- und Hold-Zeiten ⏱️

Das Verständnis von Zeitverletzungen ist entscheidend. Zwei spezifische Konzepte dominieren die Analyse der Datenintegrität: Setup-Zeit und Hold-Zeit. Diese sind oft die Ursache für die schwierigsten Fehler in digitalen Systemen.

Setup-Zeit (Tsu)

Die Setup-Zeit ist die minimale Zeitspanne, voreinem Taktrand, innerhalb derer die Daten stabil sein müssen. Wenn die Daten zu nahe am Taktrand ändern, kann der empfangende Flip-Flop den korrekten Wert nicht erfassen.

- Es stellt sicher, dass die Daten stabil sind, bevor sich das Erfassungsfenster schließt.

- Verstöße verursachen Metastabilität oder falsche Logikzustände.

- Die Pfadverzögerung muss kleiner als die Taktklasse minus die Setup-Zeit sein.

Haltezeit (Th)

Die Haltezeit ist die minimale Zeitspanne, in dernacheinem Taktflankensignal, während der Daten stabil bleiben müssen. Wenn die Daten zu früh nach der Taktflanke wechseln, kann der Flip-Flop den zuvor erfassten Wert verlieren.

- Es stellt sicher, dass die Daten lange genug stabil bleiben, um erfasst zu werden.

- Verstöße sind oft schwerer zu beheben als Setup-Verstöße.

- Die Pfadverzögerung muss größer als die Anforderung an die Haltezeit sein.

Zeitverletzungsszenarien

Beim Analysieren eines Zeitdiagramms achten Sie auf folgende Muster:

- Setup-Verstoß: Das Datensignal ändert sich noch, wenn die Taktflanke eintrifft.

- Halte-Verstoß: Das Datensignal ändert sich unmittelbar nach der Taktflanke.

- Glitch: Ein kurzer Impuls, der innerhalb des Setup-/Haltefensters liegt, aber kein gültiger Übergang ist.

Zeitdiagramm gegenüber Zustandsdiagramm 🔄

Verwirrung entsteht oft zwischen Zeitdiagrammen und Zustandsdiagrammen. Obwohl beide das Systemverhalten beschreiben, beantworten sie unterschiedliche Fragen. Ein Zustandsdiagramm zeigtwasdas System tut (Logikablauf), während ein Zeitdiagramm zeigtwannes geschieht (zeitlicher Ablauf).

| Funktion | Zeitdiagramm | Zustandsdiagramm |

|---|---|---|

| Hauptaugenmerk | Zeit und Signalpegel | Logik und Steuerfluss |

| Achsen-Darstellung | Horizontal = Zeit | Horizontal = Logische Zustände |

| Empfohlen für | Signaltreue, Synchronisation | Algorithmus-Entwurf, FSM-Logik |

| Komplexität | Hohe zeitliche Auflösung | Hohe logische Verzweigung |

| Signal-Detail | Zeigt Spannungsniveaus (Hoch/Niedrig) an | Zeigt abstrakte Zustände (Warten/Lauf) an |

Die Verwendung des richtigen Diagramms für die Aufgabe verhindert Missverständnisse. Ein Zustandsautomat kann ohne ein Zeitdiagramm entworfen werden, aber eine Hochgeschwindigkeits-Bus-Schnittstelle nicht.

Beste Praktiken zur Erstellung genauer Diagramme ✅

Um sicherzustellen, dass Ihre Dokumentation wirksam ist, befolgen Sie diese Richtlinien. Präzision in der Dokumentation reduziert Mehrdeutigkeiten bei der Implementierung.

- Zeitskala definieren: Geben Sie immer die Einheiten an (ns, µs, Takte). Wenn Takte verwendet werden, definieren Sie die Taktfrequenz.

- Jedes Signal beschriften: Verwenden Sie keine generischen Namen wie „Signal 1“. Verwenden Sie beschreibende Namen wie „CLK_IN“ oder „DATA_VALID“.

- Kritische Punkte markieren: Markieren Sie Setup- und Hold-Zeiträume explizit durch Schattierung oder Anmerkungen.

- Taktdomänen einbeziehen: Wenn mehrere Takte existieren, unterscheiden Sie sie deutlich. Zeigen Sie die Beziehung zwischen asynchronen Taktquellen, falls zutreffend, an.

- Aktiven Zustand Hoch/Niedrig anzeigen: Klären Sie, ob ein aktiver Zustand Hoch (1) oder Niedrig (0) ist, um Polarity-Fehler zu vermeiden.

- Unbekannte Zustände anzeigen: Verwenden Sie X oder Z, um undefinierte oder hochimpedanzige Zustände darzustellen, anstatt sie leer zu lassen.

Umgang mit asynchronen Signalen 🔄

Einer der anspruchsvollsten Aspekte von Zeitdiagrammen ist der Umgang mit asynchronen Signalen. Dies sind Signale, die nicht mit dem Haupttakt des Systems synchronisiert sind. Sie führen Unsicherheit ein, die beherrscht werden muss.

- Metastabilität: Wenn ein asynchrones Signal nahe einer Taktränder ankommt, kann der Flip-Flop in einen metastabilen Zustand geraten. Er wird letztendlich entweder auf 0 oder 1 auflösen, aber die dafür benötigte Zeit ist unvorhersehbar.

- Synchronisierer: Verwenden Sie Ketten von Flip-Flops, um die Metastabilität zu lösen. Zeitdiagramme sollten zeigen, dass sich der metastabile Bereich vor der nächsten Taktränder auflöst.

- Handshake: Protokolle wie I2C oder SPI verwenden asynchrone Handshakes. Das Zeitdiagramm muss die Wartezeiten zeigen, in denen der Master auf den Slave wartet.

Praxisanwendung: Debuggen einer Rennbedingung 🐞

Stellen Sie sich eine Situation vor, bei der ein Datenbus nicht korrekt gelesen wird. Das System hängt gelegentlich. Eine Analyse des Zeitdiagramms bringt das Problem ans Licht.

- Beobachtung: Das „Ready“-Signal wird leicht nach dem „Read“-Strobe aktiviert.

- Diagrammprüfung: Das Zeitdiagramm zeigt, dass die „Ready“-Kante innerhalb des Setup-Fensters des „Read“-Strobos fällt.

- Schlussfolgerung: Die Daten werden gelesen, bevor sie gültig sind.

- Lösung: Passen Sie die Logik an, um das „Read“-Strobe zu verzögern oder die „Ready“-Pulsbreite zu verlängern.

Dieses Beispiel zeigt, warum die Visualisierung der Zeitachse entscheidend ist. Ohne das Diagramm bleibt die Rennbedingung in der Code-Logik verborgen.

Werkzeuge und Analysemethoden 🔍

Während spezifische Softwarenamen nicht im Fokus stehen, bleiben die Analysemethoden konstant. Moderne Ingenieurarbeit stützt sich auf Simulationen und Wellenform-Viewer, um Zeitdiagramme zu validieren.

- Simulation: Führen Sie Testbenchs aus, um Wellenformen zu generieren, die dem Entwurfsziel entsprechen.

- Statische Zeitanalyse (STA): Berechnen Sie Verzögerungen ohne Simulation, um Verstöße über alle Pfade hinweg zu überprüfen.

- Hardware-Debugging: Verwenden Sie Oszilloskope, um echte Wellenformen aus der Praxis zu erfassen und mit dem theoretischen Diagramm zu vergleichen.

- Versionskontrolle: Halten Sie Zeitdiagramme in der Versionskontrolle. Änderungen in der Hardware erfordern oft Aktualisierungen der Zeitvorgaben.

Die Auswirkungen von Jitter und Skew 📉

Zeitdiagramme werden oft mit perfekten, geraden Linien gezeichnet. Die Realität ist unordentlicher. Jitter und Skew sind Störquellen, die die Zeitgenauigkeit beeinflussen.

- Jitter: Schwankungen in der Zeitpunkte der Signalflanken. Taktschwankungen verursachen eine Verschiebung des Abtastfensters.

- S Verzögerung: Der Unterschied in der Ankunftszeit des gleichen Taktsignals an verschiedenen Stellen der Schaltung.

- Auswirkung: Beide verringern die Zeitmarge. Ein Zeitverlaufsschema sollte idealerweise die Marge zeigen, nicht nur die ideale Flanke.

Zusammenfassung der wichtigsten Erkenntnisse 📝

Zeitverlaufsschemata sind mehr als nur Zeichnungen; sie sind Spezifikationen des Verhaltens. Indem Ingenieure die Mythen und Fakten um sie herum verstehen, können sie robusteren Systemen entwerfen.

- Vermeide Annahmen: Nehme keine sofortigen Übergänge oder perfekte Synchronisation an.

- Konzentriere dich auf die Sicherheitsmargen: Setup- und Hold-Zeiten sind die Sicherheitspuffer, die Versagen verhindern.

- Kommuniziere klar: Verwende Diagramme, um die Kluft zwischen Hardware- und Software-Teams zu überbrücken.

- Dokumentiere Variationen: Anerkenne, dass die Zeitverläufe sich mit Umgebung und Prozess ändern.

Wenn du ein Zeitverlaufsschema betrachtest, sieh die Zeit. Sieh die Einschränkungen. Sieh die Zuverlässigkeit. Diese Perspektive verwandelt ein statisches Bild in ein mächtiges Werkzeug für ingenieurwissenschaftliche Exzellenz.