Zeitdiagramme sind die Grundlage der digitalen Systemgestaltung. Sie bieten eine visuelle Sprache, die Ingenieure verwenden, um zu beschreiben, wie Signale im Laufe der Zeit wechseln. Egal, ob Sie eine Mikrocontroller-Schnittstelle entwerfen oder einen Kommunikationsprotokoll-Debugging durchführen, das Verständnis dieser Diagramme ist unerlässlich. Diese Anleitung führt Sie Schritt für Schritt durch den Prozess der Erstellung und Interpretation ohne unnötige Komplexität.

Der Einstieg mag einschüchternd wirken, aber mit dem richtigen Rahmen können Sie effektive Diagramme schnell zeichnen. Wir behandeln die zentralen Komponenten, die Logik hinter Signalübergängen und die entscheidenden Parameter, die die Systemzuverlässigkeit definieren. Lassen Sie uns in die Mechanik der Signalzeitgestaltung eintauchen.

Verständnis des Kernzwecks 🧠

Ein Zeitdiagramm ist eine grafische Darstellung der Abfolge von Ereignissen in einem System. Es stellt den Zustand von Signalen entlang einer gemeinsamen Zeitachse dar. Im Gegensatz zu Schaltplänen, die physische Verbindungen zeigen, konzentrieren sich Zeitdiagramme auf zeitliche Beziehungen. Diese Unterscheidung ist entscheidend für das Debuggen von Logikfehlern, die bei statischer Schaltungsanalyse nicht sichtbar werden.

Wenn Sie diese Diagramme zeichnen, dokumentieren Sie das Verhalten von Daten- und Steuersignalen. Ziel ist es sicherzustellen, dass ein Signal bereit ist, bevor ein anderes darauf reagiert. Diese Synchronisation verhindert Datenkorruption und gewährleistet eine stabile Funktion.

-

Visuelle Klarheit: Sie machen abstrakte zeitliche Abhängigkeiten konkret.

-

Debugging-Hilfe: Sie heben Rennbedingungen und Setup-Verstöße hervor.

-

Dokumentation: Sie dienen als Referenz für Hardware- und Software-Teams.

-

Verifikation: Sie helfen dabei, zu überprüfen, ob die Logik der Spezifikation entspricht.

Ohne ein klares Diagramm ist es leicht, subtile Zeitprobleme zu übersehen, die nur unter bestimmten Bedingungen auftreten. Durch die Standardisierung Ihrer Zeichnungsweise verringern Sie die Mehrdeutigkeit für alle Beteiligten am Projekt.

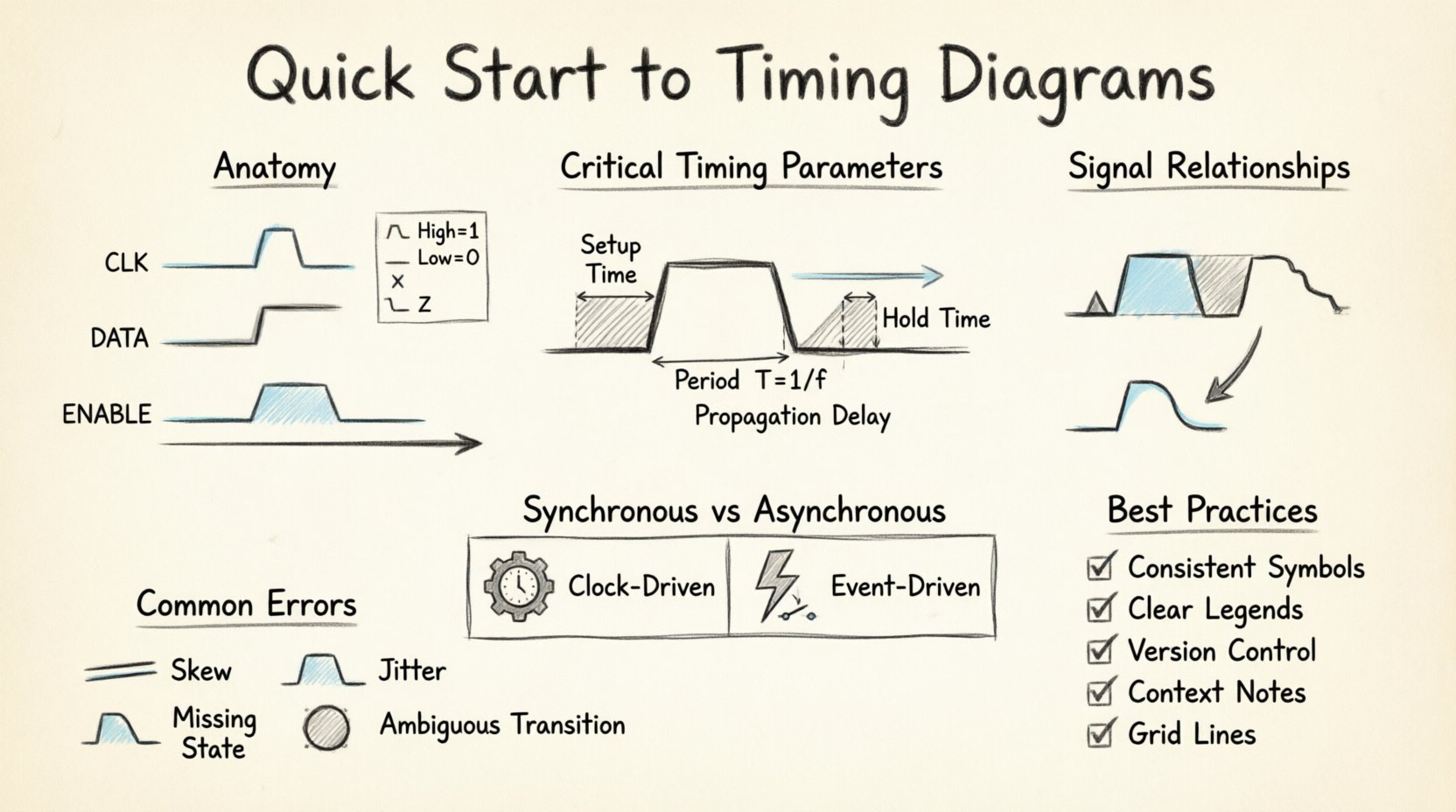

Anatomie eines Zeitdiagramms 📐

Jedes Zeitdiagramm teilt eine gemeinsame Struktur. Die Beherrschung dieser Struktur ermöglicht es Ihnen, komplexe Wellenformen leicht zu lesen. Die Anordnung ist in verschiedenen ingenieurwissenschaftlichen Disziplinen konsistent, von eingebetteten Systemen bis hin zu Hochgeschwindigkeitsnetzwerken.

1. Die Zeitachse ⏰

Die horizontale Achse stellt die Zeit dar. Sie fließt von links nach rechts. Die Zeit ist in jedem Kontext nicht immer linear, aber in den meisten Standarddiagrammen entsprechen gleiche Abstände gleichen Zeitintervallen. Sie müssen nicht jede Millisekunde beschriften, aber die Markierung wichtiger Intervalle hilft, die Informationen zu skalieren.

-

Richtung:Immer von links nach rechts.

-

Skala:Kann je nach Signalfrequenz linear oder logarithmisch sein.

-

Markierungen:Verwenden Sie senkrechte Linien, um spezifische Ereignisse wie Taktflanken zu kennzeichnen.

2. Die Signalleitungen 📊

Signale werden durch horizontal übereinander gestellte Linien dargestellt. Jede Linie entspricht einem bestimmten Draht oder einer bestimmten Leitung im Schaltkreis. Der Name des Signals erscheint gewöhnlich auf der linken oder rechten Seite der Linie.

-

Gruppierung:Verwandte Signale, wie Adress- und Datenleitungen, werden oft zusammengefasst.

-

Beschriftung:Markieren Sie Signale immer deutlich, um Verwechslungen zwischen ähnlichen Namen zu vermeiden.

-

Reihenfolge:Stellen Sie das bedeutendste Signal je nach Konvention oben oder unten ab.

3. Logische Pegel 🔋

Signale wechseln zwischen definierten Zuständen. In der digitalen Logik sind dies typischerweise High und Low, oder 1 und 0. Die vertikale Position der Linie zeigt den Zustand an.

|

Zustand |

Häufige Bezeichnung |

Physische Bedeutung |

|---|---|---|

|

High |

1, H, VCC |

Positiver Spannungsversorgungsleiter |

|

Low |

0, L, GND |

Masse oder Nullspannung |

|

Unbekannt |

X |

Unbestimmter Zustand |

|

Hochimpedanz |

Z |

Getrennt oder schwimmend |

Das Verständnis dieser Pegel ist der erste Schritt beim Lesen des Diagramms. Die Übergänge zwischen diesen Pegeln sind der Ort, an dem die Aktion stattfindet.

Kritische Zeitparameter ⚙️

Zeitplanung geht nicht nur darum, Linien zu zeichnen; es geht darum, Einschränkungen zu definieren. Bestimmte Parameter bestimmen, wie schnell ein Signal wechseln kann und wann es stabil sein muss. Diese Einschränkungen sind entscheidend dafür, dass das System korrekt funktioniert.

1. Setup-Zeit ⏳

Die Setup-Zeit ist die minimale Zeitspanne, die ein Datensignal stabil sein muss, bevor ein Taktrand eintritt. Wenn sich die Daten zu nahe am Taktrand ändern, kann das System den falschen Wert erfassen. Dies ist eine kritische Einschränkung in synchronen Systemen.

-

Definition:Zeit vor dem aktiven Taktrand.

-

Verletzung:Verursacht Metastabilität oder falsche Datenerfassung.

-

Entwurfsregel: Stellen Sie sicher, dass die Daten lange vor dem Auslösen des Takts stabil sind.

2. Haltezeit ⏳

Die Haltezeit ist die minimale Zeitspanne, während der ein Datensignal nach dem Taktkante stabil bleiben muss. Wenn das Signal zu früh nach dem Auslösen wechselt, könnte das empfangende Element den Wert möglicherweise nicht korrekt erfassen.

-

Definition:Zeit nach der aktiven Taktkante.

-

Verletzung: Ähnlich wie die Setup-Zeit führt dies zu Datenfehlern.

-

Entwurfsregel: Stellen Sie sicher, dass das Signal unmittelbar nach dem Takt nicht wechselt.

3. Propagationsverzögerung ⏱️

Die Propagationsverzögerung ist die Zeit, die ein Signal benötigt, um vom Eingang eines Bauelements zum Ausgang zu gelangen. Kein elektronisches Bauelement arbeitet sofort. Diese Verzögerung addiert sich über mehrere Stufen und muss bei Hochgeschwindigkeitsentwürfen berücksichtigt werden.

-

Quelle:Interne Gatterverzögerungen und Leiterbahnlänge.

-

Auswirkung: Begrenzt die maximale Betriebsfrequenz.

-

Messung:Gemessen vom 50 %-Punkt des Eingangs zum 50 %-Punkt des Ausgangs.

4. Periode und Frequenz 🔁

Bei Taktsignalen ist die Periode die Zeit zwischen zwei aufeinanderfolgenden identischen Punkten der Wellenform (z. B. steigende Flanke bis steigende Flanke). Die Frequenz ist der Kehrwert der Periode.

-

Periode: T = 1 / f

-

Tastverhältnis:Prozentsatz der Zeit, in der das Signal innerhalb einer Periode hoch ist.

-

Stabilität: Taktschwankungen beeinflussen die Genauigkeit der Zeitsteuerung.

Signalbeziehungen ablesen und analysieren 🔄

Sobald Sie die Komponenten verstehen, ist der nächste Schritt die Analyse der Wechselwirkung zwischen Signalen. Hier wird das Diagramm zu einem Diagnosewerkzeug. Sie suchen nach Abhängigkeiten und möglichen Konflikten.

1. Flankenauslöseverhalten 📉

Die meisten digitalen Schaltungen werden auf bestimmten Flanken des Takts ausgelöst. Einige reagieren auf die steigende Flanke, andere auf die fallende Flanke. Sie müssen identifizieren, welche Flanke für jedes Bauelement in Ihrem System aktiv ist.

-

Steigende Flanke:Übergang von niedrig nach hoch.

-

Fallende Flanke:Übergang von hoch nach niedrig.

-

Beide Flanken:Einige Systeme erfassen Daten bei beiden Übergängen.

Verwenden Sie beim Zeichnen kleine Dreiecke oder Kerben, um anzuzeigen, welche Flanke aktiv ist. Dies vermeidet Verwirrung bei der Implementierung.

2. Gültige Datenfenster 🕒

Daten sind nur innerhalb eines bestimmten Fensters gültig. Vor der Setup-Zeit und nach der Hold-Zeit darf die Datenleitung nicht wechseln. Außerhalb dieses Fensters gelten die Daten als gültig. Die Markierung dieses Fensters in Ihrer Darstellung klärt die Erwartungen.

-

Fenster:Bestimmt durch Setup + Hold + Propagierungsverzögerung.

-

Verletzung:Wenn sich die Daten außerhalb dieses Fensters ändern, treten Fehler auf.

-

Visueller Hinweis:Verwenden Sie schraffierte Bereiche, um gültige Datenperioden hervorzuheben.

3. Asynchrone Signale 📡

Nicht alle Signale folgen dem Takt. Asynchrone Signale wie Unterbrechungen oder Zurücksetzungen arbeiten unabhängig. Sie erfordern eine sorgfältige Behandlung in Zeitdiagrammen, um ihre Priorität und Verzögerung zu zeigen.

-

Priorität:Unterbrechungen haben oft Vorrang vor Taktzyklen.

-

Verzögerung:Beachten Sie die Verzögerung zwischen Aktivierung und Antwort.

-

Stabilität:Stellen Sie sicher, dass asynchrone Signale für die Setup-/Hold-Anforderungen stabil sind.

Synchron vs. asynchron Systeme 📡

Der Unterschied zwischen synchroner und asynchroner Gestaltung beeinflusst, wie Sie Ihre Diagramme aufbauen. Jeder Ansatz hat spezifische Regeln und Konventionen.

|

Merkmale |

Synchron |

Asynchron |

|---|---|---|

|

Steuerung |

Gesteuert durch einen Takt |

Gesteuert durch Ereignisse |

|

Vorhersage |

Leicht vorhersehbare Zeitsteuerung |

Schwieriger vorhersehbare Zeitsteuerung |

|

Komplexität |

Standardisierte Logik |

Handshake-Protokolle |

|

Leistung |

Höher aufgrund des Taktsignals |

Oft niedriger |

In einem synchronen Diagramm sehen Sie eine dominierende Taktsignalleitung, die alle anderen Signale ausrichtet. In einem asynchronen Diagramm sehen Sie Handshakes und Wartezeiten. Beide erfordern eine präzise Zeitsteuerungs-Dokumentation.

Häufige Fehler und wie man sie vermeidet ⚠️

Fehler in Zeitdiagrammen können zu kostspieligen Hardware-Revisionen führen. Die Kenntnis häufiger Fallstricke hilft Ihnen, sauberere und genauere Darstellungen zu erstellen.

1. Ignorieren der Verzögerungsdifferenz 📏

Verzögerungsdifferenz ist der Unterschied in der Ankunftszeit eines Signals an verschiedenen Punkten. Wenn Sie annehmen, dass alle Signale gleichzeitig eintreffen, könnten Sie Zeitverletzungen übersehen. Berücksichtigen Sie immer die Kabelänge und Lastunterschiede.

-

Prüfen:Vergleichen Sie die Ankunftszeiten bei verschiedenen Empfängern.

-

Beheben:Fügen Sie Verzögerungspuffer hinzu oder passen Sie die Spurenlängen an.

-

Visuell:Zeigen Sie geringfügige Verschiebungen bei parallelen Linien, wenn die Verzögerungsdifferenz signifikant ist.

2. Übersehen von Jitter ⚡

Jitter ist die Variation in der Zeitsteuerung eines Signals. Ein Takt kann nicht perfekt periodisch sein. Bei Hochgeschwindigkeitsdesigns kann Jitter Ihre Zeitabstände aufzehren. Stellen Sie Jitter als schraffierte Fläche um die Taktkante dar.

-

Quelle:Störungen der Stromversorgung oder externe Störungen.

-

Auswirkung:Verringert die effektive Setup- und Hold-Zeit.

-

Visuell:Verwenden Sie verschwommene Linien oder Bänder, um Unsicherheiten anzuzeigen.

3. Mehrdeutige Übergänge 🔄

Ein Übergang, der wie eine gerade Linie aussieht, könnte tatsächlich eine Steigung sein. Reale Signale ändern sich nicht sofort. Die Zeichnung perfekt vertikaler Linien impliziert unendliche Geschwindigkeit, was physikalisch unmöglich ist.

-

Best Practice: Zeichnen Sie Übergänge mit einer leichten Neigung, wenn Präzision erforderlich ist.

-

Konvention:Vertikale Linien sind für die logische Darstellung akzeptabel.

-

Klarheit:Stellen Sie sicher, dass die Absicht unabhängig von der Neigung klar ist.

4. Fehlende Zustandsübergänge 🚦

Komplexe Zustandsmaschinen haben oft Zwischenzustände, die nicht offensichtlich sind. Zeichnen Sie nur Start- und Endzustände, verlieren Sie kritische Informationen über die Reihenfolge.

-

Detail:Zeigen Sie alle relevanten Zustandsänderungen.

-

Beschriftungen:Beschreiben Sie Zustände mit ihren Namen oder Werten.

-

Logik:Stellen Sie sicher, dass das Diagramm den tatsächlichen Logikfluss widerspiegelt.

Best Practices für die Dokumentation 📝

Um sicherzustellen, dass Ihre Diagramme jahrelang nützlich sind, beachten Sie einen konsistenten Stil. Dadurch werden sie einfacher zu pflegen und mit anderen Ingenieuren zu teilen.

-

Konsistente Symbole:Verwenden Sie durchgehend die gleichen Pfeilspitzen und Linienstile.

-

Klare Legenden:Definieren Sie alle verwendeten benutzerdefinierten Symbole oder Abkürzungen.

-

Versionskontrolle:Beschreiben Sie Diagramme mit Versionsnummern und Daten.

-

Zusammenhang:Fügen Sie eine kurze Beschreibung des dargestellten Systems hinzu.

-

Rasterlinien:Verwenden Sie ein Raster, um Signale auszurichten und Zeitintervalle zu markieren.

Konsistenz verringert die kognitive Belastung für jeden, der Ihre Arbeit liest. Sie erleichtert auch das Erkennen von Anomalien, wenn Sie das Diagramm später überprüfen.

Störungsbehebung mit Zeitverlaufsanalyse 🛠️

Wenn ein System ausfällt, sind Zeitverlaufsdiagramme oft der erste Ort, an dem man nachschauen sollte. Sie helfen dabei, festzustellen, ob das Problem logisch oder zeitlich bedingt ist.

1. Erkennen von Rennbedingungen 🏁

Eine Rennbedingung tritt auf, wenn die Ausgabe von der Reihenfolge der Ereignisse abhängt. Wenn zwei Signale gleichzeitig an einem Gatter ankommen, kann das Ergebnis unvorhersehbar sein. Zeitdiagramme zeigen diese Überlappungen auf.

-

Suchen Sie nach: Signale, die gleichzeitig kreuzen.

-

Lösung: Puffer hinzufügen oder die Logik neu anordnen.

-

Verhinderung: Mit Puffern gestalten, um gleichzeitige Übergänge zu vermeiden.

2. Erkennen von Störimpulsen ⚡

Störimpulse sind kurze Pulse, die aufgrund von Ausbreitungsverzögerungen auftreten. Sie könnten einen Flip-Flop unbeabsichtigt auslösen. In einem Diagramm erscheinen sie als schmale Spitzen zwischen stabilen Pegeln.

-

Visuell: Schmale Pulse, die nicht der Taktfrequenz entsprechen.

-

Behebung: Filtern verwenden oder das Signal am stabilen Edge sperren.

-

Analyse: Prüfen, ob die Pulslänge die Haltezeit überschreitet.

3. Überprüfung von Bus-Protokollen 📡

Bussysteme wie I2C oder SPI haben strenge zeitliche Anforderungen. Start- und Stoppbedingungen, Taktsperre und Datenschiebungen müssen perfekt ausgerichtet sein. Zeitdiagramme sind die Standardmethode zur Überprüfung dieser Protokolle.

-

Start/Stop: Die korrekte Übergangsbedingung auf der Datenleitung im Verhältnis zum Takt überprüfen.

-

Sperre: Sicherstellen, dass der Slave den Takt für die erforderliche Dauer niedrig halten kann.

-

Daten: Bestätigen, dass die Daten während der Takt-Hochphase stabil sind.

Abschließende Gedanken zur Signalintegrität 🎯

Genauere Zeitdiagramme zu erstellen, ist eine Fähigkeit, die durch Übung verbessert wird. Es erfordert ein tiefes Verständnis dafür, wie Elektronik im Laufe der Zeit reagiert. Indem Sie die oben genannten Richtlinien befolgen, können Sie Diagramme erstellen, die sowohl informativ als auch zuverlässig sind.

Denken Sie daran, dass diese Diagramme Kommunikationswerkzeuge sind. Sie schließen die Lücke zwischen Theorie und Umsetzung. Wenn Sie ein Zeitdiagramm zeichnen, erzählen Sie eine Geschichte darüber, wie das System reagiert. Machen Sie diese Geschichte klar, präzise und konsistent.

Konzentrieren Sie sich auf die wesentlichen Parameter: Setup, Hold, Verzögerung und Verzerrung. Halten Sie die Anordnung sauber und die Beschriftungen eindeutig. Mit diesen Gewohnheiten werden Sie feststellen, dass das Zeichnen von Zeitdiagrammen zu einem natürlichen Bestandteil Ihres Entwurfsprozesses wird, sodass Sie in Minuten statt in Stunden zeichnen können.