Das Verständnis des Signalverlaufs innerhalb eines digitalen Systems ist entscheidend für Ingenieure, die an Hardware, Firmware oder eingebetteter Software arbeiten. Ein Zeitverlaufsdiagramm dient als primäres visuelles Werkzeug, um die Wechselwirkungen verschiedener Signale über einen bestimmten Zeitraum darzustellen. Diese visuelle Darstellung ermöglicht es Teams, sicherzustellen, dass Daten korrekt erfasst werden, die Takte stabil sind und Logikübergänge ohne Konflikte stattfinden. Ohne ein präzises Verständnis dieser Diagramme kann die Systemzuverlässigkeit erheblich leiden. Dieser Leitfaden untersucht die wesentlichen Elemente, aus denen ein Zeitverlaufsdiagramm besteht, um eine genaue Gestaltung und Analyse zu gewährleisten.

Was ist ein Zeitverlaufsdiagramm? 📊

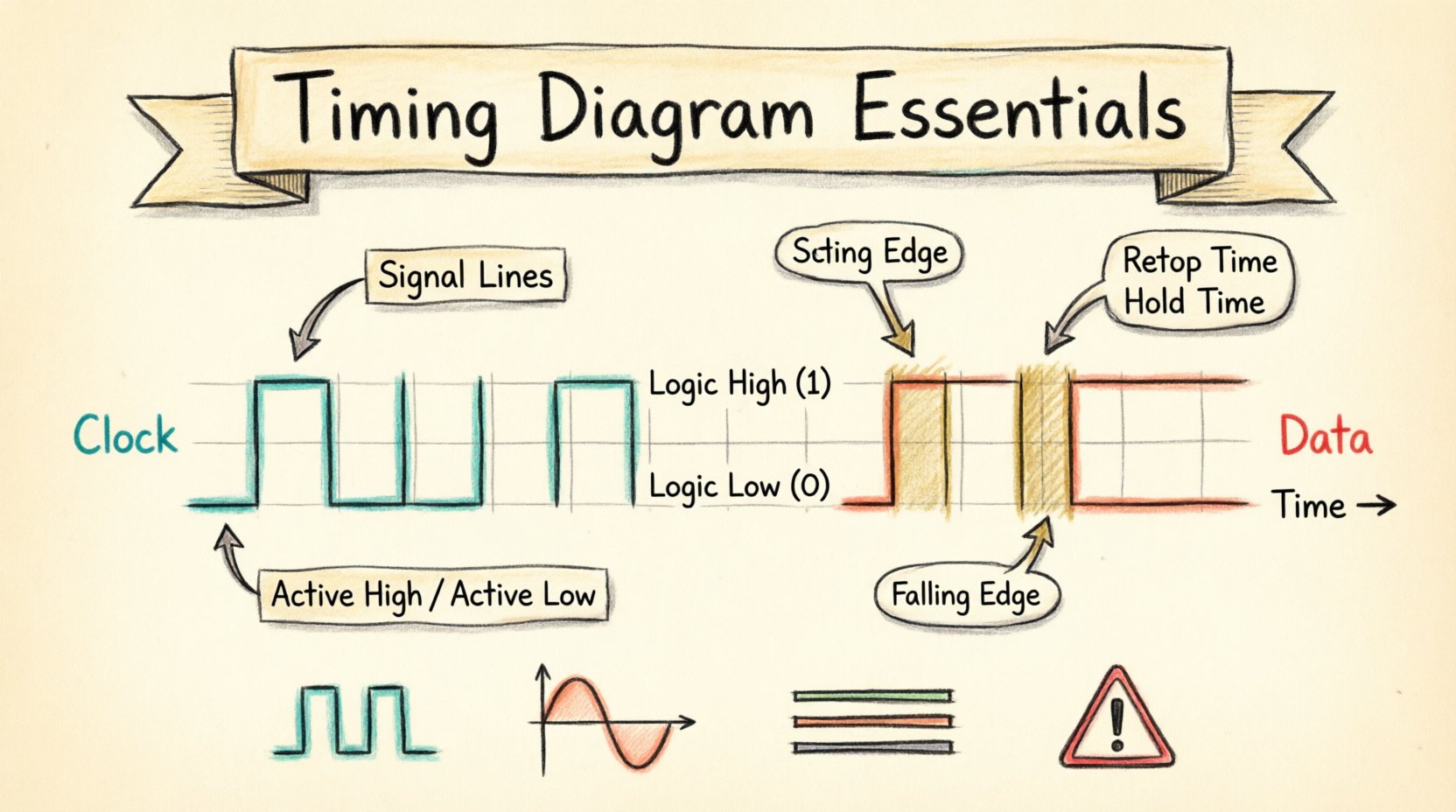

Ein Zeitverlaufsdiagramm ist eine grafische Darstellung, die das Verhalten von zwei oder mehr Signalen über die Zeit zeigt. Es zeigt die Abfolge von Ereignissen an, wobei angegeben wird, wann Signale ihren Zustand wechseln, wie lange sie in diesem Zustand verbleiben und wie sie sich zu einer Taktsquelle verhalten. In der Hardwareentwicklung sind diese Diagramme unverzichtbar, um sicherzustellen, dass Komponenten korrekt kommunizieren. In der Software helfen sie, Konkurrenzbedingungen, Rennbedingungen und Synchronisationspunkte zu visualisieren.

Diese Diagramme stellen in der Regel die Zeit auf der horizontalen Achse (x-Achse) und das Signalniveau oder den Zustand auf der vertikalen Achse (y-Achse) dar. Vertikale Linien repräsentieren bestimmte Zeitpunkte, während horizontale Linien den stabilen Zustand eines Signals anzeigen. Die Übergänge zwischen diesen Zuständen sind entscheidend, da sie die eigentlichen Datenübertragungen oder Steueraktionen innerhalb des Systems anzeigen.

Wesentliche Komponenten eines Zeitverlaufsdiagramms 🔧

Um ein effektives Zeitverlaufsdiagramm lesen oder erstellen zu können, muss man die grundlegenden Bausteine verstehen. Jedes Diagramm, unabhängig von seiner Komplexität, beruht auf einer konsistenten Menge an Elementen, um Informationen präzise zu vermitteln.

- Zeitachse: Die horizontale Grundlinie, die die Zeitentwicklung darstellt. Sie verläuft normalerweise von links nach rechts und zeigt von „Vergangenheit“ zu „Zukunft“.

- Signalleitungen: Horizontale Verläufe, die spezifischen Leitungen, Bussen oder Variablen zugeordnet sind. Jede Linie stellt das Logikniveau eines bestimmten Signals dar.

- Logikniveaus: Die vertikalen Positionen auf der Signalleitung. Typischerweise werden hohe (1, Vcc, True) und niedrige (0, Gnd, False) Zustände dargestellt.

- Übergänge: Die vertikalen Linien, die Logikniveaus verbinden. Eine steigende Flanke bewegt sich von niedrig zu hoch, während eine fallende Flanke von hoch zu niedrig geht.

- Anmerkungen: Textbeschriftungen oder Markierungen, die bestimmte Ereignisse, Verzögerungen oder Zustände klären.

Die Zeitachse: Präzision zählt ⏳

Die Zeitachse ist die Grundlage des Diagramms. Sie stellt nicht immer echte Sekunden dar; oft werden Taktrunden oder Nanosekunden dargestellt, abhängig von der Entwurfsgeschwindigkeit. Eine konsistente Skalierung ist entscheidend. Wenn ein Bereich des Diagramms 10 Nanosekunden pro Rasterfeld zeigt, muss ein anderer Bereich diese Skalierung beibehalten, es sei denn, er ist ausdrücklich vergrößert, um Details zu zeigen.

Beim Analysieren der Systemleistung hilft die Zeitachse, Engpässe zu identifizieren. Wenn beispielsweise ein Datensignal 50 Nanosekunden benötigt, um sich zu stabilisieren, aber die Taktkante bereits nach 40 Nanosekunden erfolgt, liegt ein Verstoß vor. Die Achse ermöglicht es Ingenieuren, diese Intervalle direkt zu messen.

Signalleitungen und Logikniveaus 🔄

Jede Signalleitung entspricht einem physischen Draht oder einer logischen Variablen. In komplexen Systemen kann ein Bus durch eine dicke Linie mit mehreren zusammengefassten Signalen oder durch einzelne Linien für jedes Bit dargestellt werden. Die Logikniveaus definieren den Zustand des Signals:

- Aktiv hoch: Das Signal gilt als „eingeschaltet“ oder „wahr“, wenn die Spannung hoch ist.

- Aktiv niedrig: Das Signal gilt als „eingeschaltet“ oder „wahr“, wenn die Spannung niedrig ist. Dies wird oft durch einen Punkt am Symbol oder eine spezifische Namenskonvention angezeigt.

Das Verständnis des aktiven Zustands ist entscheidend für die Interpretation von Steuersignalen wie „Chip Select“ oder „Write Enable“. Ein falsches Verständnis eines aktiv-niedrigen Signals als aktiv-hoch kann zu Designfehlern führen, die schwer zu debuggen sind.

Übergänge und Flanken ⚡

Übergänge treten auf, wenn ein Signal von einem Logikniveau zum anderen wechselt. Diese Änderungen sind in der realen Welt selten sofortig, aber in einem Zeitverlaufsdiagramm werden sie oft als senkrechte Linien gezeichnet, um den idealen Zeitpunkt des Wechsels darzustellen.

- Steigende Flanke: Der Übergang von niedrig zu hoch. Dies ist oft der Auslöspunkt für synchrones Logik.

- Fallende Flanke: Der Übergang von hoch zu niedrig. Einige Systeme verwenden diese Flanke zur Datenerfassung.

- Flankengetriggert: Logik, die nur im Moment des Übergangs reagiert.

- Ebenengetriggert: Logik, die reagiert, solange das Signal in einem bestimmten Zustand bleibt.

Realwelt-Signale haben Anstiegs- und Abfallzeiten. Eine perfekte senkrechte Linie ist eine Abstraktion. Bei Hochgeschwindigkeitsentwürfen ist die Steigung des Übergangs wichtig, da sie elektromagnetische Störungen und die Signalintegrität beeinflusst.

Zeitparameter und Einschränkungen 📐

Abseits der visuellen Linien liegt der entscheidende Wert eines Zeitdiagramms in den quantitativen Parametern, die neben den Signalen definiert sind. Diese Parameter bestimmen die physikalischen Grenzen, innerhalb derer die Hardware arbeiten muss.

Setup- und Haltezeit ⚙️

Dies sind die beiden häufigsten Einschränkungen bei der Entwurfslogik sequenzieller Schaltungen, insbesondere wenn Daten von einem Flip-Flop an einer Taktränder erfasst werden.

- Setup-Zeit: Die minimale Zeit, die das Datensignal stabil sein muss vor der aktiven Taktränder. Wenn sich das Datenignal zu nahe an der Taktränder ändert, kann der Flip-Flop den korrekten Wert möglicherweise nicht erfassen.

- Haltezeit: Die minimale Zeit, die das Datensignal stabil bleiben muss nach der aktiven Taktränder. Wenn sich das Datenignal zu früh nach der Flanke ändert, kann die Erfassung verfälscht werden.

| Parameter | Definition | Folge einer Verletzung |

|---|---|---|

| Setup-Zeit | Zeit, in der das Daten signal stabil sein muss, bevor die Taktränder | Metastabilität oder falsche Datenerfassung |

| Haltezeit | Zeit, in der das Daten signal stabil sein muss, nach der Taktränder | Metastabilität oder falsche Datenerfassung |

| Ausbreitungsverzögerung | Zeit, die benötigt wird, damit ein Signal durch ein Gatter reist | Reduzierung der Timing-Slack, niedrigere maximale Frequenz |

| Taktschiefe | Unterschied in der Ankunftszeit des Taktsignals | Reduzierung des effektiven Zeitfensters für Timing |

Ausbreitungsverzögerung ⏱️

Die Ausbreitungsverzögerung ist die Zeit, die benötigt wird, damit eine Änderung am Eingang die Ausgabe beeinflusst. In einem Zeitdiagramm ist dies als Lücke zwischen einer Taktränder und der daraus resultierenden Datenänderung sichtbar. Diese Verzögerung entsteht durch physikalische Beschränkungen, wie beispielsweise die Kapazität in den Leitungen und die Schaltgeschwindigkeit der Transistoren.

Beim Entwurf eines Systems muss die Summe der Ausbreitungsverzögerungen entlang eines Pfades kleiner als die Taktrate minus die Setup-Zeit sein. Wenn die Verzögerung zu groß ist, kann das System nicht mit der gewünschten Taktfrequenz laufen.

Taktschiefe und Jitter 📉

Taktschiefe bezieht sich auf den Unterschied in den Ankunftszeiten des Taktsignals an verschiedenen Stellen der Schaltung. In einem idealen Diagramm ist die Taktsignalleitung vertikal und gleichzeitig für alle Komponenten. In der Realität verursachen Routing-Unterschiede die Schiefe. Positive Schiefe bedeutet, dass der Takt am Ziel später eintrifft, was die Setup-Zeit verbessern kann, aber die Hold-Zeit beeinträchtigt.

Jitter ist die Variation in der Zeitpunkte der Signalränder. Es ist Rauschen, das dazu führt, dass die Kante früher oder später eintritt, als erwartet. Hoher Jitter verringert die effektive Zeitmarge für Timing und erfordert, dass das System langsamer läuft, um Stabilität zu gewährleisten.

Arten von Signalen und Bussen 📡

Verschiedene Systeme verwenden unterschiedliche Signalmethoden. Das Zeitdiagramm muss diese Unterschiede widerspiegeln, um genau zu sein.

Digitale Signale

Die meisten Zeitdiagramme konzentrieren sich auf digitale Logik. Diese Signale sind binär und schalten zwischen 0 und 1. Die Klarheit des Diagramms hängt davon ab, die Logikschwellen deutlich zu markieren. Einige Signale können Zwischenzustände oder „egal“-Bedingungen aufweisen, die gewöhnlich mit einem X gekennzeichnet sind.

Analoge Signale

Obwohl sie in rein digitalen Zeitdiagrammen weniger verbreitet sind, werden analoge Signale wie Spannungsversorgungen oder Sensorausgänge manchmal eingeschlossen. Sie werden mit abfallenden oder gekrümmten Linien dargestellt, anstatt mit scharfen Sprüngen, was eine kontinuierliche Änderung statt diskreter Zustandsänderungen anzeigt.

Busse und parallele Daten

Wenn mehrere Bits gleichzeitig übertragen werden, werden sie oft gruppiert. Ein Bus-Zeitdiagramm zeigt den Zustand aller Bits gleichzeitig. Es ist entscheidend, die Busbreite (z. B. 8-Bit, 32-Bit) anzugeben und das gültige Datenfenster darzustellen, in dem alle Bits gleichzeitig stabil sind.

Ein Zeitdiagramm lesen: Eine Schritt-für-Schritt-Anleitung 🔍

Die Interpretation dieser Diagramme erfordert einen systematischen Ansatz, um kritische Details nicht zu übersehen.

- Identifizieren Sie den Takt: Finden Sie die primäre Zeitreferenz. Alle anderen Ereignisse sollten relativ zu dieser Linie gemessen werden.

- Bestimmen Sie die Kantenempfindlichkeit: Prüfen Sie, ob das System auf die steigende oder fallende Kante des Takts reagiert.

- Verfolgen Sie die Gültigkeit der Daten: Suchen Sie nach dem Zeitraum, in dem die Datensignale stabil sind. Dies ist das „gültige Fenster“.

- Überprüfen Sie Steuersignale: Identifizieren Sie Aktivierungs-, Zurücksetz- oder Chip-Auswahl-Leitungen, die den Datenübertrag steuern.

- Messen Sie Intervalle: Verwenden Sie die Zeitachse, um Verzögerungen, Setup-Zeiten und Pulsbreiten zu messen.

Häufige Zeitverletzungen und Fehler ⚠️

Selbst bei sorgfältiger Planung treten Zeitverletzungen auf. Die Erkennung der Anzeichen in einem Diagramm ist der erste Schritt zur Behebung dieser Probleme.

- Setup-Verletzung: Daten treffen zu spät am nächsten Taktflankeneintritt ein. Die Lösung erfordert oft eine Verlangsamung des Takts oder die Optimierung des Logikpfads, um die Verzögerung zu reduzieren.

- Hold-Verletzung: Daten ändern sich zu früh nach der Taktflanke. Dies ist oft schwerer zu beheben, da möglicherweise eine Verzögerung im Datenpfad oder im Taktweg erforderlich ist.

- Metastabilität: Ein Zustand, in dem die Ausgabe eines Flip-Flops für eine undefinierte Dauer weder 0 noch 1 ist. Dies tritt meist auf, wenn Setup- oder Hold-Zeiten verletzt werden.

- Glitches: Kurze, unbeabsichtigte Impulse, verursacht durch Rennbedingungen in der kombinatorischen Logik. Diese können falsche Zustandsänderungen auslösen, wenn sie nicht gefiltert werden.

Asynchrone vs. synchrone Schaltung 🔄

Zeitdiagramme sehen je nach Entwurfsmethode unterschiedlich aus.

Synchroner Entwurf

Ereignisse werden durch einen globalen Takt koordiniert. Das Zeitdiagramm zeigt klare, periodische Taktsignale. Daten ändern sich nur an Taktflanken. Dieser Ansatz vereinfacht die Analyse, da das Zeitfenster festgelegt ist.

Asynchroner Entwurf

Ereignisse werden durch Handshake-Signale (wie Request und Acknowledge) koordiniert. Das Zeitdiagramm zeigt unregelmäßige Abstände zwischen Ereignissen. Obwohl flexibler, sind diese Diagramme schwerer zu analysieren, da kein fester Zeitbezug existiert.

Anwendung in Protokollen 📡

Kommunikationsprotokolle beruhen stark auf präziser Zeitsteuerung. Das Verständnis des Diagramms ist entscheidend für die Implementierung dieser Standards.

Serielle Kommunikation

Serielle Schnittstellen senden Daten bitweise. Das Zeitdiagramm zeigt die Bitperiode. Das Verhältnis zwischen Takt und Datenleitung (z. B. Daten gültig bei steigender Flanke) definiert die Protokollregeln.

Parallele Kommunikation

Parallele Schnittstellen senden mehrere Bits gleichzeitig. Das Zeitdiagramm muss die Setup-Zeit für die gesamte Busleitung zeigen. Alle Bits müssen stabil sein, bevor die Latch-Flanke eintritt.

Best Practices für Dokumentation 📝

Die Erstellung klarer Dokumentation stellt sicher, dass andere Ingenieure das System ohne Missverständnisse verstehen können.

- Verwenden Sie konsistente Bezeichnungen: Benennen Sie Signale genau so, wie sie im Code oder in der Schaltung erscheinen.

- Geben Sie Einheiten an: Geben Sie immer die Zeiteinheiten (ns, µs, Zyklen) auf der Achse an.

- Markieren Sie kritische Pfade: Verwenden Sie fett gedruckte Linien oder Farben, um die zeitkritischsten Signale anzugeben.

- Verletzungen markieren: Wenn eine Verletzung bekannt ist, markieren Sie sie deutlich, anstatt sie zu verbergen.

- Aktualisieren Sie es stets: Aktualisieren Sie Diagramme bei jeder Änderung des Entwurfs. Veraltete Diagramme sind eine Hauptquelle für Fehler.

Erweiterte Überlegungen: Mehrere Taktsysteme 🌐

Moderne Systeme arbeiten oft mit mehreren Taktsystemen, die mit unterschiedlichen Geschwindigkeiten laufen. Ein Zeitdiagramm für diese Systeme muss die Beziehung zwischen den Takten deutlich zeigen.

- Übergänge zwischen Taktsystemen: Daten, die von einem schnellen in ein langsames System übertragen werden, erfordern eine sorgfältige Synchronisation, um Datenverlust zu vermeiden.

- Phasenbeziehungen: Wenn zwei Takte eine gemeinsame Quelle haben, aber unterschiedliche Phasen aufweisen, muss das Diagramm die Phasenverschiebung anzeigen.

- Handshake-Logik: Asynchrone Brücken zwischen Systemen beruhen auf Handshake-Signalen. Das Zeitdiagramm muss den vollständigen Anfrage-Acknowledgement-Zyklus zeigen.

Die Rolle der Simulation bei der Zeitanalyse 💻

Bevor die Hardware gebaut wird, überprüfen Simulationen die Zeitdiagramme. Ingenieure verwenden Wellenform-Viewer, um das erwartete Verhalten mit den simulierten Ergebnissen zu vergleichen.

- Statische Zeitanalyse: Berechnet die schlechtesten Fallverzögerungen, ohne echte Wellenformen zu simulieren.

- Dynamische Zeit-Simulation: Führt eine virtuelle Version der Schaltung aus, um echte Wellenformen zu generieren.

- Simulation nach Layout: Berücksichtigt physische Leiterbahnlängen und Kapazitäten nach der Chip-Entwicklung.

Diese Werkzeuge ermöglichen es Ingenieuren, das Zeitdiagramm an der physischen Realität zu überprüfen. Wenn die Simulation eine Setup-Verletzung zeigt, muss der Entwurf vor der Fertigung überarbeitet werden.

Schlussfolgerung zur Zeitgenauigkeit ✅

Die Beherrschung der Erstellung und Interpretation von Zeitdiagrammen ist eine grundlegende Fähigkeit für technische Fachkräfte. Diese Diagramme schließen die Lücke zwischen abstrakter Logik und physischer Realität. Sie stellen sicher, dass Signale zum richtigen Zeitpunkt, im richtigen Zustand und mit ausreichender Stabilität eintreffen, damit das System funktionieren kann. Durch die Einhaltung der in diesem Leitfaden beschriebenen Elemente und Beschränkungen können Teams Fehler reduzieren und die Zuverlässigkeit des Systems verbessern. Sorgfalt bei diesen visuellen Darstellungen zahlt sich in Stabilität und Leistung des Endprodukts aus.

Unabhängig davon, ob man an Hochgeschwindigkeits-Speicher-Schnittstellen, energiesparenden Mikrocontrollern oder komplexen Datenbussen arbeitet, bleiben die Prinzipien gleich. Zeit ist die Konstante, und die Signale sind die Variablen. Das Verständnis ihrer Beziehung ist der Schlüssel für erfolgreiche Ingenieurarbeit.