In der komplexen Welt der eingebetteten Technik ist Präzision keine bloße Vorliebe; sie ist eine Voraussetzung. Zeitdiagramme dienen als visuelle Baupläne, um zu verstehen, wie Signale im Laufe der Zeit miteinander interagieren. Diese grafischen Darstellungen zeigen Spannungsniveaus, Taktrunden und Datenumschläge entlang einer zeitlichen Achse ab. Für Ingenieure, die Mikrocontroller, Sensoren oder Kommunikationsschnittstellen entwerfen, ist das Beherrschen des Lesens und Erstellens dieser Diagramme entscheidend, um die Zuverlässigkeit des Systems zu gewährleisten.

Ohne eine klare Sicht auf zeitliche Beziehungen können Hardwarekomponenten nicht korrekt kommunizieren, was zu Datenkorruption oder Systemabstürzen führen kann. Dieser Leitfaden untersucht die praktischen Anwendungen von Zeitdiagrammen in verschiedenen Bereichen der eingebetteten Entwicklung und bietet einen detaillierten Einblick in ihre Nutzen, ohne sich auf spezifische Softwarewerkzeuge zu stützen.

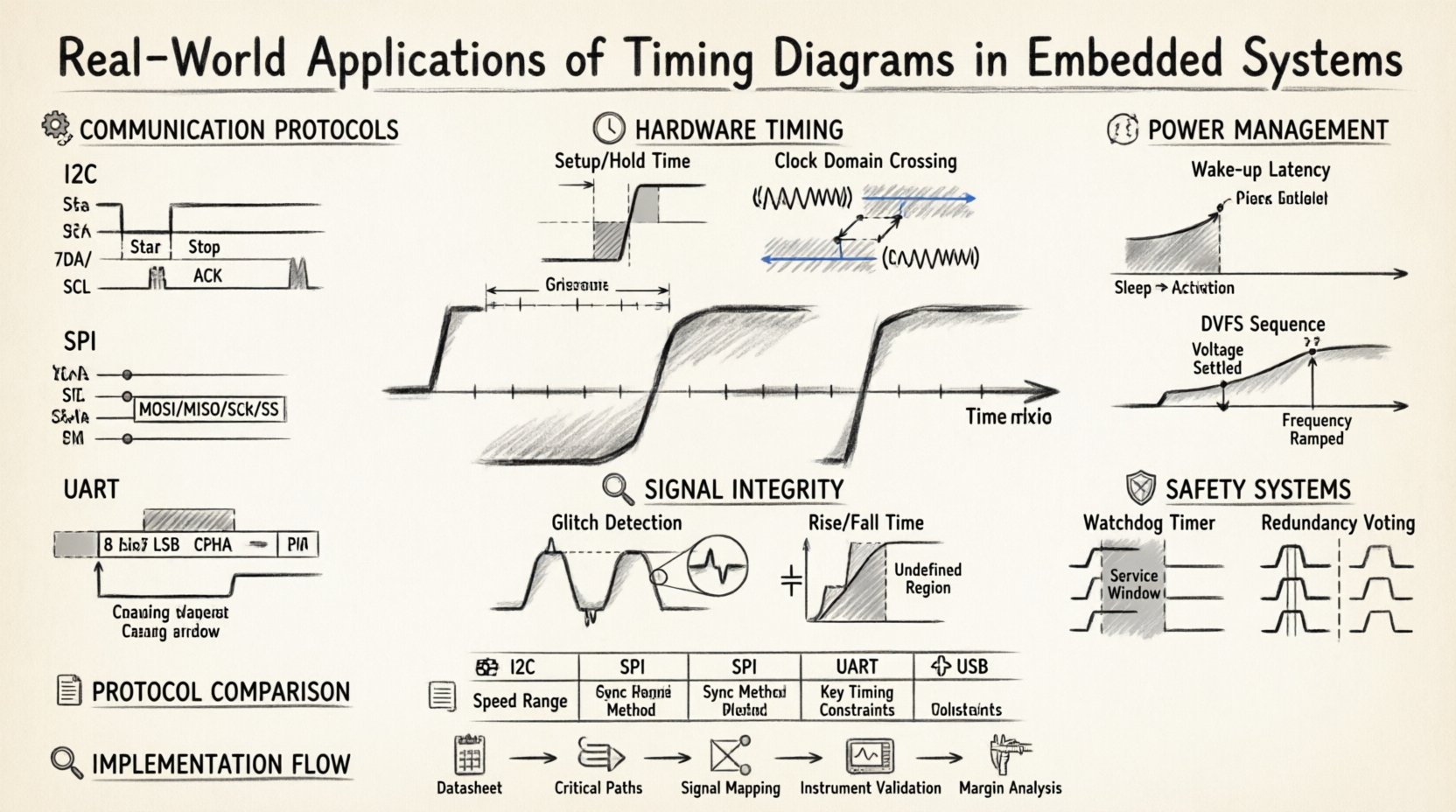

🔌 Analyse von Kommunikationsprotokollen

Serielle Kommunikation ist die Grundlage moderner eingebetteter Systeme. Daten verbleiben selten innerhalb eines einzigen Chips; sie bewegen sich zwischen Prozessoren, Speichern und Peripheriegeräten. Zeitdiagramme sind entscheidend, um diese Interaktionen zu definieren und zu überprüfen.

Inter-Integrated Circuit (I2C)

Das I2C-Protokoll nutzt eine Zweidraht-Schnittstelle: Serielle Datenleitung (SDA) und serielle Taktschaltung (SCL). Ein Zeitdiagramm für I2C zeigt die spezifische Reihenfolge auf, die für die Datenübertragung erforderlich ist.

- Startbedingung: Die SDA-Leitung wechselt von Hoch auf Niedrig, während die SCL-Leitung hoch bleibt. Dies signalisiert dem Bus, dass eine Transaktion beginnen soll.

- Adressrahmen: Das erste gesendete Byte enthält die 7-Bit-Adresse des Zielgeräts sowie ein Lese-/Schreibbit.

- Bestätigung: Der Empfänger zieht die SDA-Leitung während des neunten Taktpulses auf Niedrig, um die Übernahme zu bestätigen.

- Stop-Bedingung: Die SDA-Leitung wechselt von Niedrig auf Hoch, während SCL hoch ist, wodurch der Bus freigegeben wird.

Ingenieure nutzen diese Diagramme, um Probleme wie Taktausdehnung zu erkennen. Wenn ein Slave-Gerät die Datenverarbeitung nicht schnell genug bewältigen kann, hält es die SCL-Leitung auf Niedrig. Das Zeitdiagramm zeigt diese Verlängerung, sodass der Entwickler die Verarbeitungsschleifen oder Puffergrößen anpassen kann.

Serielle Peripherie-Schnittstelle (SPI)

SPI ist ein synchrones Protokoll, das häufig für höhere Geschwindigkeiten bei der Kommunikation verwendet wird. Es umfasst vier Leitungen: Master Out Slave In (MOSI), Master In Slave Out (MISO), Serieller Takt (SCK) und Slave-Auswahl (SS).

- Taktpolarität (CPOL): Bestimmt den Ruhezustand der Taktschaltung. Ist sie vor Beginn der Datenübertragung hoch oder niedrig?

- Taktfrequenz (CPHA): Definiert, wann die Daten abgetastet werden. Ist es am ersten oder zweiten Taktrand?

- Zeitplan für Chip-Auswahl: Die SS-Leitung muss während der gesamten Transaktion niedrig bleiben. Wenn sie kurzzeitig auf Hoch springt, wird die Transaktion abgebrochen.

Das Verständnis dieser Phasen ist entscheidend. Eine Abweichung in CPOL oder CPHA zwischen Master und Slave führt zu Müll-Daten. Ein Zeitdiagramm visualisiert diese Übergänge und macht es einfach, Abweichungen während des Hardware-Starts zu erkennen.

Universeller asynchroner Empfänger/Transmitter (UART)

Im Gegensatz zu SPI und I2C verwendet UART keine Taktschaltung. Die Synchronisation beruht auf vereinbarten Baudraten. Zeitdiagramme hier konzentrieren sich auf die Bitdauer und die Rahmenbildung.

- Startbit: Ein niedriges Pulspunkt zeigt den Beginn eines Bytes an.

- Datenbits: Typischerweise 8 Bits, übertragen mit dem wenigstwertigen Bit (LSB) zuerst.

- Stop-Bit: Ein Hochpuls signalisiert das Ende des Bytes.

Zeitdiagramme helfen Ingenieuren, das Toleranzfenster zu berechnen. Wenn die Takte der beiden Geräte zu weit auseinander driften, verschiebt sich der Abtastpunkt und verursacht Fehler. Das Diagramm zeigt das Abtastfenster, das normalerweise in der Mitte der Bitzeit liegt.

⏱️ Hardware-Synchronisation und Vorbereitungszeiten

Abgesehen von der Kommunikation sind Zeitdiagramme unverzichtbar, um zu verstehen, wie Logikgatter und Flip-Flops miteinander interagieren. Digitale Logik beruht auf präzisen Zeitbedingungen, um korrekt zu funktionieren.

Vorbereitungs- und Haltezeiten

Wenn Daten in einen Register oder Flip-Flop eintreten, müssen sie bestimmten zeitlichen Anforderungen im Verhältnis zur Taktkante entsprechen.

- Vorbereitungszeit: Die minimale Dauer, in der Daten stabil sein müssen vor die Taktkante eintrifft.

- Haltezeit: Die minimale Dauer, in der Daten stabil bleiben müssen nach die Taktkante eintrifft.

Wenn ein Signal die Vorbereitungszeit verletzt, könnte der Register den falschen Wert erfassen. Wenn die Haltezeit verletzt wird, kann Metastabilität auftreten. Ein Zeitdiagramm visualisiert das Datensignal im Verhältnis zur Taktkante und hebt die verbotenen Bereiche hervor, in denen Datenänderungen nicht zulässig sind.

Taktbereichsübergang (CDC)

Komplexe Systeme führen oft verschiedene Teile der Logik mit unterschiedlichen Taktfrequenzen aus. Die Übertragung von Daten von einem schnellen Taktbereich in einen langsamen oder umgekehrt birgt Risiken.

- Synchronisation: Verwendung einer Kette von Flip-Flops, um sicherzustellen, dass das Signal vor der Verwendung stabil ist.

- Handshake: Verwendung von Anforderungs- und Bestätigungs-Signalen zur Koordination der Datenübertragung ohne gemeinsamen Takt.

Ein Zeitdiagramm für CDC zeigt die Handshake-Sequenz. Es stellt sicher, dass die Daten gültig sind, bevor der empfangende Bereich sie bestätigt. Dadurch wird Datenverlust bei asynchronen Übertragungen verhindert.

🔍 Debugging und Signalintegrität

Wenn ein eingebettetes System unerwartet reagiert, suchen Ingenieure oft zuerst in Zeitdiagrammen nach Ursachen. Sie liefern eine historische Aufzeichnung des Signalverhaltens, die statische Tests nicht erfassen können.

Erkennen von Störungen

Eine Störung ist ein kurzer, unbeabsichtigter Impuls auf einer Signalleitung. Sie kann nur wenige Nanosekunden dauern, kann aber einen Zustandswechsel in einem Flip-Flop auslösen.

- Rennbedingungen: Treten auf, wenn die Reihenfolge der Ereignisse von Bedeutung ist und die Zeitplanung zu eng ist.

- Ausbreitungsverzögerung:Signale benötigen Zeit, um durch Logikgatter zu reisen. Zeitdiagramme zeigen diese Verzögerungen deutlich.

Durch Überlagerung des erwarteten Zeitdiagramms mit den erfassten tatsächlichen Signalen können Ingenieure genau dort den Abweichungspunkt identifizieren. Dies ermöglicht gezielte Korrekturen im Firmware- oder Hardware-Design.

Rauschabstände und Anstiegs-/Abfallzeiten

Realitätsnahe Signale sind keine perfekten Rechteckwellen. Sie weisen Anstiegs- und Abfallzeiten aufgrund von Kapazität und Induktivität in den Spuren auf.

- Anstiegszeit:Die Zeit, die ein Signal benötigt, um von niedrig auf hoch zu wechseln.

- Abfallzeit:Die Zeit, die ein Signal benötigt, um von hoch auf niedrig zu wechseln.

Wenn diese Übergänge zu langsam sind, könnte das Signal zu lange im undefinierten Spannungsbereich zwischen Logik 0 und Logik 1 verweilen. Dies kann dazu führen, dass mehrere Taktränder ausgelöst werden oder Logikfehler auftreten. Ein Zeitdiagramm hilft dabei, diese Steigungen zu messen, um sicherzustellen, dass sie den Spezifikationen des empfangenden Chips entsprechen.

💤 Energiemanagement und Energiesparzustände

Energieeffizienz ist bei batteriebetriebenen eingebetteten Geräten von großer Bedeutung. Zeitdiagramme spielen eine Rolle bei der Optimierung des Energieverbrauchs.

Wachwerfsverzögerung

Wenn ein Gerät in den Ruhezustand wechselt, wird der Takt gestoppt, um Energie zu sparen. Das Aufwachen erfordert die Wiederherstellung des Takts und die Stabilisierung der Spannung.

- Übergangszeit:Die Zeit, die benötigt wird, um vom Schlafzustand in den aktiven Zustand zu wechseln.

- Verzögerung:Die Verzögerung zwischen einem Weckereignis und der Ausführung des Codes durch den Prozessor.

Ein Zeitdiagramm der Einschaltsequenz zeigt die Verzögerung zwischen dem Auslösesignal und der Stabilisierung des Systemtakts. Diese Information ist entscheidend für zeitkritische Anwendungen, bei denen eine Verzögerung von einigen Millisekunden von Bedeutung ist.

Dynamische Spannungs- und Frequenzskalierung (DVFS)

Systeme können Spannung und Frequenz basierend auf der Last anpassen. Zeitdiagramme helfen dabei, die Übergänge zwischen verschiedenen Leistungsstufen zu überprüfen.

- Frequenzanstieg: Ändert sich der Takt reibungslos oder abrupt?

- Spannungsansprechzeit: Ist die Spannung stabil, bevor die neue Frequenz angewendet wird?

Falsche Reihenfolge während der DVFS kann zu Spannungseinbrüchen oder Logikfehlern führen. Das Zeitdiagramm liefert die Sequenzüberprüfung, die erforderlich ist, um sichere Übergänge zu gewährleisten.

🛡️ Sicherheitskritische Systeme

In der Automobil-, Medizin- und Industrieanwendung ist Sicherheit von höchster Bedeutung. Zeitdiagramme werden verwendet, um zu überprüfen, ob Sicherheitsmechanismen innerhalb der vorgeschriebenen Zeitgrenzen funktionieren.

Watchdog-Timer

Ein Watchdog-Timer setzt das System zurück, wenn die Software hängt. Zeitdiagramme definieren die Ablaufzeit.

- Zeitüberschreitungszeitraum: Die maximal zulässige Zeit zwischen Neustarts.

- Wartungszeitraum: Die Zeit, die die Software benötigt, um den Timer zurückzusetzen.

Wenn der Wartungszeitraum zu lang ist, könnte der Watchdog unnötigerweise auslösen. Ist er zu kurz, könnte ein langsamer Interrupt eine falsche Neustartaktion verursachen. Das Diagramm stellt sicher, dass die Zeitabläufe den Anforderungen der Sicherheitsstandards entsprechen.

Redundanz und Abstimmung

Einige Systeme verwenden mehrere Prozessoren, um über die korrekte Ausgabe abzustimmen. Zeitdiagramme stellen sicher, dass alle Prozessoren gleichzeitig die Abstimmungsphase erreichen.

- Synchronisation: Alle Kanäle müssen ihre Daten ausrichten.

- Zeitüberschreitung: Wenn ein Kanal zu spät ist, muss das System die Abweichung erkennen.

Dies ist entscheidend bei Bremssteuerungen oder Lenksystemen, bei denen eine Verzögerung gefährlich sein kann. Das Zeitdiagramm zeigt die Verzögerung jedes Kanals auf, um sicherzustellen, dass die Abstimmungslogik korrekt funktioniert.

📋 Übersicht über den Protokollvergleich

Die folgende Tabelle fasst die wichtigsten Zeitverhaltensmerkmale gängiger eingebetteter Schnittstellen zusammen, um die Auswahl und Gestaltung zu unterstützen.

| Protokoll | Geschwindigkeitsbereich | Synchronisationsmethode | Typischer Anwendungsfall | Wichtige Zeitverzögerungsbeschränkung |

|---|---|---|---|---|

| I2C | 100 kHz bis 3,4 MHz | Geteilter Takt | Sensoren, EEPROM | Taktverlängerung |

| SPI | 1 MHz bis 50 MHz+ | Master-Takt | Flash-Speicher, Displays | Chip-Select-Vorbereitung |

| UART | 9600 bis 921600 bps | Asynchron | Debug, GPS, Bluetooth | Baudrate-Toleranz |

| USB | 1,5 Mbps bis 20 Gbps | Paketbasiert | Peripheriegeräte, Speicher | Token/Handshake-Zeitplanung |

🛠️ Praktische Umsetzungsschritte

Die Erstellung eines Zeitdiagramms erfordert einen systematischen Ansatz. Es beginnt mit der Verständnis der Spezifikation und endet mit der Überprüfung.

- Datenblätter prüfen: Jedes Bauteil verfügt über einen Zeitabschnitt. Suchen Sie nach den Tabellen zu den Wechselstrom-Eigenschaften.

- Kritische Pfade identifizieren: Bestimmen Sie, welche Signale die maximale Geschwindigkeit des Systems bestimmen.

- Abhängigkeiten abbilden: Zeichnen Sie die Beziehungen zwischen Signalen auf. Welches Signal löst das andere aus?

- Mit Instrumenten validieren: Verwenden Sie Logikanalysatoren oder Oszilloskope, um echte Wellenformen aufzunehmen.

- Grenzen analysieren: Stellen Sie sicher, dass ausreichend Zeit zwischen den Signalen vorhanden ist, um Temperatur- und Spannungsvariationen zu berücksichtigen.

Dokumentation ist entscheidend. Ein gut annotiertes Zeitdiagramm dient als Referenz für zukünftige Wartung. Es erklärt, warum bestimmte Verzögerungen hinzugefügt wurden oder warum spezifische Pull-up-Widerstände gewählt wurden.

🚀 Erweiterte Überlegungen

Je komplexer die Systeme werden, desto mehr Aufmerksamkeit erfordert die Zeitanalyse.

Jitter und Phasenrauschen

Takte sind nicht vollkommen stabil. Jitter ist die Abweichung der Taktränder von ihrer idealen Position. Zeitdiagramme zeigen die Variation der Ränderstellung über mehrere Zyklen.

- Perioden-Jitter:Variation der Taktrate.

- Zyklus-zu-Zyklus-Jitter:Variation von einem Zyklus zum nächsten.

Hohe Jitter verringert die Setup- und Hold-Margin. Bei Hochgeschwindigkeitsschnittstellen wie DDR-Speicher kann dies zu Lese-/Schreibfehlern führen. Zeitdiagramme helfen dabei, diese Jitter zu quantifizieren, um sicherzustellen, dass sie innerhalb akzeptabler Grenzen bleibt.

Thermische Effekte

Die Temperatur beeinflusst die Geschwindigkeit von Transistoren. Je heißer ein Chip wird, desto langsamer werden die Signale.

- Worst-Case-Analyse:Entwerfen Sie für die maximale Betriebstemperatur.

- Thermische Drosselung:Stellen Sie sicher, dass das System während der Hochgeschwindigkeitsbetriebsphase keine sicheren thermischen Grenzen überschreitet.

Ein Zeitdiagramm, das bei Raumtemperatur erstellt wurde, gilt möglicherweise nicht bei 85 °C. Ingenieure müssen diese thermischen Verschiebungen berücksichtigen, um Robustheit zu gewährleisten.

📝 Abschließende Gedanken

Zeitdiagramme sind mehr als nur Zeichnungen; sie sind die Sprache der Synchronisation. Sie schließen die Lücke zwischen theoretischer Logik und physischer Realität. In eingebetteten Systemen, wo Hardware und Software verflochten sind, führt ein klares Verständnis der Signalzeitgestaltung zu einer Vermeidung kostspieliger Neuplanungen und garantiert Zuverlässigkeit.

Unabhängig davon, ob Sie ein Kommunikationsprotokoll debuggen, die Stromaufnahme optimieren oder die Sicherheit in einem kritischen System gewährleisten, liefern diese Diagramme die Klarheit, die erforderlich ist, um fundierte Entscheidungen zu treffen. Indem sie sich auf Setup-Zeiten, Propagationsverzögerungen und Signalintegrität konzentrieren, können Ingenieure Systeme entwickeln, die unter realen Bedingungen konsistent funktionieren.

Die Investition in das Verständnis von Zeitbeziehungen zahlt sich in Stabilität und Leistung aus. Während die Technologie fortschreitet, bleiben die Prinzipien gleich. Zeit ist die Konstante, und die Beherrschung ihrer Messung ist der Schlüssel für einen erfolgreichen eingebetteten Entwurf.