Das Verständnis des Verhaltens digitaler Schaltungen erfordert mehr als nur das Wissen über Logikgatter. Es erfordert ein Verständnis dafür, wie Signale im Laufe der Zeit wechseln. Zeitdiagramme bieten die visuelle Sprache für diese zeitliche Analyse. Sie zeigen den Zustand verschiedener Signale im Verhältnis zu einem Takt oder einem bestimmten Ereignis auf. Für Informatik-Studenten ist die Beherrschung dieses Konzepts entscheidend für die Gestaltung zuverlässiger Systeme.

Diese Anleitung untersucht die Mechanik, Lesetechniken und kritischen Parameter, die mit Zeitdiagrammen verbunden sind. Wir behandeln alles von grundlegenden Signalübergängen bis hin zu komplexen Setup- und Hold-Zeit-Verletzungen. Am Ende dieser Übersicht werden Sie über eine solide Grundlage für die Analyse digitaler Wechselwirkungen verfügen.

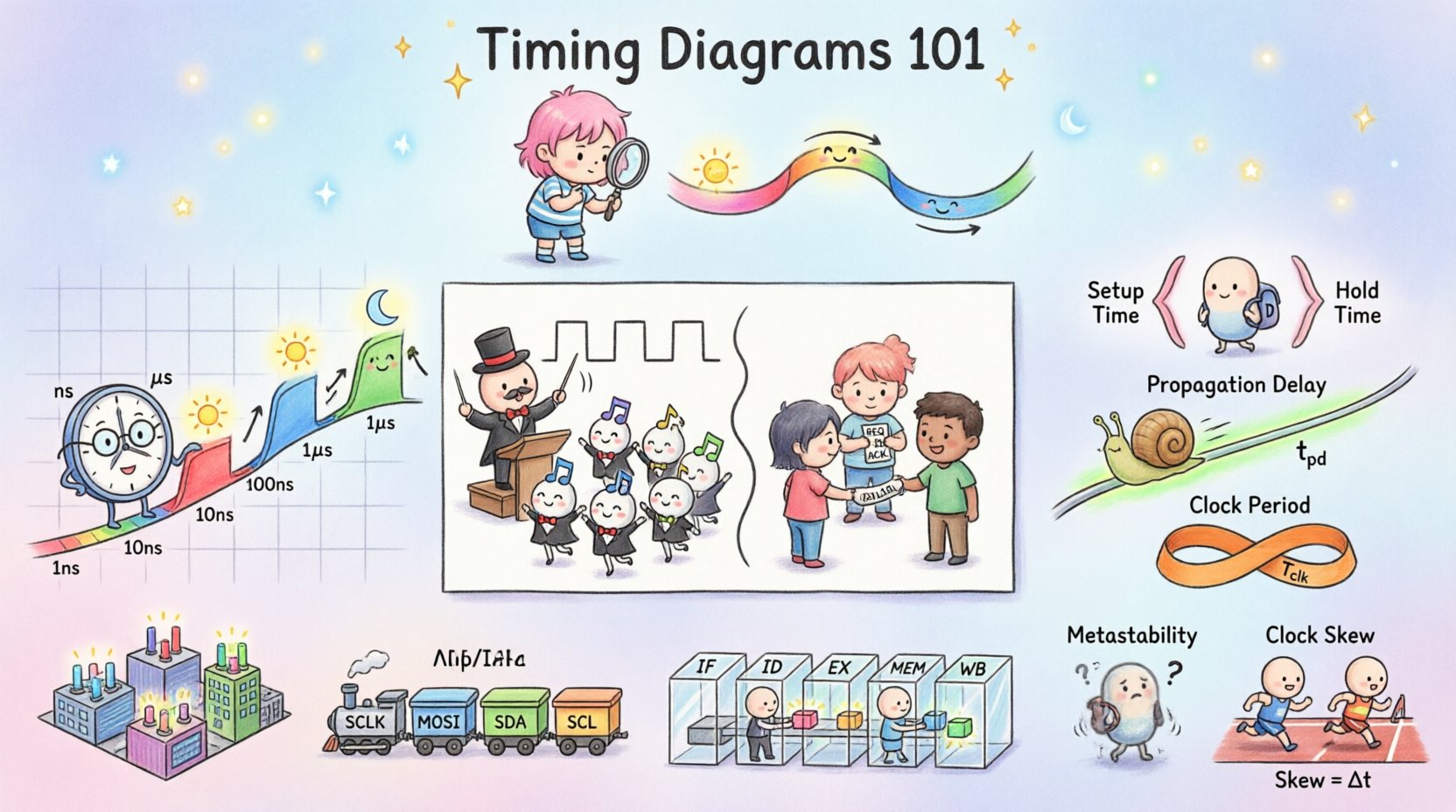

Was ist ein Zeitdiagramm? ⏱️

Ein Zeitdiagramm ist eine grafische Darstellung der Beziehung zwischen zwei oder mehr Signalen im Laufe der Zeit. Es fungiert als Zeitstrahl für digitale Ereignisse. Jedes Signal wird als horizontale Linie dargestellt. Die vertikale Position zeigt den Logikpegel oder den Zustand an. Die horizontale Achse stellt den Zeitverlauf dar.

Diese Diagramme sind entscheidend dafür, sicherzustellen, dass ein digitales System korrekt funktioniert. Sie helfen Ingenieuren, vorherzusagen, wie Daten durch Register, Busse und Speicher fließen. Ohne sie wäre das Debuggen von Hardwareproblemen nahezu unmöglich. Sie schließen die Lücke zwischen abstrakter Logik und physischer Realität.

Wichtige Komponenten digitaler Signale 📡

Bevor man sich den Diagrammen widmet, muss man die Signale selbst verstehen. Digitale Systeme stützen sich auf Spannungsniveaus, um binäre Daten darzustellen. Diese Niveaus sind nicht immer statisch; sie wechseln zwischen Zuständen.

- Logischer Hochzustand (1):Stellt typischerweise eine Spannung nahe der Versorgungsspannung dar.

- Logischer Tiefzustand (0):Stellt typischerweise eine Spannung nahe dem Erdpotential dar.

- Kanten: Die Übergangspunkte zwischen Hoch- und Tiefzustand. Steigende Kanten verlaufen von niedrig nach hoch. Fallende Kanten verlaufen von hoch nach niedrig.

- Stabiler Zustand: Der Zeitraum, in dem ein Signal konstant bleibt.

- Rauschabstände: Die Toleranz, die ein Signal hat, bevor es falsch interpretiert wird.

Zeitdiagramme visualisieren diese Übergänge. Sie zeigen genau, wann ein Signal wechselt und wie lange es in diesem Zustand bleibt. Diese Präzision ist entscheidend für die Gewährleistung der Datenintegrität.

Verständnis der Zeitachse ⏳

Die horizontale Achse ist die Grundlage jedes Zeitdiagramms. Sie stellt den zeitlichen Fortschritt dar. In der digitalen Schaltungstechnik ist diese Achse oft mit einem Taktsignal synchronisiert. Der Takt fungiert als Herzschlag des Systems.

Die Einheiten auf der Zeitachse variieren je nach Geschwindigkeit der Schaltung. Häufig verwendete Einheiten sind:

- Sekunden (s):Wird für sehr langsame Systeme verwendet.

- Millisekunden (ms):10^-3 Sekunden.

- Mikrosekunden (µs):10^-6 Sekunden.

- Nanosekunden (ns):10^-9 Sekunden. Standard für moderne Prozessoren.

- Pikosekunden (ps): 10^-12 Sekunden. Erforderlich für Hochgeschwindigkeitsschnittstellen.

Beim Lesen eines Diagramms achten Sie auf die Skalierungsmarkierungen. Sie zeigen die Dauer jedes Zyklus an. Dies hilft bei der Berechnung von Ausbreitungsverzögerungen und sicherstellt, dass Signale innerhalb des erforderlichen Zeitfensters eintreffen.

Synchron vs. asynchron Systeme 🔄

Digitale Systeme fallen im Allgemeinen in zwei Kategorien, abhängig davon, wie sie die Zeitsteuerung handhaben. Das Verständnis des Unterschieds ist entscheidend für die Erstellung genauer Diagramme.

1. Synchron Systeme

Bei synchronen Designs finden alle Zustandsänderungen relativ zu einem globalen Taktsignal statt. Das Zeitdiagramm zeigt eine periodische Taktsignalwelle. Jeder Flip-Flop aktualisiert sich am aktiven Flankensignal dieses Taktsignals.

- Vorteile: Vorhersehbares Verhalten. Einfacher zu verifizieren.

- Herausforderungen: Taktschiefe kann Probleme verursachen, wenn Signale zu unterschiedlichen Zeiten eintreffen.

- Diagramm-Feature: Senkrechte Linien weisen oft auf die Taktränder hin, um Erfassungszeitpunkte zu zeigen.

2. Asynchrone Systeme

Asynchrone Designs verlassen sich nicht auf einen globalen Takt. Stattdessen verwenden sie Handshake-Protokolle oder lokale Signale, um Aktionen auszulösen. Zeitdiagramme hier sind unregelmäßiger.

- Vorteile: In einigen Fällen geringerer Stromverbrauch. Schnellere durchschnittliche Reaktionszeiten.

- Herausforderungen: Komplex zu verifizieren. Anfällig für Rennbedingungen.

- Diagramm-Feature: Signale lösen sich gegenseitig ohne festen Rhythmus aus.

Kritische Zeitparameter 📏

Spezifische Messwerte definieren die Zuverlässigkeit eines Zeitdiagramms. Diese Parameter bestimmen, ob eine Schaltung unter allen Bedingungen korrekt funktioniert.

| Parameter | Beschreibung | Bedeutung |

|---|---|---|

| Ausbreitungsverzögerung | Zeit, die benötigt wird, damit ein Signal von der Eingabe zur Ausgabe gelangt. | Begrenzt die maximale Betriebsfrequenz. |

| Vorhaltezeit | Zeitdaten müssen stabil sein, bevor die Taktkante eintritt. | Stellt sicher, dass die Schleuse den richtigen Wert erfasst. |

| Haltezeit | Zeitdaten müssen stabil bleiben, nachdem die Taktkante eingetreten ist. | Verhindert, dass die Schleuse einen sich ändernden Wert liest. |

| Taktfrequenzperiode | Dauer eines vollständigen Zyklus des Taktsignals. | Bestimmt die Geschwindigkeit des Systems. |

| Tastverhältnis | Prozentsatz des Zeitraums, in dem das Signal hoch ist. | Wirkt sich auf den Stromverbrauch und die Zeitintervalle aus. |

Tiefgang: Setup- und Haltezeiten

Setup- und Haltezeiten sind die kritischsten Einschränkungen für sequenzielle Logik. Bei Verletzung kann das System in einen metastabilen Zustand geraten, in dem die Ausgabe undefiniert ist.

Setup-Zeit-Verletzung: Dies tritt auf, wenn die Daten zu nahe an der Taktkante wechseln. Der Schaltkreis hat nicht genug Zeit, sich auf die Erfassung vorzubereiten. Das Ergebnis ist oft ein Logikfehler.

Haltezeit-Verletzung: Dies tritt auf, wenn die Daten zu früh nach der Taktkante wechseln. Der Schaltkreis versucht noch immer, den vorherigen Wert zu erfassen. Dies ist oft schwerer zu beheben, da es von der physischen Anordnung abhängt.

Lesen und Analysieren von Diagrammen 🔍

Die Analyse eines Zeitdiagramms erfordert einen systematischen Ansatz. Befolgen Sie diese Schritte, um die visuellen Daten genau zu interpretieren.

- Identifizieren Sie den Takt: Finden Sie das periodische Signal. Dies ist Ihr Bezugspunkt.

- Aktive Kanten lokalisieren: Bestimmen Sie, ob das System auf steigende oder fallende Kanten reagiert.

- Signalabhängigkeiten verfolgen: Sehen Sie, wie Änderungen eines Signals andere beeinflussen.

- Auf Störungen prüfen: Suchen Sie nach kurzen Impulsen, die Rauschen oder unbeabsichtigte Übergänge sein könnten.

- Einschränkungen überprüfen: Stellen Sie sicher, dass Setup- und Haltezeiten für alle Register eingehalten werden.

Betrachten Sie einen einfachen Datenübertragungsszenario. Eine CPU sendet Daten an den Speicher. Das Zeitdiagramm zeigt, dass zuerst die Adressleitungen stabil werden, gefolgt von den Datensignalen und schließlich dem Schreibsignal. Jeder Schritt muss innerhalb eines bestimmten Zeitfensters erfolgen.

Häufige Verstöße und ihre Auswirkungen ⚠️

Selbst erfahrene Ingenieure stoßen auf Timing-Probleme. Das Verständnis häufiger Verstöße hilft bei der Fehlersuche.

1. Metastabilität

Wenn ein Signal die Setup- oder Hold-Zeit überschreitet, kann die Ausgabe des Flip-Flops vor der Endstabilisierung oszillieren. Dieser Zustand wird Metastabilität genannt. Er kann sich durch das System ausbreiten und unvorhersehbares Verhalten verursachen. Synchronisationschaltungen werden häufig verwendet, um dieses Risiko zu verringern.

2. Verzögerung (Skew)

Clock Skew tritt auf, wenn das Taktsignal zu verschiedenen Komponenten zu unterschiedlichen Zeiten eintrifft. Dies kann die effektive Timing-Marge verringern. Positiver Skew bietet mehr Setup-Zeit, aber weniger Hold-Zeit. Negativer Skew hat das Gegenteil zur Folge.

3. Rennbedingungen

Rennbedingungen treten auf, wenn die Ausgabe von der Reihenfolge der Ereignisse abhängt. Wenn zwei Signale gleichzeitig wechseln, bestimmt die Reihenfolge ihrer Verarbeitung den Endzustand. Zeitdiagramme helfen dabei, diese Abläufe zu visualisieren, um Rennen zu vermeiden.

Anwendung in der Computerarchitektur 🖥️

Zeitdiagramme sind nicht nur theoretische Werkzeuge. Sie werden in der praktischen Architektur breit eingesetzt.

Speicher-Schnittstellen

DRAM und SRAM haben strenge Timing-Anforderungen. Der Speichercontroller muss auf bestimmte Verzögerungen warten, bevor er liest oder schreibt. Zeitdiagramme definieren die Befehlsbus-Reihenfolgen. Sie stellen sicher, dass der Speicherbank bereit ist, bevor auf Daten zugegriffen wird.

Bus-Protokolle

Protokolle wie I2C, SPI und UART basieren auf Timing für die Kommunikation. Die Taktsignalleitung in SPI synchronisiert den Datentransfer. Bei UART basiert das Timing auf Baudraten. Der Empfänger muss die Datensignalleitung genau in der Mitte des Bitzeitraums abtasten. Ein Zeitdiagramm zeigt die Ausrichtung des Startbits, der Datenbits und des Stopbits.

Pipeline-Stufen

Moderne CPUs verwenden Pipelining, um mehrere Befehle gleichzeitig auszuführen. Jede Stufe muss innerhalb eines Taktszyklus abgeschlossen werden. Zeitdiagramme zeigen den Datenfluss durch die Stufen Abruf, Dekodierung, Ausführung und Schreib zurück. Sie helfen dabei, Staus zu identifizieren, bei denen eine Stufe auf eine andere wartet.

Best Practices für die Dokumentation 📝

Durch die Erstellung klarer Zeitdiagramme wird sichergestellt, dass andere Ingenieure Ihre Architektur verstehen können. Befolgen Sie diese Richtlinien für eine effektive Dokumentation.

- Verwenden Sie konsistente Skalen:Stellen Sie sicher, dass die Zeitachse im gesamten Dokument einheitlich ist.

- Beschriften Sie deutlich:Benennen Sie jedes Signal. Vermeiden Sie generische Bezeichnungen wie „Signal 1“.

- Markieren Sie Einschränkungen:Verwenden Sie Klammern oder schraffierte Bereiche, um Setup- und Hold-Fenster zu zeigen.

- Gruppieren Sie verwandte Signale:Halten Sie Steuersignale zusammen und Daten-Signale zusammen.

- Fügen Sie Anmerkungen hinzu:Fügen Sie Notizen hinzu, die komplexe Übergänge oder besondere Verhaltensweisen erklären.

Erweiterte Überlegungen 🔬

Je schneller die Systeme werden, desto komplexer wird die Timing-Analyse. Mehrere Faktoren fügen zusätzliche Schwierigkeiten hinzu.

1. Versorgungsnetzrauschen

Spannungsschwankungen können die Schwellenwerte von Logikgattern verschieben. Dies verändert effektiv die Ausbreitungsverzögerung. Zeitdiagramme müssen die ungünstigsten Spannungsszenarien berücksichtigen.

2. Temperaturvariationen

Elektronische Bauteile verhalten sich bei unterschiedlichen Temperaturen unterschiedlich. Hohe Temperaturen erhöhen den Widerstand und die Verzögerung. Niedrige Temperaturen können die Kapazität beeinflussen. Entwickler müssen die Zeitverhalten über den gesamten Betriebstemperaturbereich hinweg überprüfen.

3. Signaltreue

Lange Spuren auf einer Leiterplatte wirken wie Übertragungsleitungen. Reflexionen und Koppelungen können Signale verzerren. Zeitdiagramme sollten für Hochgeschwindigkeitsverbindungen Augendiagramme oder Signalqualitätsmetriken enthalten.

Schlussfolgerung zur Zeitverzögerungsanalyse 🎯

Zeitdiagramme sind die Karte zur Navigation in der digitalen Logik. Sie übersetzen abstrakte Binärzustände in physikalische Zeitereignisse. Für einen Informatikstudenten ist die Beherrschung des Lesens und Erstellens dieser Diagramme eine zentrale Kompetenz.

Durch das Verständnis von Taktrunden, Ausbreitungsverzögerungen und Setup-Beschränkungen können Sie Systeme entwerfen, die robust und effizient sind. Die Fähigkeit, den Signalfluss visuell darzustellen, verhindert kostspielige Fehler bei der Hardwareentwicklung. Während die Technologie fortschreitet, bleiben die Prinzipien gleich. Die Zeit ist die konstante Variable.

Konzentrieren Sie sich auf die Grundlagen. Üben Sie das Lesen bestehender Diagramme. Zeichnen Sie Ihre eigenen für jeden neuen Schaltkreis, den Sie bauen. Diese Disziplin wird Ihnen in Ihrer technischen Karriere sehr dienen.