La communication en génie repose fortement sur la précision visuelle. Lorsqu’on discute des interactions système, de la propagation des signaux ou du flux de données, un diagramme de timing bien conçu sert de langue universelle. Ces diagrammes capturent les relations entre les événements au fil du temps, permettant aux ingénieurs de diagnostiquer des problèmes, de vérifier la logique et de documenter le comportement du système de manière efficace. Toutefois, un diagramme encombré, ambigu ou mal échelonné peut entraîner des malentendus coûteux. Ce guide expose les normes essentielles pour créer des diagrammes qui transmettent la vérité technique sans confusion.

📊 Comprendre les bases des diagrammes de timing

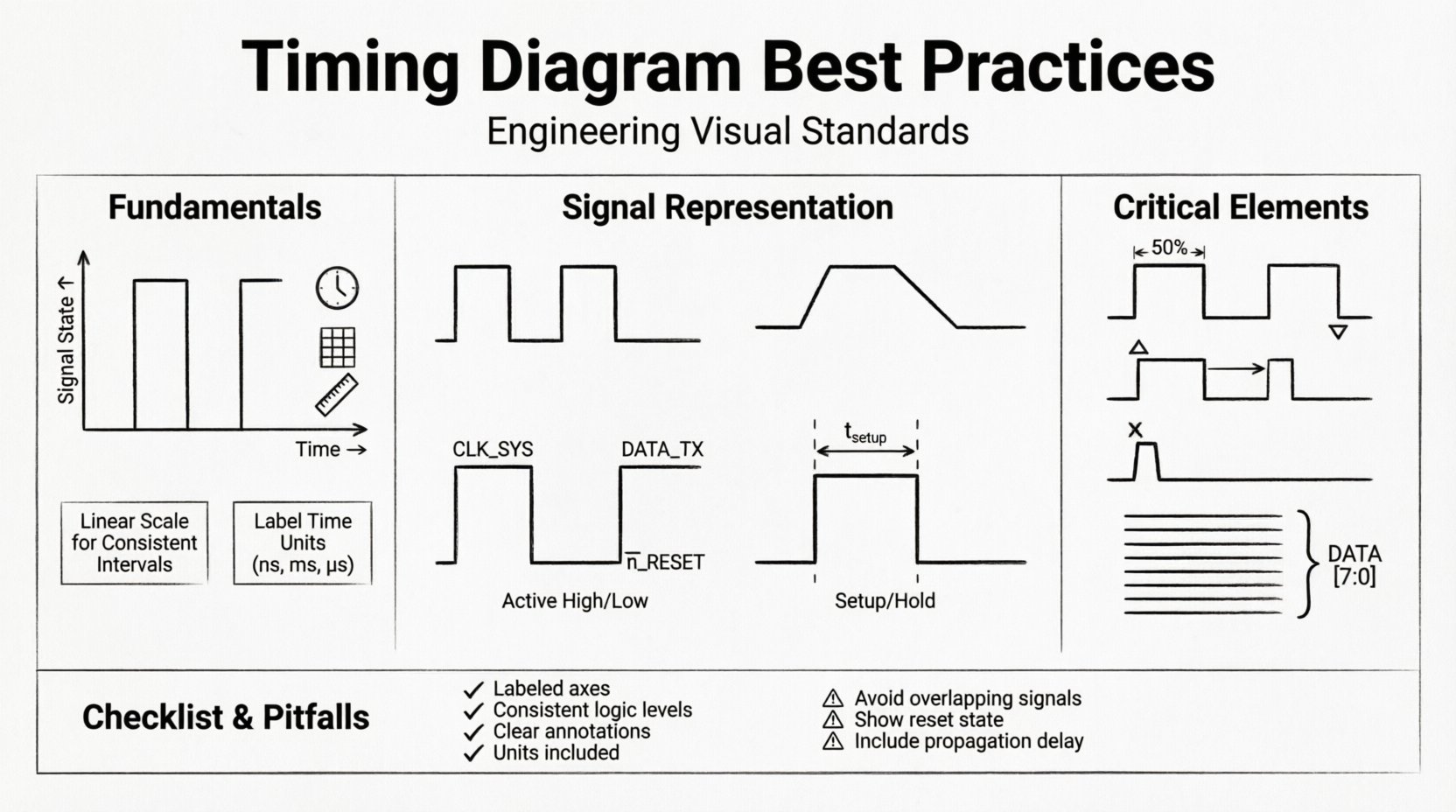

Un diagramme de timing est une représentation graphique de la manière dont les signaux changent d’état au fil du temps. Ce n’est pas simplement un dessin ; c’est une spécification. Que vous travailliez sur des interfaces matériels, des systèmes embarqués ou des protocoles logiciels, le principe fondamental reste le même : le temps s’écoule horizontalement, et les états des signaux sont tracés verticalement. Dans ce contexte, la clarté n’est pas un luxe ; c’est une exigence pour la sécurité et la fiabilité.

Lors de la création de ces visuels, l’objectif est de réduire la charge cognitive du lecteur. Il ne doit pas deviner où commence l’horloge, quelle ligne représente les données ou quelles sont les seuils de tension. Chaque élément doit avoir une fonction précise.

- Axe du temps : La dimension horizontale représente l’évolution du temps. Elle peut être linéaire ou logarithmique selon les événements à capturer.

- Lignes de signal : La dimension verticale représente l’état d’un signal, tel que Haut/Bas, 1/0 ou niveaux de tension.

- Événements : Points précis dans le temps où des changements se produisent, tels que des fronts, des impulsions ou des transferts de données.

📏 Configuration de votre canevas et de l’échelle

La base d’un diagramme clair est la grille. Sans échelle cohérente, la relation entre les événements devient déformée. Un croquis qui semble correct à un niveau de zoom peut révéler des violations critiques de timing à un autre niveau.

1. Définition de l’échelle du temps

Les échelles du temps doivent être choisies en fonction de l’événement le plus rapide du système. Si vous documentez une interaction au niveau du microseconde, dessiner la timeline en millisecondes masquera les détails. À l’inverse, si les événements s’étendent sur plusieurs secondes, une échelle en microseconde génère un bruit inutile. Marquez toujours clairement l’unité de temps sur l’axe.

- Échelle linéaire : Utilisez-la pour des intervalles constants. C’est la norme pour la documentation de la plupart des protocoles.

- Échelle logarithmique : Peu utilisée, mais nécessaire lorsque les événements couvrent plusieurs ordres de grandeur (par exemple, les délais de démarrage par rapport aux temps de traitement).

2. Lignes de grille et points de repère

Les lignes de grille aident l’œil à suivre les intervalles de temps dans le diagramme. Les lignes de grille épaisses doivent marquer les unités majeures (par exemple, 10 ms), tandis que les lignes plus fines marquent les unités mineures (par exemple, 1 ms). Cette hiérarchie visuelle empêche le lecteur de perdre le fil.

Assurez-vous que les lignes verticales de grille s’alignent avec les événements importants. Si un front d’horloge tombe exactement sur une ligne de grille, cela fournit un repère naturel pour lire les temps de setup et de hold. Ne forcez pas les événements à s’adapter à la grille s’ils représentent des mesures du monde réel ; ajustez plutôt la grille ou utilisez des annotations pour indiquer le décalage.

⚡ Représenter les signaux avec précision

La manière dont un signal est dessiné détermine sa lecture. Un front montant implique une transition du bas vers le haut, mais la vitesse et la forme de cette transition peuvent porter une signification concernant l’intégrité du signal.

1. États et niveaux des signaux

Définissez clairement ce qui constitue un état logique. En logique numérique, il s’agit généralement de 0 (Bas) et de 1 (Haut). Dans les contextes analogiques ou mixtes, des niveaux de tension (par exemple, 0 V à 5 V) sont requis. Utilisez des styles de traits distincts pour distinguer entre :

- Actif haut : Le signal est vrai lorsque la ligne est au niveau supérieur.

- Actif bas : Le signal est vrai lorsque la ligne est au niveau inférieur (souvent indiqué par une barre au-dessus du nom du signal).

2. Représentation des arêtes

Les arêtes sont la partie la plus critique du schéma. Elles indiquent précisément le moment où un changement d’état se produit. Utilisez des lignes nettes et continues pour les transitions idéales. Si vous devez représenter des taux de montée physiques ou des temps de montée, dessinez-les sous forme de lignes inclinées plutôt que de pics verticaux.

Évitez les lignes dentelées sauf si vous documentez spécifiquement du bruit ou des instabilités. Les lignes nettes suggèrent une stabilité ; les lignes dentelées suggèrent une interférence. Soyez intentionnel quant à la forme que vous dessinez.

3. Conventions de nommage des signaux

Un nom de signal n’est pas seulement une étiquette ; c’est une définition. Évitez les noms génériques commeSignal_A ou Fil_1. Utilisez plutôt des noms fonctionnels qui décrivent l’objectif, tels queHORLOGE_SYS ou DONNEES_TX.

- Préfixes : Utilisez des préfixes standards pour indiquer le type de signal (par exemple,

Npour la logique négative,HORpour l’horloge). - Cas : Utilisez des majuscules pour les constantes et les signaux, un mélange de majuscules et de minuscules pour les variables si pertinent.

- Consistance : Assurez-vous que le nom sur le schéma correspond exactement au nom dans le code ou la fiche technique.

⏱️ Horloging et synchronisation

Les horloges pilotent le timing des systèmes synchrones. Une représentation incorrecte d’une horloge peut invalider l’ensemble du schéma. Le signal d’horloge est souvent le premier point de référence que le lecteur vérifie.

1. Cycle de travail et période

Dessinez le signal d’horloge avec un cycle de travail constant, sauf si le système exige spécifiquement un timing variable. Si le cycle de travail n’est pas de 50 %, indiquez les durées haute et basse. La période (le temps pour un cycle complet) doit être clairement indiquée.

Pour les systèmes à fréquence variable, ne supposez pas qu’une longueur de ligne constante représente un temps constant. Marquez chaque période individuellement si elles diffèrent significativement.

2. Déclenchement sur front

Indiquez si le système se déclenche sur le front montant (positif) ou le front descendant (négatif). Vous pouvez utiliser des flèches ou de petits triangles au niveau du front. Cela est crucial pour comprendre quand les données sont échantillonnées.

- Front montant : Marquez avec un petit triangle pointant vers le haut.

- Front descendant : Marquez avec un petit triangle pointant vers le bas.

3. Jitter et phase

Dans les systèmes à haute vitesse, le jitter (variation du timing) est un facteur connu. Si vous dessinez un idéal théorique, des lignes droites conviennent. Si vous documentez un comportement mesuré, utilisez une région ombrée ou plusieurs tracés pour montrer la variance. Les relations de phase entre plusieurs horloges doivent être explicitement indiquées.

🔄 Gestion des transitions de données

Les signaux de données sont souvent plus complexes que les horloges. Ils évoluent en fonction de l’état du système. Documenter correctement ces transitions exige une attention portée à la relation entre les données et l’horloge.

1. Temps de setup et temps de maintien

Ce sont des contraintes critiques pour une capture de données fiable. Le temps de setup est la durée avant le front de l’horloge pendant laquelle les données doivent être stables. Le temps de maintien est la durée après le front de l’horloge pendant laquelle les données doivent rester stables. Visualisez-les comme des fenêtres par rapport au front de l’horloge.

Tracez des lignes verticales pointillées pour indiquer les fenêtres de setup et de maintien. Indiquez la durée en unités de temps (par exemple, t_setup = 5 ns). Cela visualise la marge disponible pour que le système fonctionne correctement.

2. Métastabilité

Lorsque les signaux traversent des domaines d’horloge, la métastabilité peut survenir. Il s’agit d’un état où le signal n’est ni complètement haut ni bas. Représentez-le par une ligne pointillée ou un hachurage spécifique dans la fenêtre de timing. Documenter cela avertit le lecteur que le signal pourrait prendre plus de temps que d’habitude pour se stabiliser.

3. Glissements et bruit

Des impulsions parasites, appelées glissements, peuvent provoquer des erreurs logiques. Si un glissement est un problème connu, dessinez-le comme une impulsion étroite qui ne respecte pas la largeur minimale requise par la logique réceptrice. Ne cachez pas ces artefacts ; ils sont souvent à l’origine des pannes intermittentes.

🏷️ Annotation et étiquetage

Le texte sur un schéma a de l’importance. Surcharger le schéma de texte le rend illisible. Un étiquetage insuffisant le rend ambigu. Trouvez un équilibre grâce à un placement stratégique.

1. Positionnement du texte

Placez le texte près de la partie pertinente du signal, mais évitez de superposer avec les lignes du signal. Utilisez des lignes d’attache (lignes fines reliant le texte au signal) si le signal est trop chargé pour accueillir le texte directement au-dessus ou au-dessous.

2. Unités et symboles

Incluez toujours les unités. Le temps doit être exprimé en secondes, millisecondes ou nanosecondes. La tension doit être en volts. Ne comptez pas sur le lecteur pour deviner. Utilisez des symboles standards pour les opérations logiques (par exemple, ! pour NON, & pour ET) si vous montrez des équations logiques aux côtés du timing.

3. Lisible

La taille de police est importante. Dans un document imprimé ou à l’écran, le texte doit être lisible sans zoomer. Si le schéma est complexe, envisagez de le diviser en plusieurs vues : un aperçu général et un agrandissement détaillé d’événements spécifiques.

🚫 Pièges courants à éviter

Même les ingénieurs expérimentés commettent des erreurs lors de la création de ces visuels. Être conscient des erreurs courantes peut économiser des heures de débogage.

- Ignorer le délai de propagation :Les signaux mettent du temps à voyager à travers les fils et les portes logiques. Si un signal change au point A et arrive au point B, dessinez le délai. Une ligne verticale au point B implique un déplacement instantané, ce qui est physiquement impossible.

- Niveaux logiques inconstants : Assurez-vous que la définition de Haut et Bas ne change pas au milieu du schéma. Cela est confus et dangereux.

- Signaux superposés : Si deux signaux doivent se croiser, assurez-vous qu’ils sont clairement distinguables. Utilisez des épaisseurs de ligne différentes ou des couleurs si le support de sortie le permet.

- États de réinitialisation manquants : Les systèmes commencent souvent dans un état spécifique. Montrez l’état initial avant que l’horloge ne commence à fonctionner. Cela évite toute confusion sur ce que font les signaux à l’instant zéro.

🧠 Considérations avancées

À mesure que les systèmes deviennent plus complexes, les diagrammes de temporisation doivent évoluer pour gérer les scénarios multi-canaux et asynchrones.

1. Temporisation multi-canaux

Lorsque vous traitez des bus (comme les bus de données), regroupez les signaux connexes. Utilisez un crochet pour indiquer que les lignes au-dessus représentent la largeur du bus (par exemple, DATA[7:0]). Montrez la transition de l’ensemble pour indiquer un transfert parallèle.

2. Synchronisation asynchrone

Tous les systèmes n’utilisent pas une horloge globale. Les protocoles de synchronisation reposent sur des signaux de demande et d’acquittement. Dessinez-les clairement avec des flèches indiquant le sens de la synchronisation. Montrez les états d’attente où le système s’arrête jusqu’à la réception du signal.

3. États de gestion de l’alimentation

Les systèmes modernes entrent en mode faible consommation. Indiquez ces transitions sur le diagramme de temporisation. Un signal peut descendre à bas pour indiquer le mode veille, mais l’horloge peut s’arrêter ou ralentir. Documentez l’état d’alimentation aux côtés de l’état de temporisation.

✅ Liste de vérification

Avant de finaliser un schéma, passez en revue cette liste de vérification pour vous assurer de respecter les meilleures pratiques.

| Élément de vérification | Critères |

|---|---|

| Axe du temps | L’échelle est-elle linéaire et étiquetée avec des unités ? |

| Noms des signaux | Tous les signaux sont-ils nommés de manière fonctionnelle et cohérente ? |

| Bords de l’horloge | Les bords montants/descendants sont-ils clairement marqués ? |

| Transitions | Les temps de setup/hold sont-ils visibles et étiquetés ? |

| Delais | Les délais de propagation sont-ils inclus là où cela est pertinent ? |

| Annotations | Le texte est-il lisible et sans chevauchement ? |

| Unités | Toutes les mesures sont-elles accompagnées d’unités (ns, V, etc.) ? |

| État initial | L’état de réinitialisation ou d’attente est-il affiché au départ ? |

| Clarté | Un ingénieur pair peut-il interpréter cela sans poser de questions ? |

📝 Réflexions finales sur la documentation

La qualité d’un diagramme de timing reflète la qualité de l’ingénierie qui se cache derrière. Un diagramme clair facilite la collaboration entre les équipes matérielles et logicielles, réduit le temps de débogage et garantit que les futurs mainteneurs comprennent le comportement du système. C’est un outil de vérité, et non seulement un simple outil de représentation.

Concentrez-vous sur la précision plutôt que sur l’esthétique. Bien qu’un diagramme attrayant soit agréable, un diagramme correct est essentiel. Prenez le temps de vérifier les mesures, étiquetez chaque contrainte, et alignez votre langage visuel avec les spécifications techniques. En suivant ces pratiques, vous assurez que les informations de timing sont conservées avec précision tout au long du cycle de vie du produit.

Souvenez-vous, le diagramme est un contrat. Il définit le comportement du système. Chaque fois que vous tracez une ligne, vous faites une promesse concernant le comportement du signal. Gardez cette promesse claire, précise et sans ambiguïté.

Adopter ces normes améliore le professionnalisme de votre documentation. Elle signale à votre équipe et à vos parties prenantes que vous valorisez la fiabilité et la clarté. Dans le monde complexe de la conception de systèmes, un bon diagramme est souvent la différence entre un lancement réussi et un problème récurrent.

🔧 Conclusion

Créer des diagrammes de timing efficaces exige une approche rigoureuse en matière de mise en page, d’étiquetage et de représentation. En privilégiant la clarté, la cohérence et la précision technique, les ingénieurs peuvent produire des visuels qui servent de références fiables pour le développement et la maintenance. Suivez les directives concernant la représentation des signaux, la synchronisation horaire et les annotations pour garantir que votre documentation résiste à l’épreuve du temps et de la complexité.