En électronique numérique et en génie informatique, comprendre la relation temporelle entre les signaux est fondamental pour la fiabilité du système. Un diagramme de temporisation sert de langage visuel principal pour décrire ces relations. Il représente les états des signaux en fonction d’un axe temporel, permettant aux ingénieurs de visualiser le flux de données, la synchronisation d’horloge et les éventuels risques au sein d’un circuit. Ce guide explore les éléments structurels, les motifs opérationnels et les scénarios critiques rencontrés dans l’analyse des signaux.

Que ce soit pour concevoir des circuits intégrés ou déboguer des systèmes embarqués, la capacité à interpréter et à créer des représentations temporelles précises est une compétence fondamentale. Ce document fournit un aperçu technique sur la manière dont les signaux interagissent, les contraintes qu’ils doivent respecter, et les pièges courants rencontrés lors de la vérification.

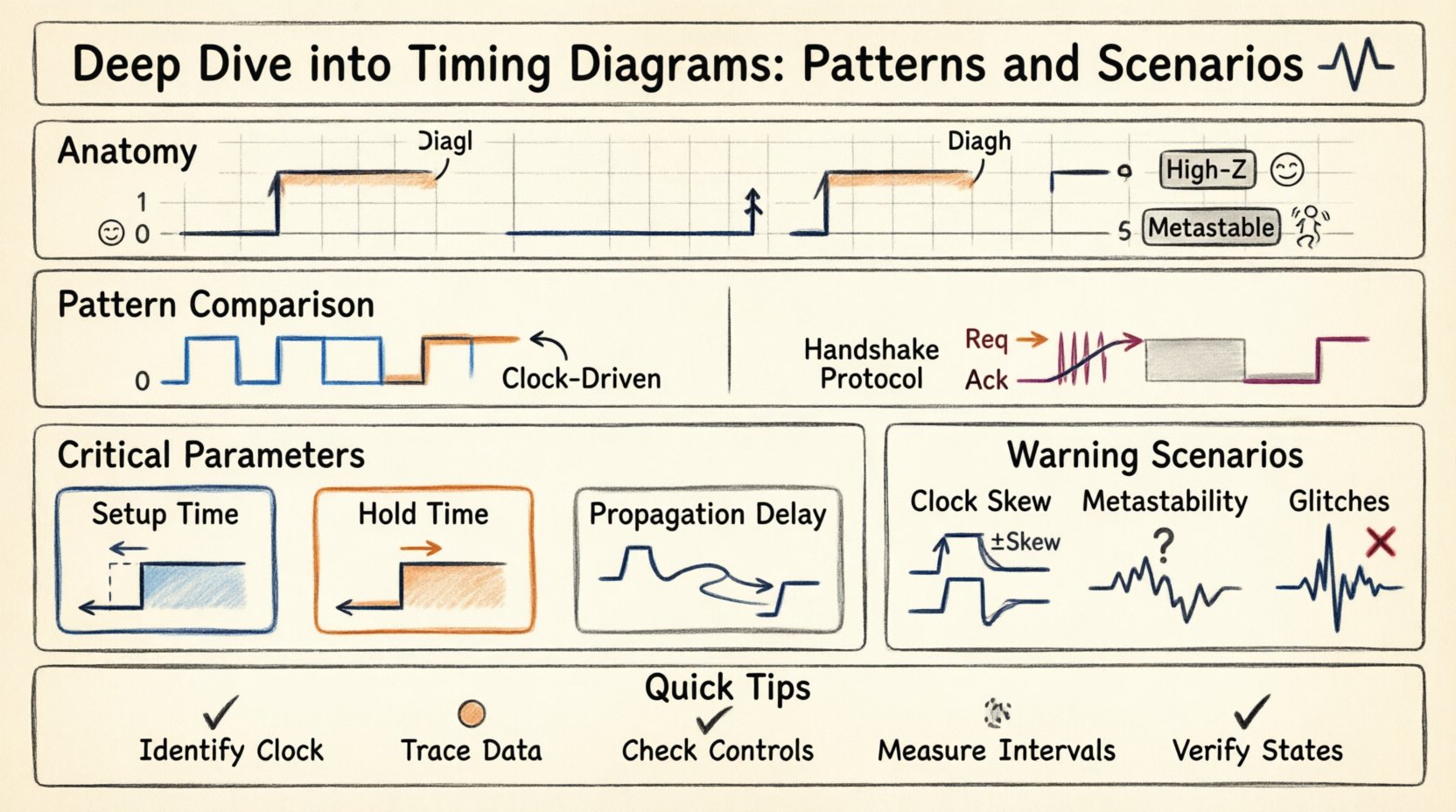

📐 Anatomie d’un diagramme de temporisation

Un diagramme de temporisation est une représentation graphique où l’axe horizontal représente le temps et l’axe vertical représente les niveaux de signal. Chaque ligne horizontale correspond à un signal ou un réseau spécifique dans la conception. Comprendre les composants est la première étape vers une analyse précise.

- Axe temporel : Généralement tracé horizontalement de gauche à droite. Il peut être linéaire ou logarithmique, selon l’échelle des événements observés.

- Lignes de signal : Traces individuelles représentant les niveaux de tension. Une tension élevée indique généralement un état logique 1, tandis qu’une tension faible indique un état logique 0.

- Transitions : Lignes verticales indiquant un changement d’état, tel qu’une transition montante (0 vers 1) ou descendante (1 vers 0).

- Étiquettes : Annotations textuelles identifiant des signaux spécifiques, des broches ou des lignes de contrôle.

- Repères : Lignes verticales pointillées souvent utilisées pour indiquer des événements spécifiques, tels qu’une impulsion d’horloge ou un déclenchement de réinitialisation.

🔢 Niveaux et états logiques

Les signaux numériques n’existent pas toujours strictement à 0 ou 1. Dans des scénarios pratiques, les signaux peuvent exister dans des états indéfinis ou des états de haute impédance. Un diagramme complet doit tenir compte de ces variations.

- Niveau logique haut (1) : Le signal est porté à un niveau de tension reconnu comme étant logiquement vrai.

- Niveau logique bas (0) : Le signal est porté à un niveau de tension reconnu comme étant logiquement faux.

- Haut-Z : Le signal est déconnecté du conducteur, flottant effectivement. Cela est courant dans les tampons à trois états.

- Métastable : Un état où le signal n’est ni haut ni bas, souvent observé lors de transitions asynchrones.

⚙️ Motifs de temporisation courants

Les conceptions suivent des motifs prévisibles pour assurer l’intégrité des données. Ces motifs définissent la manière dont les données se déplacent par rapport aux signaux de contrôle. Reconnaître ces motifs aide à vérifier qu’une conception répond à ses spécifications.

📌 Transfert de données synchrone

Les conceptions synchrones reposent sur un signal d’horloge global pour coordonner les actions. Les données ne sont échantillonnées qu’à des moments précis, généralement au front montant ou descendant de l’horloge.

- Commandé par l’horloge : Tous les changements d’état se produisent par rapport au front d’horloge.

- Validité des données : Les données doivent être stables avant le front d’horloge et rester stables après celui-ci.

- Propagation : Il y a un délai entre le front d’horloge et le changement de la sortie.

📌 Synchronisation asynchrone

La communication asynchrone ne repose pas sur une horloge partagée. Elle utilise plutôt des signaux de contrôle pour indiquer quand les données sont prêtes et quand elles ont été reçues.

- Demande (Req) : L’expéditeur indique que les données sont disponibles.

- Accusé de réception (Ack) : Le récepteur indique que les données ont été acceptées.

- États d’attente : L’expéditeur peut s’arrêter jusqu’à ce que le récepteur soit prêt.

| Fonctionnalité | Schéma synchrone | Schéma asynchrone |

|---|---|---|

| Coordination | Signal d’horloge global | Signaux de handshake de contrôle |

| Vitesse | Généralement plus élevée | Variable, dépendante de la réponse |

| Complexité | Réseau de distribution d’horloge | Logique du protocole |

| Latence | Prévisible | Variable |

⏱️ Paramètres de temporisation critiques

Au-delà des lignes visuelles, des contraintes numériques spécifiques définissent si un circuit fonctionnera correctement. Ces paramètres sont critiques pour l’analyse statique de temporisation et doivent être vérifiés par rapport aux limites physiques.

🛑 Temps de setup

Le temps de setup est la durée minimale pendant laquelle le signal de données doit rester stable avant l’edge d’horloge. Si les données changent trop près de l’edge d’horloge, le bascule réceptrice peut ne pas capturer la bonne valeur.

- Mesure : Mesuré à partir de l’edge actif d’horloge en reculant dans le temps.

- Risque : Une violation entraîne une capture incorrecte des données.

- Exigence : Le délai du chemin de données doit être suffisamment long pour respecter la fenêtre de setup.

🛑 Temps de maintien

Le temps de maintien est la durée minimale pendant laquelle le signal de données doit rester stable après l’edge d’horloge. Cela garantit que le verrou a suffisamment de temps pour verrouiller la valeur d’entrée.

- Mesure : Mesuré à partir de l’edge actif d’horloge en avançant dans le temps.

- Risque : Une violation entraîne une métastabilité ou la capture de données incorrectes.

- Exigence : Le délai du chemin de données doit être suffisamment court pour permettre la fenêtre de maintien.

⚡ Délai de propagation

Il s’agit du temps nécessaire à un signal pour voyager depuis l’entrée d’une porte logique jusqu’à sa sortie. Il varie en fonction de la capacité de charge et de la résistance interne du transistor.

- tpd (Haut vers Bas) : Temps de transition de 1 à 0.

- tpd (Bas vers Haut) : Temps de transition de 0 à 1.

- Désynchronisation : Différences de délai entre des chemins parallèles.

🚨 Scénarios critiques de temporisation

Certains scénarios présentent des défis importants qui nécessitent une analyse soigneuse. Ces situations impliquent souvent des interactions entre différents domaines d’horloge ou des limitations physiques du matériel.

🔄 Désynchronisation d’horloge

La désynchronisation d’horloge se produit lorsque le signal d’horloge arrive à différents composants à des moments différents. Cela peut se produire en raison de différences de routage ou de distance physique.

- Désynchronisation positive : L’horloge de destination arrive plus tard que l’horloge source.

- Désynchronisation négative : L’horloge de destination arrive plus tôt que l’horloge source.

- Impact : Peut réduire efficacement les marges de temps de configuration ou augmenter les violations de temps de maintien.

🌊 Métastabilité

La métastabilité est un état où la sortie d’un bascule n’est ni haute ni basse. Elle se produit généralement lorsque les temps de configuration ou de maintien sont violés, notamment dans les croisements asynchrones.

- Résolution : Le circuit finit par atteindre un état stable, mais le temps nécessaire est imprévisible.

- Solution : Utiliser des synchronisateurs (bascules à plusieurs étages) pour réduire la probabilité d’échec.

- MTBF : Le temps moyen entre les défaillances est calculé en fonction des taux de résolution de la métastabilité.

📉 Glissements

Les glissements sont des pics de courte durée dans le signal qui peuvent être confondus avec des transitions valides. Ils surviennent souvent en raison de différences de délais de propagation le long de chemins différents.

- Causes : Longueurs de chemin inégales ou conditions de course.

- Effet : Peut déclencher des changements d’état non désirés dans la logique en aval.

- Atténuation : Utiliser une logique de filtrage ou garantir une fermeture temporelle correcte.

🔍 Analyse des formes d’onde

Lors de la revue d’un diagramme temporel, une approche systématique garantit que aucun détail n’est négligé. Les ingénieurs doivent suivre le flux des signaux de données et de contrôle pour identifier les écarts.

🔍 Analyse étape par étape

- Identifier l’horloge : Localiser le signal d’horloge principal. Déterminer s’il est déclenché sur front montant ou front descendant.

- Suivre les chemins de données : Suivez les lignes de données depuis la source jusqu’à la destination.

- Vérifiez les signaux de contrôle :Vérifiez que les signaux d’activation, de réinitialisation et d’effacement sont correctement activés.

- Mesurez les intervalles :Calculez le temps entre des événements spécifiques pour vérifier les exigences de configuration et de maintien.

- Vérifiez les transitions d’état :Assurez-vous que l’état de sortie correspond à la fonction logique attendue.

🔍 Lecture des déclencheurs sur front

Comprendre comment un composant réagit aux fronts des signaux est essentiel.

- Déclenchement sur front montant :L’action a lieu lors de la transition du bas au haut.

- Déclenchement sur front descendant :L’action a lieu lors de la transition du haut au bas.

- Déclenchement sur niveau :L’action a lieu tant que le signal reste à un niveau spécifique.

🛠️ Normes de documentation

Une documentation claire garantit que les conceptions sont comprises par d’autres ingénieurs. La cohérence dans la notation et l’étiquetage empêche les malentendus lors du débogage ou du transfert.

📝 Conventions d’étiquetage

- Noms des signaux :Utilisez des conventions de nommage cohérentes (par exemple,

clk,rst_n,data_in). - Polarité :Indiquez clairement les signaux actifs bas, souvent avec une barre ou un suffixe.

- Unités :Indiquez clairement les unités de temps (ns, µs, ms) sur l’axe des temps.

- Échelle : Assurez-vous que l’échelle de temps est adaptée aux événements affichés.

📝 Clarté visuelle

- Espacement : Évitez autant que possible les lignes superposées.

- Contraste : Utilisez des couleurs distinctes ou des épaisseurs de trait différentes pour les différents types de signaux.

- Annotations : Ajoutez des notes expliquant des comportements complexes ou des contraintes spécifiques.

- Grille : Utilisez un fond quadrillé pour aider à mesurer les intervalles de temps.

🚧 Flux de dépannage

Lorsqu’un design ne respecte pas les contraintes de timing, un processus de dépannage structuré aide à identifier la cause racine. Cela implique d’examiner le schéma à la lumière des contraintes physiques.

🚧 Identification des violations

- Vérifier le temps de préparation : Les données arrivent-elles trop tard par rapport à l’horloge ?

- Vérifier le temps de maintien : Les données changent-elles trop tôt après l’horloge ?

- Vérifier la fréquence de l’horloge : La période de l’horloge est-elle plus courte que le minimum requis ?

🚧 Stratégies d’atténuation

- Registres de pipeline : Insérez des registres supplémentaires pour interrompre les chemins combinatoires longs.

- Gestion d’horloge : Réduisez l’activité pour diminuer la consommation d’énergie et améliorer potentiellement le timing.

- Insertion de tampons : Ajoutez des tampons pour équilibrer les délais sur les chemins parallèles.

- Contraintes de timing : Définissez des chemins faux pour exclure la logique qui n’affecte pas le flux de données.

📈 Meilleures pratiques pour la conception

Adopter les meilleures pratiques pendant la phase de conception réduit la probabilité de problèmes de timing plus tard dans le cycle de développement. Une planification proactive est plus efficace qu’une correction réactive.

- Standardiser les interfaces :Utiliser des protocoles connus pour le transfert de données afin de simplifier la vérification du timing.

- Minimiser les chemins asynchrones :Réduire au minimum les interactions asynchrones afin de diminuer les risques de métastabilité.

- Documenter les hypothèses :Préciser clairement les fréquences d’horloge et les niveaux de tension dans les spécifications du design.

- Réviser régulièrement :Effectuer des revues de timing à chaque étape majeure du projet.

🎯 Résumé des concepts clés

Les diagrammes de timing sont des outils essentiels pour visualiser le comportement temporel des systèmes numériques. Ils révèlent comment les signaux de données et de contrôle interagissent au fil du temps, mettant en évidence des contraintes critiques telles que les temps de setup et de hold. En comprenant l’anatomie de ces diagrammes, les ingénieurs peuvent identifier des motifs, prévoir des erreurs et garantir des performances systémiques robustes.

Les points clés incluent la distinction entre les motifs synchrones et asynchrones, l’importance de la gestion du décalage d’horloge, et la nécessité de normes claires de documentation. Respecter ces principes facilite la conception fiable et simplifie le processus de vérification.

L’analyse continue des données de forme d’onde garantit que les conceptions restent dans les limites opérationnelles. À mesure que la technologie progresse et que les fréquences d’horloge augmentent, la précision requise dans l’analyse du timing devient encore plus critique. La maîtrise de ces concepts permet la création d’architectures numériques stables et à haute performance.