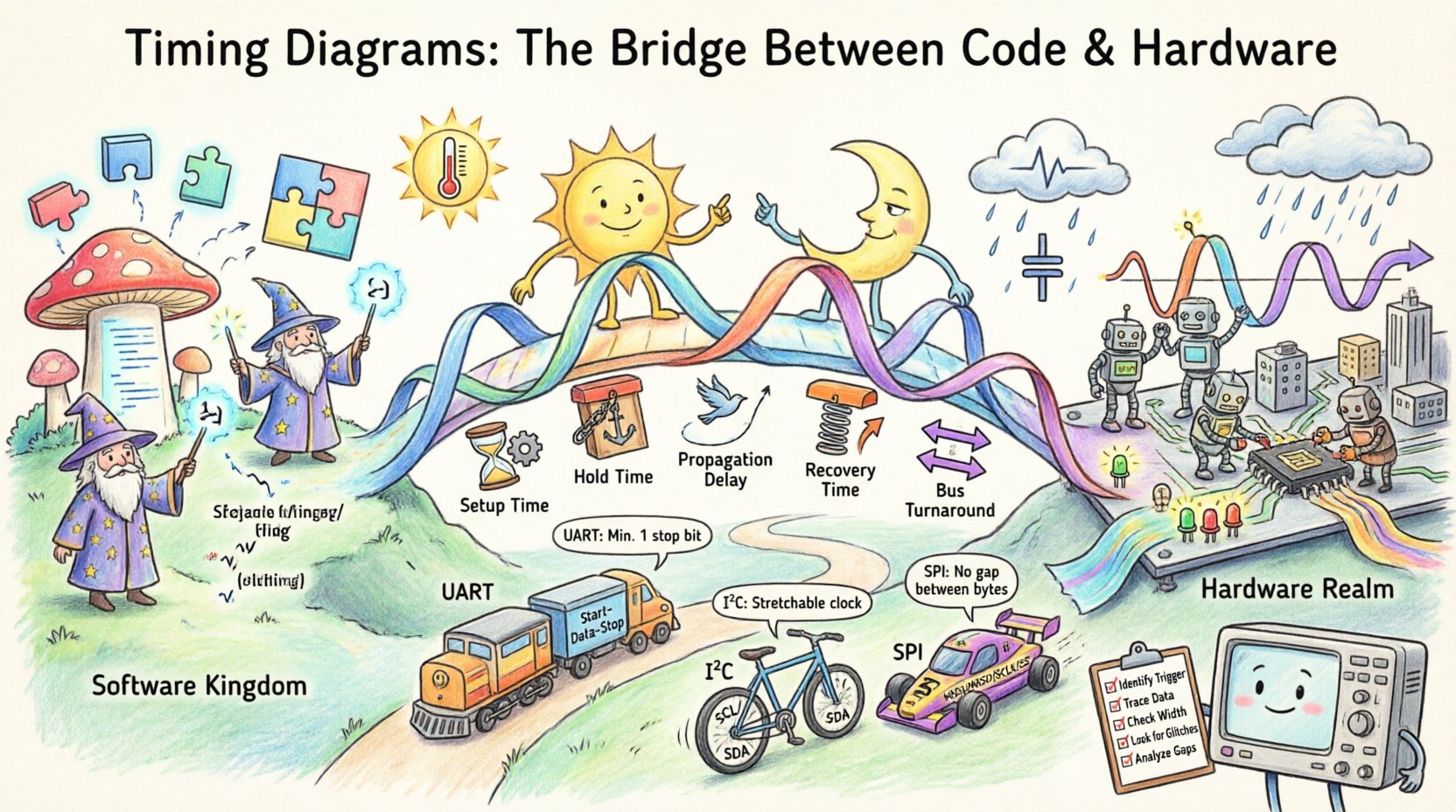

Lorsque les ingénieurs logiciels écrivent du code, ils pensent en instructions, variables et flux logiques. Lorsque les ingénieurs matériels conçoivent des circuits, ils pensent en niveaux de tension, délais de propagation et cycles d’horloge. Ces deux mondes existent souvent dans un état de friction. Le code s’attend à ce qu’un signal arrive à un moment logique précis, mais le matériel fonctionne selon le temps physique, sujet au bruit, à la température et à la résistance électrique. Le pont entre ces deux domaines est le diagramme de timing.

Un diagramme de timing n’est pas simplement une image ; c’est un contrat. Il définit la relation précise entre des événements dans le temps. Il indique au firmware à quel moment il est sûr de lire une broche, et au silicium à quel moment il est sûr de piloter une ligne. Sans une compréhension claire de ces diagrammes, les systèmes embarqués échouent de manière imprévisible. La corruption des données, les conditions de course et les blocages du système deviennent des problèmes fréquents. Ce guide explore les mécanismes des diagrammes de timing, la physique derrière eux, et comment les lire et les créer efficacement.

📊 L’anatomie d’un signal

Au cœur de la logique numérique repose l’utilisation d’états binaires. Dans le monde physique, ces états sont représentés par des niveaux de tension. Un « haut » pourrait être de 3,3 volts, et un « bas » de 0 volt. Mais les signaux ne changent pas instantanément. Ils montent et descendent sur une période finie. Un diagramme de timing visualise cette transition.

Comprendre le langage visuel de ces diagrammes est la première étape vers la maîtrise. Les éléments clés incluent :

- Axe du temps : Habituellement horizontal, allant de gauche à droite. Il peut être linéaire ou logarithmique, bien que le linéaire soit la norme pour la plupart des analyses logiques.

- Lignes de signal : Des lignes verticales représentant des fils spécifiques, des broches ou des nœuds internes.

- Transitions : Le passage du bas au haut (front montant) ou du haut au bas (front descendant). Ces fronts déclenchent souvent des changements d’état dans la logique séquentielle.

- Niveaux : L’état stable d’un signal avant ou après une transition.

- Étiquettes : Des annotations textuelles qui précisent le sens d’une impulsion ou d’un intervalle spécifique.

Prenons un signal d’horloge simple. Il oscille entre haut et bas. Le temps nécessaire pour effectuer un cycle complet est la période. L’inverse de la période est la fréquence. Dans un diagramme de timing, l’horloge agit comme le battement du cœur du système. Tous les autres signaux sont souvent synchronisés sur ces fronts.

🕰️ Le domaine d’horloge

La plupart des systèmes numériques fonctionnent dans un domaine d’horloge. Il s’agit d’un groupe de circuits qui partagent la même référence temporelle. Toutefois, les signaux traversent souvent différents domaines. Cela introduit de la complexité. Un signal généré dans un domaine rapide pourrait arriver trop tard pour un domaine lent, ou trop tôt, provoquant une violation de maintien.

Lors de l’analyse du timing, vous devez tenir compte de :

- Désynchronisation d’horloge : La différence de temps d’arrivée du signal d’horloge entre différents composants. Si l’horloge arrive au destinataire avant l’émetteur, les marges de timing se réduisent.

- Décalage de phase : Dans certains systèmes, les signaux ne sont pas alignés sur le front d’horloge, mais surviennent au milieu du cycle.

- Jitter : Des variations dans le timing d’un signal. Le jitter peut être aléatoire ou déterministe. Il réduit la marge de bruit et rend le diagramme moins prévisible.

Le code écrit pour interagir avec le matériel suppose une horloge stable. Si l’horloge physique dérive en raison de fluctuations de température ou de tension, le diagramme de timing ne correspond plus à la réalité. C’est pourquoi les diagrammes de timing doivent inclure des bandes de tolérance ou des scénarios au pire cas.

⚙️ Paramètres de timing critiques

Des paramètres spécifiques définissent les limites de l’intégrité du signal. Ces valeurs se trouvent souvent dans les fiches techniques, mais sont mieux comprises dans le contexte d’un diagramme de timing. Le tableau suivant présente les paramètres les plus critiques que les ingénieurs doivent évaluer.

| Paramètre | Définition | Impact sur le système |

|---|---|---|

| Temps de préparation | Le temps minimal pendant lequel les données doivent rester stablesavantl’arête de l’horloge. | Si ce délai est violé, le bascule réceptrice ne peut pas capturer la bonne valeur. |

| Temps de maintien | Le temps minimal pendant lequel les données doivent rester stablesaprèsl’arête de l’horloge. | Si ce délai est violé, la bascule peut entrer dans un état métastable. |

| Délai de propagation | Temps nécessaire pour qu’un signal se propage de l’entrée à la sortie. | Les délais s’accumulent à travers les portes logiques, pouvant entraîner la perte de cycles d’horloge. |

| Temps de récupération | Temps nécessaire pour qu’un signal de contrôle revienne à son état normal après un événement asynchrone. | Influence la vitesse de récupération du système après une réinitialisation ou une interruption. |

| Temps de retournement du bus | Temps nécessaire pour passer un bus du mode sortie au mode entrée. | Crucial pour les bus bidirectionnels comme I2C ou 1-Wire. |

La violation de ces paramètres ne provoque pas toujours un crash immédiat. Parfois, le système fonctionne à 99 % du temps et ne tombe en panne que dans des conditions spécifiques. C’est pourquoi l’analyse des délais est un processus itératif. Vous devez vérifier que le schéma reste valable dans des conditions extrêmes de tension et de température.

👀 Lecture du signal

Lire un diagramme temporel exige une approche systématique. Lors du débogage d’un problème matériel, ne regardez pas seulement les niveaux des signaux. Observez les relations entre les signaux.

Suivez ces étapes pour analyser un signal :

- Identifiez le déclencheur :Trouvez l’événement qui déclenche la séquence. Il s’agit généralement d’une arête d’horloge ou d’une interruption externe.

- Suivez les données :Suivez les lignes de données par rapport au déclencheur. Les données apparaissent-elles avant ou après l’arête d’horloge ?

- Vérifiez la largeur Mesurez la durée des impulsions. Un signal « Haut » est-il suffisamment long pour être reconnu par la logique réceptrice ?

- Recherchez les parasites :Impulsions parasites qui surviennent entre des états stables. Elles peuvent être causées par des interférences ou des aléas logiques.

- Analysez l’intervalle :Examinez le temps entre la fin d’une transaction et le début de la suivante. Y a-t-il assez de temps pour que le matériel se réinitialise ?

Souvent, le problème réside dans l’intervalle. Si un microcontrôleur termine l’écriture de données vers une périphérie, il peut nécessiter un délai spécifique avant d’envoyer le prochain octet. Si le schéma montre ces octets consécutifs sans intervalle, le code est probablement trop ambitieux par rapport au matériel.

🔌 Protocoles courants et temporisation

Les différents protocoles de communication imposent des contraintes de temporisation différentes. Comprendre ces contraintes est essentiel pour écrire un microprogramme qui communique de manière fiable.

| Protocole | Caractéristique temporelle clé | Mode de défaillance courant |

|---|---|---|

| UART | Bit de départ suivi par les bits de données et un bit d’arrêt. Dépend du débit baud. | Erreurs de bits dues au décalage d’horloge entre l’émetteur et le récepteur. |

| I2C | Lignes SCL et SDA. Nécessite des résistances de tirage vers le haut. SDA doit être stable pendant que SCL est à haut. | Problèmes de maintien du bus ou de prolongation d’horloge entraînant des timeouts. |

| SPI | Les lignes d’horloge et de données sont séparées. Déclenchement sur front (paramètres CPOL/CPHA). | Les esclaves répondant trop lentement par rapport à la vitesse d’horloge du maître. |

| Interruptions GPIO | Sensibilité au front. Nécessite un temps de traitement minimal dans le gestionnaire d’interruption. | Interruptions manquées dues à une exécution longue des routines de service précédentes. |

Par exemple, dans SPI, le moment du front d’horloge par rapport à la ligne de données détermine si les données sont capturées sur le front montant ou descendant. Si le microprogramme suppose un mode et que le matériel est configuré pour l’autre, les données seront lues incorrectement. Un diagramme temporel clarifie cette relation visuellement, évitant ainsi les erreurs de configuration.

🔍 Débogage des problèmes liés au temps

Lorsqu’un système se comporte de manière erratique, l’outil à utiliser en premier n’est pas un débogueur, mais un diagramme temporel. Le débogage avec le temps consiste à capturer le comportement électrique réel et à le comparer au design attendu.

Les problèmes courants liés au temps incluent :

- Métastabilité :Lorsqu’un signal arrive à une bascule trop près du front d’horloge, la sortie devient imprévisible. Elle peut se stabiliser à haut, bas, ou rester dans un état intermédiaire pendant un temps indéterminé.

- Conditions de course : Lorsque le résultat dépend du timing relatif des événements. Si deux signaux changent simultanément, l’ordre de traitement importe.

- Intégrité du signal : Les réflexions et les bourdonnements sur les traces longues peuvent provoquer des transitions erronées. Le diagramme peut montrer des oscillations là où une onde carrée propre devrait se trouver.

- Violations de setup/hold : Les données changent trop près de l’edge d’horloge. Cela est souvent dû à une vitesse d’horloge trop élevée par rapport au chemin logique.

Pour résoudre ces problèmes, vous devrez peut-être ajouter des délais dans le code, modifier la fréquence d’horloge ou ajuster la disposition matérielle. Le diagramme de timing fournit les preuves nécessaires pour apporter ces modifications en toute confiance.

📝 Meilleures pratiques pour la documentation

Créer des diagrammes de timing pour la documentation est aussi important que de les lire. Un timing mal documenté conduit à des cauchemars de maintenance. Les ingénieurs futurs auront du mal à comprendre pourquoi un délai spécifique a été ajouté au code.

Suivez ces directives lors de la création de vos propres diagrammes :

- Utilisez des symboles standards :Évitez les icônes personnalisées sauf si elles sont définies dans une légende. Utilisez la notation standard pour les fronts montants/descendants.

- Tout étiqueter :Ne supposez pas que le lecteur connaît la signification de chaque ligne. Étiquetez clairement les broches, les signaux et les états.

- Inclure le contexte :Montrez l’état des signaux de contrôle (comme Chip Select ou Enable) aux côtés des lignes de données.

- Précisez les unités :Indiquez toujours l’échelle de temps. S’agit-il de microsecondes, de nanosecondes ou de cycles d’horloge ?

- Mettre en évidence les chemins critiques :Utilisez des lignes en gras ou des couleurs différentes pour mettre en évidence les signaux qui déterminent la stabilité du système.

- Contrôle de version :Mettez à jour les diagrammes lorsque le matériel ou le firmware change. Un diagramme obsolète est une menace.

La documentation ne doit pas montrer uniquement le « chemin heureux ». Elle doit également montrer les états d’erreur. À quoi ressemble le diagramme lorsqu’un délai d’attente expiré se produit ? À quoi ressemble-t-il lorsqu’un redémarrage est déclenché ? Ce sont souvent dans ces scénarios que les bogues les plus insidieux se cachent.

🌡️ Facteurs environnementaux

Un diagramme de timing est souvent généré dans des conditions de laboratoire idéales. Les environnements réels sont rarement idéaux. La température, la tension et les interférences électromagnétiques affectent toutes la propagation du signal.

Prenez en compte les facteurs suivants :

- Température :Les performances du silicium se dégradent à haute température. Le délai de propagation augmente. Un système qui fonctionne à 25 °C pourrait échouer à 85 °C.

- Tension :Une tension d’alimentation plus faible augmente le délai. Une tension plus élevée pourrait réduire le délai, mais augmente la consommation d’énergie et la chaleur.

- Capacité de charge : Les longs fils ajoutent de la capacité. Cela ralentit les temps de montée et de descente des signaux, ce qui élargit effectivement la largeur d’impulsion tout en ralentissant la transition.

Une conception robuste prend en compte ces variations. Lors de la création d’un diagramme de temporisation pour la production, envisagez le coin « pire cas ». Cela signifie que le diagramme représente les transitions de signal les plus lentes possibles et les fronts d’horloge les plus rapides possibles. Si le système fonctionne dans ces conditions, il fonctionnera dans la plupart des cas.

🛠️ Création et validation des diagrammes

Bien qu’un dessin manuel soit possible, l’ingénierie moderne repose sur des outils automatisés pour capturer et valider les temporisations. Toutefois, les principes restent les mêmes, quel que soit l’outil utilisé. L’objectif est de visualiser l’écoulement du temps.

Lors de la validation d’un diagramme :

- Comparer avec les fiches techniques : Assurez-vous que les valeurs de temporisation de votre diagramme correspondent aux spécifications du fabricant pour les puces utilisées.

- Exécuter des simulations : Utilisez des environnements de simulation pour modéliser la logique avant de construire le circuit physique.

- Mesurer le matériel réel : Rien ne remplace la mesure réelle. Capturez les formes d’onde à partir de la carte physique et superposez-les sur le diagramme de conception.

- Vérifier les marges : Y a-t-il assez de temps de marge entre les signaux ? Si la marge est nulle, toute variation entraînera une défaillance.

La validation est un processus continu. Au fur et à mesure que le micrologiciel évolue, les exigences de temporisation peuvent changer. Un nouveau gestionnaire d’interruption pourrait introduire un retard qui pousse un signal au-delà de son délai. Une vérification continue assure que le pont entre le code et le matériel reste solide.

🔗 L’intersection de la logique et de la physique

En définitive, un diagramme de temporisation représente l’intersection de la logique et de la physique. La logique dicte ce qui devrait se produire ; la physique dicte ce qui se produit réellement. Le rôle de l’ingénieur est d’aligner ces deux réalités.

En maîtrisant l’interprétation et la création de ces diagrammes, vous acquérez la capacité de diagnostiquer des défaillances complexes que d’autres pourraient manquer. Vous cessez de deviner pourquoi le système bloque et commencez à voir exactement là où la contrainte de temporisation a été violée. Ce niveau de compréhension transforme un développeur en concepteur.

Que vous conceviez une interface de capteur simple ou un bus de communication à haute vitesse, le diagramme de temporisation est votre référence principale. Il garantit que le code que vous écrivez s’exécute dans le délai attendu par le matériel. Il garantit que les signaux que vous voyez à l’écran correspondent aux tensions sur les broches. C’est le langage de la synchronisation.

Consacrez du temps à comprendre ces diagrammes. Traitez-les avec la même gravité que le code lui-même. Dans les systèmes embarqués, le temporisation n’est pas seulement un détail ; c’est la fondation de la fiabilité. Lorsque le code et le matériel parlent la même langue du temps, le système fonctionne avec précision et stabilité.