Diagram waktu adalah tulang punggung desain sistem digital. Mereka menyediakan bahasa visual yang digunakan insinyur untuk menjelaskan bagaimana sinyal berubah seiring waktu. Baik Anda sedang merancang antarmuka mikrokontroler atau mendiagnosis protokol komunikasi, memahami diagram ini sangat penting. Panduan ini membimbing Anda melalui proses membuat dan menafsirkan diagram tersebut tanpa kompleksitas yang tidak perlu.

Memulai mungkin terasa menakutkan, tetapi dengan kerangka kerja yang tepat, Anda dapat menggambar diagram yang efektif dengan cepat. Kami akan membahas komponen utama, logika di balik transisi sinyal, serta parameter penting yang menentukan keandalan sistem. Mari kita masuk ke mekanisme waktu sinyal.

Memahami Tujuan Utama 🧠

Diagram waktu adalah representasi grafis dari urutan kejadian dalam suatu sistem. Diagram ini memetakan keadaan sinyal terhadap sumbu waktu bersama. Berbeda dengan diagram skematik yang menunjukkan koneksi fisik, diagram waktu berfokus pada hubungan temporal. Perbedaan ini sangat penting untuk mendiagnosis kesalahan logika yang tidak muncul dalam analisis rangkaian statis.

Ketika Anda menggambar diagram ini, Anda sedang mendokumentasikan perilaku sinyal data dan kontrol. Tujuannya adalah memastikan bahwa satu sinyal siap sebelum sinyal lainnya bertindak atasnya. Sinkronisasi ini mencegah kerusakan data dan memastikan operasi yang stabil.

-

Kesadaran Visual: Mereka menjadikan ketergantungan waktu yang abstrak menjadi nyata.

-

Bantuan Debugging: Mereka menyoroti kondisi persaingan dan pelanggaran setup.

-

Dokumentasi: Mereka berfungsi sebagai referensi bagi tim perangkat keras dan perangkat lunak.

-

Verifikasi: Mereka membantu memvalidasi bahwa logika sesuai dengan spesifikasi.

Tanpa diagram yang jelas, mudah untuk melewatkan masalah waktu yang halus yang hanya muncul dalam kondisi tertentu. Dengan menstandarkan cara Anda menggambar, Anda mengurangi ambiguitas bagi semua pihak yang terlibat dalam proyek ini.

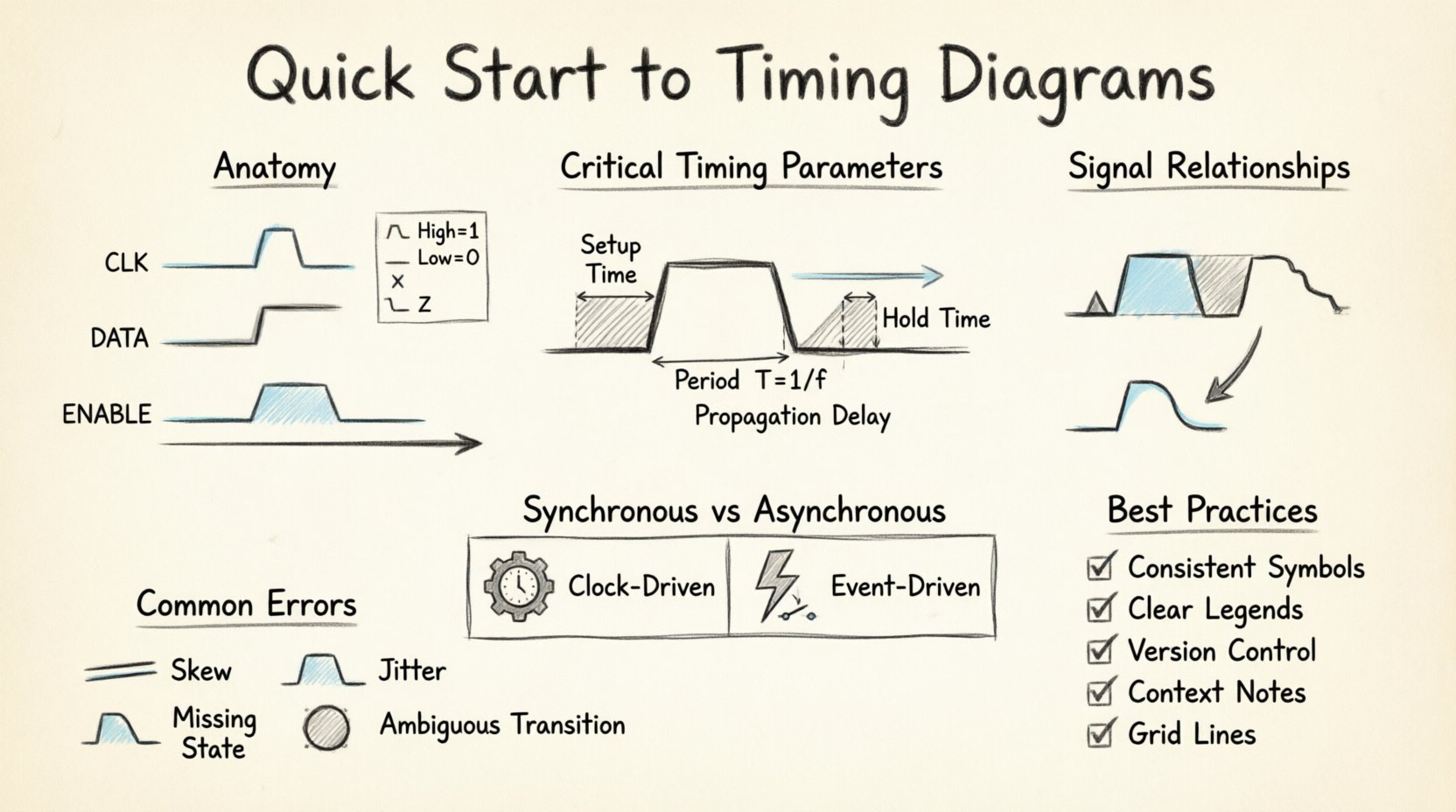

Anatomi Diagram Waktu 📐

Setiap diagram waktu memiliki struktur umum. Menguasai struktur ini memungkinkan Anda membaca gelombang kompleks dengan mudah. Tata letak ini konsisten di berbagai disiplin teknik, mulai dari sistem tertanam hingga jaringan berkecepatan tinggi.

1. Sumbu Waktu ⏰

Sumbu horizontal mewakili waktu. Alirannya dari kiri ke kanan. Waktu tidak selalu linier dalam setiap konteks, tetapi dalam sebagian besar diagram standar, jarak yang sama mewakili interval waktu yang sama. Anda tidak perlu menandai setiap milidetik, tetapi menandai interval penting membantu menyesuaikan informasi.

-

Arah:Selalu dari kiri ke kanan.

-

Skala:Dapat berupa linier atau logaritmik tergantung pada frekuensi sinyal.

-

Penanda:Gunakan garis vertikal untuk menandai kejadian tertentu seperti tepi jam.

2. Garis Sinyal 📊

Sinyal direpresentasikan oleh garis horizontal yang ditumpuk secara vertikal. Setiap garis sesuai dengan kabel atau jaringan tertentu dalam rangkaian. Nama sinyal biasanya muncul di sisi kiri atau kanan garis.

-

Pengelompokan:Sinyal yang saling berkaitan, seperti jalur alamat dan data, sering dikelompokkan bersama.

-

Penandaan:Selalu beri label pada sinyal dengan jelas untuk menghindari kebingungan antara nama-nama yang mirip.

-

Urutan:Tempatkan sinyal yang paling penting di bagian atas atau bawah, tergantung pada konvensi.

3. Tingkat Logika 🔋

Sinyal berpindah-pindah antara status yang telah ditentukan. Dalam logika digital, ini biasanya tinggi dan rendah, atau 1 dan 0. Posisi vertikal garis menunjukkan statusnya.

|

Status |

Notasi Umum |

Makna Fisik |

|---|---|---|

|

Tinggi |

1, H, VCC |

Relai tegangan positif |

|

Rendah |

0, L, GND |

Tanah atau tegangan nol |

|

Tidak diketahui |

X |

Status yang tidak pasti |

|

Impedansi Tinggi |

Z |

Terputus atau mengambang |

Memahami tingkat-tingkat ini adalah langkah pertama dalam membaca diagram. Transisi antara tingkat-tingkat ini adalah tempat terjadinya aktivitas.

Parameter Waktu Kritis ⚙️

Waktu bukan hanya tentang menggambar garis; ini tentang menentukan batasan. Parameter tertentu menentukan seberapa cepat suatu sinyal dapat berubah dan kapan sinyal harus stabil. Batasan-batasan ini sangat penting untuk memastikan sistem berfungsi dengan benar.

1. Waktu Persiapan ⏳

Waktu persiapan adalah jumlah waktu minimum yang harus stabil oleh sinyal data sebelum tepi jam tiba. Jika data berubah terlalu dekat dengan tepi jam, sistem dapat menangkap nilai yang salah. Ini merupakan batasan kritis dalam sistem sinkron.

-

Definisi:Waktu sebelum tepi jam aktif.

-

Pelanggaran:Menyebabkan metastabilitas atau penangkapan data yang salah.

-

Aturan Desain: Pastikan data stabil jauh sebelum jam berfungsi.

2. Waktu Tahan ⏳

Waktu tahan adalah jumlah waktu minimum yang harus tetap stabil dari sinyal data setelah tepi jam. Jika sinyal berubah terlalu cepat setelah pemicu, elemen penerima mungkin tidak menangkap nilai dengan benar.

-

Definisi:Waktu setelah tepi jam aktif.

-

Pelanggaran: Mirip dengan waktu pengaturan, menyebabkan kesalahan data.

-

Aturan Desain:Pastikan sinyal tidak berubah segera setelah jam.

3. Keterlambatan Propagasi ⏱️

Keterlambatan propagasi adalah waktu yang dibutuhkan sinyal untuk menempuh perjalanan dari input komponen ke outputnya. Tidak ada komponen elektronik yang berfungsi secara instan. Keterlambatan ini menumpuk di berbagai tahap dan harus diperhitungkan dalam desain berkecepatan tinggi.

-

Sumber:Keterlambatan gerbang internal dan panjang kabel.

-

Dampak:Membatasi frekuensi operasi maksimum.

-

Pengukuran:Diukur dari titik 50% input ke titik 50% output.

4. Periode dan Frekuensi 🔁

Untuk sinyal jam, periode adalah waktu antara dua titik identik berurutan pada gelombang (misalnya, tepi naik ke tepi naik). Frekuensi adalah kebalikan dari periode.

-

Periode: T = 1 / f

-

Duty Cycle:Persentase waktu sinyal berada dalam keadaan tinggi dalam satu periode.

-

Stabilitas:Jitter jam memengaruhi presisi waktu.

Membaca dan Menganalisis Hubungan Sinyal 🔄

Setelah Anda memahami komponen-komponennya, langkah berikutnya adalah menganalisis bagaimana sinyal saling berinteraksi. Di sinilah diagram menjadi alat diagnostik. Anda mencari ketergantungan dan konflik potensial.

1. Pemicu Tepi 📉

Kebanyakan rangkaian digital dipicu oleh tepi tertentu dari jam. Beberapa dipicu oleh tepi naik, sementara yang lain menggunakan tepi turun. Anda harus mengidentifikasi tepi mana yang aktif untuk setiap komponen dalam sistem Anda.

-

Tepi Naik:Transisi dari Rendah ke Tinggi.

-

Sisi Turun:Transisi dari Tinggi ke Rendah.

-

Kedua Sisi:Beberapa sistem mengambil sampel data pada kedua transisi.

Saat menggambar, gunakan segitiga kecil atau takik untuk menunjukkan sisi mana yang aktif. Ini mencegah kebingungan selama implementasi.

2. Jendela Data yang Valid 🕒

Data hanya valid dalam jendela tertentu. Sebelum waktu setup, dan setelah waktu hold, garis data tidak boleh berubah. Di luar jendela ini, data dianggap valid. Menandai jendela ini pada diagram Anda akan menjelaskan ekspektasi.

-

Jendela:Didefinisikan oleh Setup + Hold + Keterlambatan Propagasi.

-

Pelanggaran:Jika data berubah di luar jendela ini, terjadi kesalahan.

-

Petunjuk Visual:Gunakan area yang diarsir untuk menyoroti periode data yang valid.

3. Sinyal Asinkron 📡

Tidak semua sinyal mengikuti jam. Sinyal asinkron seperti interupsi atau reset beroperasi secara independen. Mereka memerlukan penanganan hati-hati dalam diagram waktu untuk menunjukkan prioritas dan latensi mereka.

-

Prioritas:Interupsi sering kali mendahului siklus jam.

-

Latensi:Catat keterlambatan antara penegasan dan respons.

-

Stabilitas:Pastikan sinyal asinkron stabil sesuai persyaratan setup/hold.

Sistem Sinkron vs Asinkron 📡

Perbedaan antara desain sinkron dan asinkron memengaruhi cara Anda membuat diagram Anda. Setiap pendekatan memiliki aturan dan konvensi khusus.

|

Fitur |

Sinkron |

Asinkron |

|---|---|---|

|

Kontrol |

Dikendalikan oleh jam |

Dikendalikan oleh peristiwa |

|

Prediksi |

Waktu yang mudah diprediksi |

Waktu yang lebih sulit diprediksi |

|

Kompleksitas |

Logika yang distandarkan |

Protokol handshake |

|

Daya |

Lebih tinggi karena clock |

Sering lebih rendah |

Pada diagram sinkron, Anda akan melihat jalur clock dominan yang menyelaraskan semua sinyal lain. Pada diagram asinkron, Anda akan melihat handshake dan status tunggu. Keduanya membutuhkan dokumentasi waktu yang tepat.

Kesalahan Umum dan Cara Menghindarinya ⚠️

Kesalahan dalam diagram waktu dapat menyebabkan revisi perangkat keras yang mahal. Mengetahui jebakan umum membantu Anda membuat representasi yang lebih bersih dan akurat.

1. Mengabaikan Skew 📏

Skew adalah perbedaan waktu kedatangan sinyal di titik-titik yang berbeda. Jika Anda mengasumsikan semua sinyal tiba secara bersamaan, Anda mungkin melewatkan pelanggaran waktu. Selalu pertimbangkan perbedaan panjang kabel dan beban.

-

Periksa: Bandingkan waktu kedatangan di penerima yang berbeda.

-

Perbaiki: Tambahkan buffer penundaan atau sesuaikan panjang jalur.

-

Visual: Tunjukkan sedikit pergeseran pada garis-garis sejajar jika skew signifikan.

2. Mengabaikan Jitter ⚡

Jitter adalah variasi dalam waktu sinyal. Clock mungkin tidak sepenuhnya periodik. Pada desain berkecepatan tinggi, jitter dapat mengurangi margin waktu Anda. Gambarkan jitter sebagai area berbayang di sekitar tepi clock.

-

Sumber: Gangguan catu daya atau gangguan eksternal.

-

Dampak: Mengurangi waktu setup dan hold yang efektif.

-

Visual: Gunakan garis kabur atau pita untuk menunjukkan ketidakpastian.

3. Transisi yang Ambigu 🔄

Transisi yang tampak seperti garis lurus sebenarnya bisa berupa kemiringan. Sinyal nyata tidak berubah secara instan. Menggambar garis vertikal sempurna menyiratkan kecepatan tak terhingga, yang secara fisik tidak mungkin.

-

Praktik Terbaik:Gambar transisi dengan kemiringan sedikit jika presisi diperlukan.

-

Kebiasaan:Garis vertikal diperbolehkan untuk representasi logis.

-

Kejelasan:Pastikan maksudnya jelas terlepas dari kemiringan.

4. Transisi Status yang Hilang 🚦

Mesin status yang kompleks sering memiliki status antara yang tidak jelas. Jika Anda hanya menggambar status awal dan akhir, Anda akan kehilangan informasi penting mengenai urutan.

-

Detail:Tampilkan semua perubahan status yang relevan.

-

Label:Berikan keterangan pada status dengan nama atau nilai mereka.

-

Logika:Pastikan diagram mencerminkan alur logika yang sebenarnya.

Praktik Terbaik untuk Dokumentasi 📝

Untuk memastikan diagram Anda bermanfaat selama bertahun-tahun, ikuti gaya yang konsisten. Ini membuatnya lebih mudah dipelihara dan dibagikan dengan insinyur lain.

-

Simbol yang Konsisten:Gunakan panah dan gaya garis yang sama di seluruh diagram.

-

Legenda yang Jelas:Tentukan simbol atau singkatan khusus yang digunakan.

-

Kontrol Versi:Beri label diagram dengan nomor versi dan tanggal.

-

Konteks:Sertakan deskripsi singkat mengenai sistem yang digambarkan.

-

Garis Kisi:Gunakan kisi untuk membantu menyelaraskan sinyal dan menandai interval waktu.

Konsistensi mengurangi beban kognitif bagi siapa pun yang membaca pekerjaan Anda. Ini juga membuat lebih mudah untuk mengidentifikasi anomali saat Anda meninjau diagram nanti.

Mendiagnosis Masalah dengan Analisis Waktu 🛠️

Ketika suatu sistem gagal, diagram waktu sering menjadi tempat pertama yang diperiksa. Mereka membantu mengidentifikasi apakah masalahnya bersifat logis atau temporal.

1. Mengidentifikasi Kondisi Persaingan 🏁

Kondisi persaingan terjadi ketika output tergantung pada urutan kejadian. Jika dua sinyal tiba di gerbang pada waktu yang sama, hasilnya bisa tidak dapat diprediksi. Diagram waktu mengungkap tumpang tindih ini.

-

Perhatikan: Sinyal yang saling melintas secara bersamaan.

-

Solusi: Tambahkan buffer atau ubah urutan logika.

-

Pencegahan: Rancang dengan margin untuk menghindari transisi bersamaan.

2. Mendeteksi Glitch ⚡

Glitch adalah pulsa pendek yang terjadi karena keterlambatan propagasi. Mereka bisa memicu flip-flop secara tidak sengaja. Pada diagram, mereka muncul sebagai puncak sempit di antara level yang stabil.

-

Visual: Pulsa sempit yang tidak sesuai dengan periode clock.

-

Perbaikan: Gunakan penyaringan atau kunci sinyal pada tepi yang stabil.

-

Analisis: Periksa apakah lebar pulsa melebihi waktu hold.

3. Memverifikasi Protokol Bus 📡

Bus seperti I2C atau SPI memiliki persyaratan waktu yang ketat. Kondisi mulai dan berhenti, penjuluran clock, serta pergeseran data harus sejalan sempurna. Diagram waktu adalah cara standar untuk memverifikasi protokol ini.

-

Mulai/Berhenti: Verifikasi transisi yang benar pada jalur data relatif terhadap clock.

-

Penjuluran: Pastikan slave dapat menahan clock rendah selama durasi yang dibutuhkan.

-

Data: Konfirmasi data stabil selama fase clock tinggi.

Pikiran Akhir Mengenai Integritas Sinyal 🎯

Membuat diagram waktu yang akurat adalah keterampilan yang membaik dengan latihan. Ini membutuhkan pemahaman mendalam tentang bagaimana elektronik berperilaku seiring waktu. Dengan mengikuti panduan di atas, Anda dapat membuat diagram yang informatif dan dapat diandalkan.

Ingat bahwa diagram ini adalah alat komunikasi. Mereka menghubungkan kesenjangan antara teori dan implementasi. Saat Anda menggambar diagram waktu, Anda sedang menceritakan kisah tentang bagaimana sistem berperilaku. Jadikan kisah itu jelas, tepat, dan konsisten.

Fokus pada parameter penting: setup, hold, delay, dan skew. Pertahankan tata letak yang bersih dan label yang tidak ambigu. Dengan kebiasaan ini, Anda akan menemukan bahwa menggambar diagram waktu menjadi bagian alami dari proses desain Anda, memungkinkan Anda menyelesaikannya dalam hitungan menit, bukan jam.