Diagram waktu adalah tulang punggung verifikasi sistem digital. Mereka menerjemahkan logika abstrak menjadi timeline visual yang menjadi acuan bagi insinyur, desainer, dan pengujicoba untuk memvalidasi perilaku sinyal. Ketika diagram waktu mengandung kesalahan, konsekuensinya melampaui meja gambar. Asumsi waktu yang salah dapat menyebabkan kegagalan perangkat keras, kerusakan data, atau ketidakstabilan sistem di lingkungan produksi. Panduan ini mengeksplorasi kesalahan paling umum dalam analisis waktu dan memberikan strategi konkret untuk memastikan akurasi.

Membuat diagram waktu yang akurat membutuhkan lebih dari sekadar menggambar garis. Ini menuntut pemahaman mendalam tentang domain jam, propagasi sinyal, dan keterbatasan fisik. Insinyur sering terburu-buru dalam tahap visualisasi, mengabaikan detail halus yang menjadi krusial saat implementasi. Dengan mengenali kesalahan umum ini sejak dini, tim dapat menghemat waktu signifikan selama tahap debugging dan integrasi. Mari kita teliti area-area spesifik di mana kesalahan biasanya terjadi.

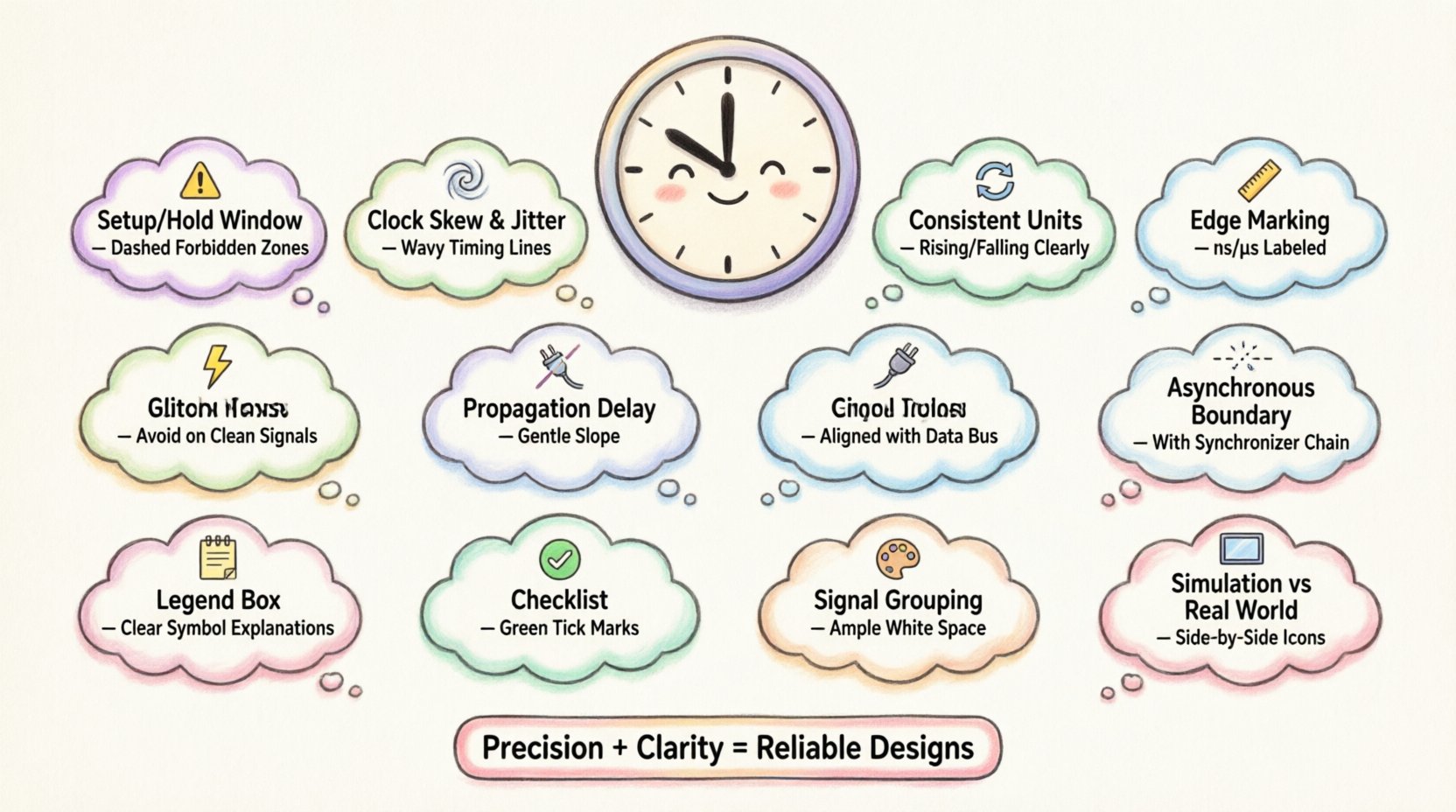

1. Salah Memahami Pelanggaran Waktu Setup dan Hold ⚠️

Waktu setup dan hold adalah batasan mendasar dalam desain digital sinkron. Pelanggaran setup terjadi ketika data tiba terlambat sebelum tepi jam aktif. Pelanggaran hold terjadi ketika data berubah terlalu cepat setelah tepi jam. Ini bukan hanya konsep teoretis; mereka mewakili batas fisik flip-flop dan gerbang logika.

Banyak diagram gagal menunjukkan secara jelas jendela validitas untuk sinyal data. Saat menggambar sinyal-sinyal ini, insinyur terkadang mengabaikan jendela setup dan hold yang krusial, menyebabkan ambiguitas saat ditinjau. Diagram yang kuat harus secara eksplisit menandai jendela-jendela ini relatif terhadap tepi jam.

- Kesalahan Umum:Menggambar transisi data yang tepat berimpit dengan tepi jam tanpa mempertimbangkan jitter atau skew.

- Kesalahan Umum:Mengabaikan arah tepi (naik vs turun) untuk jendela setup/hold.

- Kesalahan Umum:Mengasumsikan tepi jam ideal dengan waktu transisi nol.

Untuk menghindari masalah ini, selalu beri keterangan pada margin setup dan hold. Gunakan pewarnaan atau tanda khusus untuk menunjukkan zona terlarang di mana transisi data tidak valid. Petunjuk visual ini memaksa peninjau untuk memeriksa apakah jalur sinyal sesuai dengan persyaratan waktu logika penerima.

2. Mengabaikan Skew dan Jitter Jam 🌪️

Skew jam mengacu pada perbedaan waktu kedatangan sinyal jam di komponen yang berbeda. Jitter mewakili variasi jangka pendek dalam waktu sinyal jam. Kedua faktor ini dapat secara drastis mengubah jendela waktu efektif untuk sinyal data.

Kesalahan umum dalam diagram adalah memperlakukan jam sebagai garis vertikal yang sempurna di seluruh komponen. Pada kenyataannya, jaringan distribusi menyebabkan keterlambatan. Jika diagram menunjukkan satu jalur jam yang bercabang ke tiga register berbeda tanpa mempertimbangkan perbedaan jalur, maka gambaran ini tidak realistis mengenai perilaku sistem.

- Dampak:Skew dapat mengurangi waktu yang tersedia bagi data untuk merambat, menyebabkan pelanggaran setup yang salah.

- Dampak:Jitter dapat menyempitkan margin waktu hold, meningkatkan risiko metastabilitas.

Saat membuat diagram, gambarkan jalur jam sebagai garis terpisah dengan offset relatif jika skew signifikan. Jika skew dapat diabaikan, nyatakan asumsi ini secara jelas dalam catatan diagram. Jangan menyembunyikan kompleksitas distribusi jam jika memengaruhi anggaran waktu.

3. Skala dan Satuan Waktu yang Tidak Konsisten 📏

Salah satu kesalahan paling sederhana namun paling merusak adalah mencampur skala waktu dalam satu diagram. Bagian tertentu mungkin menunjukkan nanosekon sementara bagian lain menunjukkan mikrosekon. Ketidakkonsistenan ini memaksa pembaca terus-menerus menghitung ulang rasio, meningkatkan kemungkinan salah paham.

Masalah lain adalah kurangnya sumbu waktu yang jelas. Tanpa batang skala atau tanda skala yang diberi label, durasi pulsa menjadi subjektif. Pulsa pendek bisa berarti 10 nanosekon atau 100 nanosekon tergantung bagaimana pembaca memahami jaraknya.

Ikuti standar berikut untuk menjaga konsistensi:

- Tentukan Skala:Tempatkan penggaris waktu di bagian bawah atau atas diagram.

- Gunakan Notasi Ilmiah:Beri label satuan secara jelas (ns, μs, ps) di bagian header.

- Jaga Rasio yang Proporsional: Pastikan jarak horizontal antar kejadian sesuai dengan selisih waktu.

Konsistensi membangun kepercayaan. Ketika setiap insinyur melihat diagram ini, mereka harus mendapatkan nilai waktu yang sama tanpa perlu membuat asumsi tentang skala gambar.

4. Ambiguitas dalam Pemicu Tepi 🔄

Logika digital sering mengandalkan pemicu tepi tertentu, seperti tepi naik atau tepi turun. Diagram waktu harus secara eksplisit menunjukkan tepi mana yang memicu tindakan. Ambiguitas di sini dapat menyebabkan perilaku yang sama sekali berlawanan pada perangkat keras.

Kesalahan umum adalah menggambar sinyal clock tanpa menunjukkan tepi aktif. Misalnya, jika flip-flop dipicu oleh tepi turun tetapi diagram terlihat identik dengan pemicu tepi naik, desainer logika mungkin mengimplementasikan perilaku yang salah.

- Praktik Terbaik:Gunakan panah pada garis clock untuk menunjukkan tepi aktif.

- Praktik Terbaik:Berikan label jenis pemicu pada legenda (misalnya, “Posedge”, “Nedge”).

- Praktik Terbaik:Hindari menggunakan panah ganda kecuali kedua tepi aktif.

Kejelasan sangat penting. Jika suatu sinyal asinkron, pastikan sinyal tersebut dipisahkan secara jelas dari domain clock untuk menghindari kebingungan mengenai tepi mana yang mengendalikannya.

5. Mengabaikan Penundaan Propagasi ⏳

Penundaan propagasi adalah waktu yang dibutuhkan sinyal untuk bergerak dari input ke output melalui gerbang logika atau kabel. Pada diagram ideal, sinyal tampak berubah secara instan. Pada sistem fisik, selalu ada penundaan.

Ketika desainer mengabaikan penundaan propagasi, diagram waktu menyiratkan bahwa output berubah segera setelah input berubah. Hal ini dapat menyembunyikan pelanggaran waktu yang akan terjadi pada silicon. Misalnya, jalur kombinasional mungkin tampak memenuhi periode clock pada diagram, tetapi penundaan aktual mendorong data melewati tepi clock berikutnya.

| Fitur | Diagram Ideal | Implementasi Dunia Nyata |

|---|---|---|

| Transisi Sinyal | Garis Vertikal | Garis Miring dengan Penundaan |

| Propagasi | Instan | Penundaan Gerbang + Penundaan Kabel |

| Margin Setup | Sering Tidak Diperiksa | Harus Memperhitungkan Kasus Terburuk |

Untuk mengurangi dampak ini, beri keterangan penundaan yang diharapkan pada jalur kritis. Jika penundaan signifikan dibandingkan dengan periode clock, gambar transisi dengan kemiringan atau secara eksplisit tandai nilai penundaannya. Representasi visual ini membantu pemeriksa untuk mengidentifikasi kemungkinan hambatan sebelum fabrikasi.

6. Mengabaikan Risiko Metastabilitas 🌌

Metastabilitas terjadi ketika flip-flop menerima data di dekat tepi clock, menyebabkan flip-flop memasuki keadaan tak terdefinisi selama durasi yang tidak dapat diprediksi. Diagram waktu jarang menangkap keadaan ini secara eksplisit karena ini merupakan mode kegagalan, bukan operasi normal.

Namun, mengabaikan kemungkinan metastabilitas dalam antarmuka asinkron adalah kelalaian kritis. Jika sebuah diagram menunjukkan sinyal asinkron yang disinkronkan ke clock tanpa rantai sinkronisasi, hal ini mengimplikasikan risiko kehilangan data atau kerusakan data.

- Identifikasi:Perhatikan sinyal yang melintasi domain clock tanpa sinkronisasi yang tepat.

- Dokumentasi:Catat di mana metastabilitas merupakan risiko yang diketahui dan bagaimana risiko tersebut dikurangi.

- Visualisasi:Gunakan garis putus-putus untuk menunjukkan batas asinkron.

Bahkan jika sistem dirancang untuk menangani metastabilitas, diagram harus mencerminkan tahapan sinkronisasi. Ini memastikan bahwa tim verifikasi mengetahui untuk menguji kondisi-kondisi khusus ini.

7. Glitch Sinyal dan Bahaya ⚡

Glitch adalah pulsa sementara yang terjadi karena keterlambatan penyebaran yang tidak sama pada jalur paralel. Mereka dapat menyebabkan pemantik logika yang salah jika tidak dipertimbangkan dalam analisis waktu.

Kesalahan umum adalah menggambar sinyal yang bersih dan stabil di tempat yang secara fisik tidak terhindarkan adanya glitch. Misalnya, pada multiplexer yang beralih antar input, output mungkin berkedip sebentar sebelum stabil. Jika diagram menunjukkan transisi yang halus, logika di hilir mungkin tidak dirancang untuk menyaring glitch ini.

Soroti zona bahaya potensial dalam diagram. Gunakan anotasi untuk memperingatkan bahwa sinyal tertentu mungkin menunjukkan perilaku sementara selama perubahan keadaan. Ini memberi informasi strategi pengujian untuk menyertakan skenario deteksi glitch.

8. Kurangnya Konteks untuk Sinyal Kontrol 🔌

Sinyal data tidak berguna tanpa konteks dari sinyal kontrol seperti enable, reset, atau chip select. Diagram yang hanya fokus pada jalur data sering kali melewatkan kondisi yang diperlukan agar data tersebut valid.

Misalnya, bus data mungkin menunjukkan nilai yang valid, tetapi jika sinyal ‘Write Enable’ tidak ditampilkan aktif selama jendela tersebut, data tersebut secara efektif diabaikan. Sebaliknya, jika ‘Write Enable’ aktif tetapi data tidak valid, sistem akan menulis data yang tidak berguna.

- Sertakan Kontrol:Selalu tampilkan sinyal kontrol bersamaan dengan sinyal data.

- Tentukan Validitas:Gunakan bendera ‘Valid’ atau indikator serupa untuk menunjukkan kapan data dapat dipercaya.

- Kondisi Status:Tandai secara jelas keadaan sinyal kontrol (Aktif Tinggi vs. Aktif Rendah).

Kelengkapan adalah kunci. Diagram waktu yang tidak memiliki konteks sinyal kontrol sering menjadi sumber kebingungan saat debugging. Pastikan hubungan antara kontrol dan data secara visual terlihat jelas.

9. Penggunaan Anotasi dan Legenda yang Buruk 📝

Bahkan diagram yang akurat sempurna bisa disalahpahami jika tidak memiliki anotasi yang tepat. Simbol, singkatan, dan legenda harus konsisten dan dijelaskan.

Kesalahan anotasi umum meliputi:

- Menggunakan label umum seperti ‘Sinyal A’ alih-alih nama yang deskriptif.

- Gagal menjelaskan makna gaya garis tertentu (padat vs. putus-putus).

- Mengabaikan definisi tingkat aktif (Aktif Tinggi vs. Aktif Rendah).

Bagian legenda khusus harus menjadi bagian dari setiap diagram waktu. Ini mendefinisikan setiap simbol, gaya garis, dan singkatan yang digunakan. Ini mengurangi beban kognitif bagi pembaca dan memastikan semua orang memahami diagram dengan cara yang sama.

10. Daftar Periksa Verifikasi dan Tinjauan ✅

Sebelum menyelesaikan diagram waktu, diperlukan tinjauan sistematis. Gunakan daftar periksa berikut untuk memvalidasi akurasi dan kejelasan pekerjaan Anda.

| Item Pemeriksaan | Kriteria Kelulusan |

|---|---|

| Skala Waktu | Satuan yang konsisten dan penggaris yang jelas disediakan |

| Sudut Jam | Sudut aktif dengan jelas ditandai untuk semua jam |

| Setup/Waktu Tahan | Jendela didefinisikan untuk sinyal sinkron |

| Propagasi | Keterlambatan diperhitungkan pada jalur kritis |

| Sinyal Kendali | Sinyal Enable/Reset ditampilkan bersama data |

| Legenda | Semua simbol dan singkatan dijelaskan |

| Persilangan Domain | Titik CDC diidentifikasi dan ditandai |

Secara rutin memperbarui daftar periksa ini memastikan tidak ada kesalahan umum yang terlewat. Ini berfungsi sebagai gerbang kualitas untuk dokumentasi sebelum mencapai tim rekayasa.

11. Kejelasan Visual dan Desain Tata Letak 🎨

Tata letak diagram waktu memengaruhi seberapa mudah kesalahan terdeteksi. Diagram yang padat dengan sinyal yang tumpang tindih rentan terbaca salah. Penyelarasan vertikal sinyal-sinyal yang terkait membantu mata melacak hubungan antar kejadian.

Ikuti prinsip tata letak berikut:

- Kelompokkan Sinyal:Pertahankan sinyal-sinyal yang terkait (seperti alamat dan data) berdekatan.

- Sejajarkan Sudut:Pastikan sudut jam sejajar secara vertikal di seluruh saluran.

- Berikan Ruang:Berikan ruang putih yang cukup untuk menghindari tumpang tindih sinyal.

- Kode Warna:Gunakan warna berbeda untuk domain jam yang berbeda jika tersedia (meskipun hitam dan putih merupakan standar untuk cetak).

Tata letak yang bersih mengurangi usaha kognitif yang dibutuhkan untuk memahami diagram. Ini membuat lebih mudah mengidentifikasi anomali dan pelanggaran waktu secara langsung.

12. Kendala Dunia Nyata vs. Simulasi 🖥️

Diagram timing yang berasal semata-mata dari simulasi mungkin tidak mencerminkan realitas fisik. Alat simulasi sering mengasumsikan kondisi ideal, seperti kapasitansi parasitik nol dan routing yang sempurna.

Saat menerjemahkan hasil simulasi ke dalam dokumentasi, insinyur harus mempertimbangkan variasi manufaktur. Sudut proses, tegangan, dan suhu (PVT) dapat menggeser margin waktu. Diagram yang hanya menampilkan nilai nominal mungkin tidak cukup untuk desain yang kuat.

- Kasus Terburuk:Pertimbangkan sudut proses terlambat untuk analisis waktu.

- Kasus Tercepat:Pertimbangkan sudut proses tercepat untuk analisis waktu hold.

- Margin:Tambahkan margin keselamatan ke dalam diagram untuk mempertimbangkan variasi PVT.

Dokumentasi harus mencerminkan ketahanan desain, bukan hanya hasil simulasi dalam kondisi terbaik. Ini mempersiapkan tim untuk skenario penempatan di dunia nyata.

Pikiran Akhir Mengenai Akurasi Waktu 🛡️

Diagram waktu adalah alat komunikasi sebanyak alat spesifikasi teknis. Tujuan utamanya adalah menyampaikan niat dan batasan secara jelas kepada semua pemangku kepentingan. Dengan menghindari kesalahan umum seperti mengabaikan skew, mengabaikan sinyal tepi, atau menghilangkan sinyal kontrol, insinyur memastikan bahwa niat desain tetap terjaga dari dokumentasi hingga perangkat keras.

Akurasi dalam diagram ini mencegah pengulangan mahal dan siklus debugging. Diagram yang terstruktur dengan baik berfungsi sebagai satu-satunya sumber kebenaran sepanjang siklus hidup proyek. Luangkan waktu untuk melakukan analisis waktu dengan benar, dan implementasi selanjutnya akan berjalan lancar.

Ingatlah bahwa diagram waktu adalah dokumen yang hidup. Harus diperbarui setiap kali desain berubah. Menjaga integritas informasi waktu memastikan sistem tetap dapat diandalkan sepanjang masa operasionalnya. Fokus pada presisi, kejelasan, dan kelengkapan untuk menghasilkan desain digital yang kuat.