Dalam arsitektur kompleks sistem digital, memahami momen tepat saat suatu sinyal berubah keadaan sangat penting. Diagram waktu menyediakan representasi visual tentang bagaimana sinyal berubah seiring waktu. Mereka merupakan alat penting bagi insinyur, pengembang, dan desainer yang perlu memverifikasi bahwa komponen berinteraksi dengan benar. Tanpa bantuan visual ini, melakukan debugging komunikasi asinkron atau memverifikasi domain jam menjadi seperti menebak-nebak. Panduan ini mengeksplorasi mekanisme, manfaat, dan aplikasi diagram waktu dalam desain sistem.

Apa itu Diagram Waktu? ⚙️

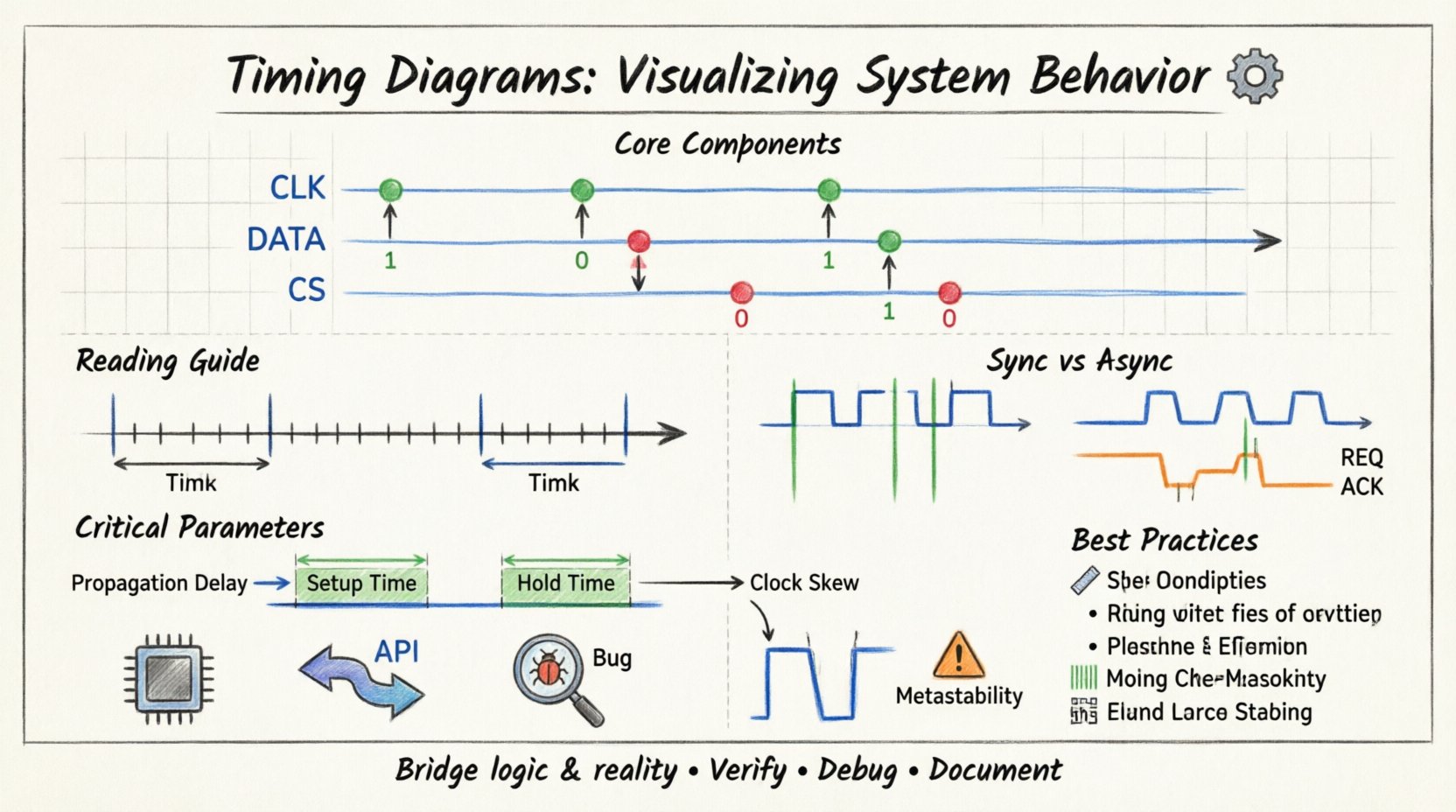

Diagram waktu adalah grafik yang menampilkan perilaku sinyal selama periode tertentu. Diagram ini memetakan keadaan logis sinyal terhadap garis waktu. Berbeda dengan skema sirkuit yang menunjukkan koneksi fisik, diagram waktu berfokus pada hubungan temporal antar kejadian. Diagram ini menjawab pertanyaan seperti: Apakah sinyal A berubah sebelum sinyal B? Apakah pulsa jam cukup lebar? Berapa lama data membutuhkan waktu untuk stabil?

Diagram ini sangat mendasar dalam:

- Memverifikasi protokol perangkat keras

- Mendokumentasikan interaksi logika perangkat lunak

- Membantu debugging kondisi persaingan

- Memvalidasi keselarasan jam dan data

Komponen Utama Diagram Waktu 🧩

Untuk memahami diagram waktu secara efektif, seseorang harus memahami komponen pembentuknya. Setiap diagram terdiri dari elemen-elemen khusus yang menyampaikan informasi mengenai operasi sistem.

1. Sumbu Waktu 📏

Sumbu horizontal mewakili waktu. Biasanya mengalir dari kiri ke kanan. Skala dapat bersifat absolut (nanosekon, mikrosekon) atau relatif (siklus jam). Dalam sistem sinkron, waktu sering dibagi menjadi langkah-langkah diskret yang sesuai dengan tepi jam.

2. Jalur Sinyal 📡

Setiap garis mewakili sinyal, kabel, atau bus data tertentu. Garis-garis ini diberi label dengan nama sepertiCLK, DATA, CS (Pemilihan Chip), atauRST (Reset). Posisi garis secara vertikal memisahkan sinyal-sinyal yang berbeda untuk menghindari kebingungan.

3. Tingkat Logika 🟢🔴

Sinyal biasanya berada dalam keadaan diskret. Dalam logika digital, keadaan tersebut adalah tinggi (logika 1) dan rendah (logika 0). Diagram waktu menunjukkan transisi antara keadaan-keadaan ini. Transisi dari rendah ke tinggi disebut tepi naik. Transisi dari tinggi ke rendah disebut tepi turun.

4. Kejadian dan Transisi 🔄

Kejadian adalah momen-momen tertentu ketika suatu sinyal berubah keadaan. Kejadian-kejadian ini sering ditandai dengan garis vertikal atau panah. Kejadian penting meliputi tepi jam, penangkapan data, dan sinyal pengakuan. Jarak antar kejadian ini menunjukkan durasi.

Membaca Diagram Waktu Secara Efektif 👁️

Membaca diagram ini membutuhkan pendekatan sistematis. Salah memahami urutan kejadian dapat menyebabkan kelemahan desain. Ikuti prinsip-prinsip berikut untuk memastikan akurasi.

- Kiri ke Kanan: Selalu baca timeline dari awal (kiri) ke akhir (kanan). Ini mewakili alur kronologis dari operasi.

- Penyelarasan Vertikal: Kejadian yang tersusun secara vertikal terjadi secara bersamaan. Jika dua sinyal berubah pada garis vertikal yang persis sama, maka keduanya bersamaan (concurrent).

- Durasi: Panjang horizontal dari suatu keadaan sinyal menunjukkan berapa lama sinyal tetap dalam keadaan tersebut. Pulsa yang lebar berarti durasi yang lebih panjang.

- Ketergantungan: Cari hubungan sebab-akibat. Perubahan satu sinyal sering memicu perubahan sinyal lain. Diagram ini menunjukkan latensi antara pemicu-pemicu tersebut.

Sistem Sinkron vs. Asinkron 🔄

Diagram waktu berbeda secara signifikan tergantung pada apakah sistem tersebut sinkron atau asinkron. Memahami perbedaan ini sangat penting untuk analisis yang akurat.

Sistem Sinkron ⏰

Sistem-sistem ini bergantung pada sinyal jam global. Semua perubahan keadaan terjadi pada tepi jam tertentu (naik atau turun). Diagram akan menunjukkan pola jam yang teratur. Data hanya diambil (sampled) ketika jam mengizinkan. Ini membuat waktu menjadi dapat diprediksi tetapi menimbulkan keterbatasan seperti waktu setup dan hold.

Sistem Asinkron 🕰️

Sistem-sistem ini tidak bergantung pada jam global. Perubahan keadaan terjadi ketika sinyal input berubah. Diagram waktu di sini terlihat kurang teratur. Fokusnya pada protokol handshaking. Salah satu sinyal harus naik dahulu, lalu sinyal lainnya, lalu kembali turun. Ini memerlukan analisis teliti terhadap keterlambatan untuk mencegah kondisi balapan (race conditions).

Parameter Kritis dalam Analisis Waktu ⚙️

Selain sekadar menggambar garis, insinyur menganalisis parameter-parameter tertentu untuk memastikan keandalan. Parameter-parameter ini menentukan jendela di mana sistem berfungsi dengan benar.

- Keterlambatan Propagasi: Waktu yang dibutuhkan sinyal untuk menempuh perjalanan dari input ke output melalui suatu komponen. Keterlambatan ini menumpuk di seluruh gerbang logika.

- Waktu Setup: Waktu minimum sebelum tepi jam di mana data harus stabil. Jika data berubah terlalu terlambat, flip-flop tidak dapat menangkapnya dengan benar.

- Waktu Hold: Waktu minimum setelah tepi jam di mana data harus tetap stabil. Jika data berubah terlalu cepat, nilai saat ini akan hilang.

- Skew Jam: Perbedaan waktu kedatangan sinyal jam di komponen-komponen yang berbeda. Skew yang tinggi dapat menyebabkan pelanggaran waktu setup atau hold.

- Metastabilitas: Suatu keadaan di mana output flip-flop bukanlah tinggi maupun rendah. Keadaan ini terjadi ketika waktu setup atau hold dilanggar. Diagram waktu membantu memvisualisasikan risiko metastabilitas.

Aplikasi dalam Perangkat Keras dan Perangkat Lunak 🔌

Diagram waktu tidak terbatas pada perangkat keras. Mereka juga digunakan secara luas dalam arsitektur perangkat lunak dan desain protokol.

Desain Perangkat Keras

Dalam perangkat keras, diagram ini memvalidasi protokol bus. Misalnya, memverifikasi bahwa bus alamat stabil sebelum strobe baca aktif. Mereka memastikan bahwa waktu akses memori sesuai dengan kecepatan jam prosesor. Mereka juga digunakan untuk menganalisis lonjakan konsumsi daya selama transisi sinyal.

Perangkat Lunak dan Protokol

Dalam perangkat lunak, diagram waktu memetakan pemanggilan API atau pertukaran pesan. Mereka menunjukkan urutan permintaan dan respons antar layanan. Ini membantu mengidentifikasi masalah latensi dalam sistem terdistribusi. Mereka menjelaskan urutan operasi dalam lingkungan berbasis banyak thread.

Jebakan dan Kesalahan Umum 🛑

Membuat atau membaca diagram waktu dapat menyebabkan kesalahan jika tidak dilakukan dengan hati-hati. Mengetahui kesalahan umum membantu meningkatkan akurasi.

- Mengabaikan Logika Aktif-Rendah: Banyak sinyal menggunakan logika aktif-rendah (terbalik). Garis yang turun ke rendah bisa berarti sinyal sedang aktif. Selalu periksa legenda atau label.

- Mengasumsikan Transisi Instan:Sinyal nyata memiliki waktu naik dan turun. Diagram ideal menunjukkan garis vertikal, tetapi sinyal fisik miring. Kemiringan ini memengaruhi integritas sinyal.

- Mengabaikan Glitch:Pulsa pendek yang tidak memenuhi persyaratan lebar minimum dapat menyebabkan pemantik palsu. Ini sering disebut glitch.

- Menafsirkan Salah Status High-Z:Status impedansi tinggi berarti sinyal terputus. Dalam diagram, ini tampak seperti garis putus-putus atau simbol tertentu. Mengabaikan ini dapat menyebabkan kesalahan kontes bus.

- Penyelarasan Jam yang Salah: Mengasumsikan semua jam sefase padahal tidak. Perbedaan waktu (skew) dapat menyebabkan data diambil secara salah.

Perbandingan Jenis Diagram 📊

Konteks yang berbeda membutuhkan metode visualisasi yang berbeda. Meskipun diagram waktu sangat kuat, mereka bukan satu-satunya alat.

| Jenis Diagram | Fokus Utama | Paling Cocok Digunakan Untuk |

|---|---|---|

| Diagram Waktu | Waktu dan Status Sinyal | Memverifikasi hubungan jam/data |

| Diagram Status | Status Sistem | Menentukan alur logika dan kondisi |

| Diagram Urutan | Urutan Pesan | Interaksi perangkat lunak dan pemanggilan API |

| Skema Sirkuit | Koneksi Fisik | Pengkabelan dan tata letak komponen |

| Penampil Gelombang | Sinyal Real-Time | Mengoreksi perilaku perangkat keras yang sebenarnya |

Praktik Terbaik untuk Dokumentasi 📝

Untuk membuat diagram waktu berguna bagi tim dan referensi masa depan, ikuti praktik terbaik berikut ini. Dokumentasi yang jelas mengurangi ambiguitas dan mempercepat proses debugging.

- Beri Label Semua Hal: Setiap jalur sinyal harus memiliki nama yang jelas. Hindari label umum seperti Sig1.

- Sertakan Satuan: Tentukan satuan waktu pada sumbu. Apakah kita melihat milidetik atau siklus jam?

- Tandai Titik-Titik Kritis: Soroti jendela setup dan hold secara eksplisit. Gunakan arsiran atau warna yang berbeda untuk menandai jendela waktu kritis.

- Jaga agar Tetap Teratur: Kelompokkan sinyal-sinyal yang terkait bersama. Misalnya, semua sinyal kontrol di bagian atas, sinyal data di bawah.

- Dokumentasikan Asumsi: Catat semua asumsi yang dibuat selama pembuatan. Misalnya, asumsikan penundaan propagasi nol atau kondisi beban tertentu.

- Gunakan Notasi yang Konsisten: Patuhi simbol standar untuk tepi naik, tepi turun, dan keadaan impedansi tinggi.

Panduan Langkah demi Langkah untuk Membuat Diagram 🛠️

Membuat diagram waktu dari awal membutuhkan pendekatan yang terstruktur. Ikuti langkah-langkah berikut untuk memastikan kelengkapan.

- Identifikasi Sinyal: Daftar semua input dan output yang terlibat dalam interaksi.

- Tentukan Urutan: Tentukan urutan kejadian. Apa yang memicu proses tersebut?

- Tentukan Skala Waktu: Putuskan tingkat kerapatan sumbu waktu.

- Gambar Jam: Jika sinkron, gambar sinyal jam terlebih dahulu. Ini menjadi dasar diagram lainnya.

- Tambahkan Data:Plotkan sinyal data relatif terhadap tepi clock.

- Periksa Keterbatasan:Verifikasi waktu setup dan hold terhadap sinyal yang digambar.

- Ulasan:Telusuri timeline untuk memastikan tidak ada celah logis yang ada.

Peran Waktu dalam Debugging 🐞

Ketika suatu sistem gagal, diagram waktu sering menjadi tempat pertama yang dilihat insinyur. Mereka membantu mengidentifikasi apakah masalahnya bersifat logis atau temporal. Jika logikanya benar tetapi waktunya salah, sistem akan gagal secara intermiten. Ini sering lebih sulit direproduksi dibandingkan kesalahan logika yang permanen.

Skenario debugging meliputi:

- Kerusakan Data:Sinyal berubah saat sedang dibaca.

- Interupsi yang Terlewat:Sinyal interupsi terlalu pendek untuk dideteksi.

- Persaingan Bus:Dua perangkat menggerakkan bus pada waktu yang sama.

- Persilangan Domain Clock:Sinyal berpindah antara frekuensi clock yang berbeda tanpa sinkronisasi yang tepat.

Memahami Lebar Data dan Penyelarasan 📐

Diagram waktu juga memvisualisasikan lebar data. Bus paralel membutuhkan beberapa jalur. Setiap jalur harus bertransisi secara sinkron. Ketidakselarasan dapat menyebabkan kesalahan data. Diagram ini menunjukkan bagaimana bit disusun dalam satu siklus clock. Untuk komunikasi serial, diagram waktu menunjukkan aliran bit. Ini menyoroti periode bit dan titik pengambilan sampel.

Topik Lanjutan: Jitter dan Noise 📉

Sinyal dunia nyata tidak sempurna. Jitter adalah penyimpangan tepi clock dari posisi idealnya. Noise adalah fluktuasi acak pada tingkat sinyal. Diagram waktu dapat menggambarkan jitter dengan menampilkan pita tebal di sekitar tepi alih-alih garis tajam. Ini menunjukkan ketidakpastian. Desainer harus memastikan sistem dapat menahan ketidakpastian ini. Margin antara pita jitter dan jendela setup/hold adalah margin keselamatan.

Integrasi dengan Suite Pengujian 🧪

Diagram waktu bukan hanya untuk desain. Mereka digunakan untuk menghasilkan kasus pengujian. Suite pengujian otomatis dapat memeriksa apakah perilaku sistem aktual sesuai dengan diagram. Jika waktu yang diukur menyimpang melebihi toleransi, pengujian gagal. Ini memastikan bahwa perangkat keras atau perangkat lunak memenuhi spesifikasi sepanjang siklus hidupnya.

Kesimpulan tentang Visualisasi Sistem 🎯

Diagram waktu tetap menjadi fondasi teknik sistem. Mereka menutup celah antara logika abstrak dan kenyataan fisik. Dengan memvisualisasikan aliran waktu dan sinyal, insinyur dapat memprediksi kegagalan sebelum terjadi. Mereka memfasilitasi komunikasi antara tim perangkat keras dan perangkat lunak. Diagram yang digambar dengan baik menyampaikan lebih banyak informasi daripada halaman teks. Seiring sistem menjadi lebih cepat dan kompleks, kebutuhan akan analisis waktu yang akurat semakin meningkat. Penguasaan diagram ini menjamin desain yang kuat dan andal.

Ingat untuk mengutamakan kejelasan dan akurasi. Hindari asumsi. Verifikasi setiap transisi. Dengan latihan, membaca dan membuat diagram ini menjadi bagian intuitif dari proses desain. Mereka adalah peta yang membimbing pelancong melalui wilayah logika digital.