Di dunia yang rumit dari rekayasa sistem embedded, waktu adalah segalanya. Sebuah mikrokontroler mungkin berfungsi sempurna dalam simulasi tetapi gagal secara kacau di perangkat keras karena beberapa nanodetik keterlambatan. Di sinilah diagram waktu menjadi alat yang tak tergantikan. Representasi visual ini memetakan perilaku sinyal seiring waktu, memberikan gambaran jelas tentang bagaimana komponen berinteraksi dalam sistem digital. Baik Anda sedang mendiagnosis kegagalan komunikasi atau merancang antarmuka peripheral baru, memahami cara membaca dan membuat diagram waktu adalah hal yang mendasar.

Panduan ini membahas mekanisme penting dari penjadwalan sinyal, mulai dari definisi dasar hingga interaksi protokol yang kompleks. Kami akan mengeksplorasi cara menafsirkan bentuk gelombang, membuat diagram yang akurat dari data pengukuran, serta mengidentifikasi jebakan umum yang menyebabkan ketidakstabilan sistem. Dengan menguasai alat visual ini, Anda mendapatkan kemampuan untuk memprediksi perilaku sistem dan memvalidasi desain sebelum desain tersebut bahkan meninggalkan meja kerja.

🔍 Memahami Dasar-Dasar Penjadwalan Sinyal

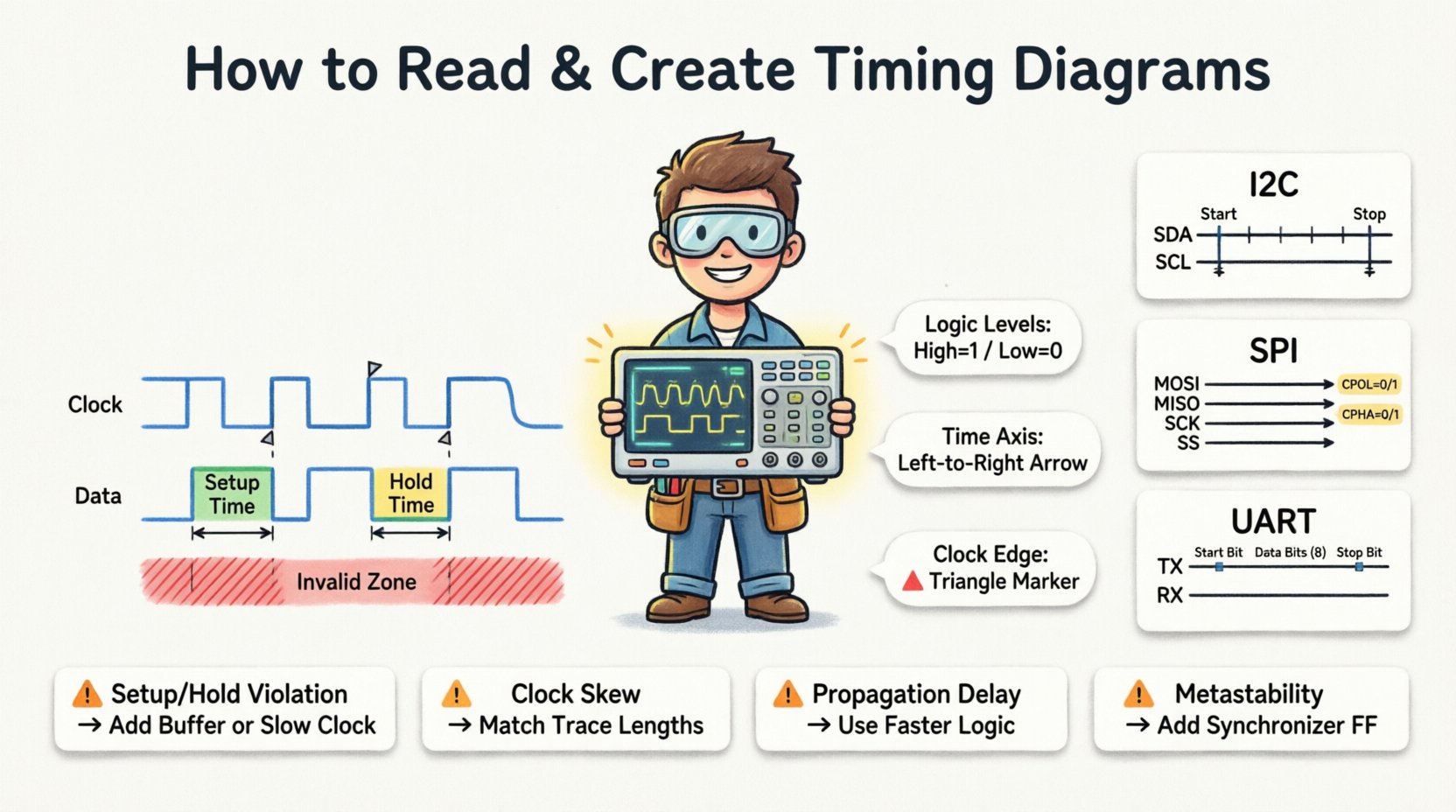

Diagram waktu bukan sekadar gambar; ia merupakan representasi matematis dari keadaan logis relatif terhadap sumbu waktu. Dalam sistem embedded, kita terutama berurusan dengan tingkat logika digital, yang bersifat biner: Tinggi (1) dan Rendah (0). Namun, transisi antara tingkat-tingkat ini justru merupakan sumber kompleksitas.

- Tingkat Logika:Sebagian besar sistem embedded beroperasi pada ambang tegangan tertentu. Sebagai contoh, sistem 3,3V mendefinisikan Tinggi sebagai semua nilai di atas 2,0V dan Rendah sebagai semua nilai di bawah 0,8V.

- Sumbu Waktu:Waktu mengalir dari kiri ke kanan. Jarak horizontal mewakili durasi keadaan tertentu atau keterlambatan antar kejadian.

- Jejak Sinyal:Setiap garis horizontal mewakili kabel atau jaringan tertentu. Banyak garis yang ditumpuk secara vertikal memungkinkan perbandingan hubungan antar sinyal.

Saat menganalisis suatu sistem, Anda mencari kausalitas. Apakah sinyal clock memicu perubahan data? Apakah sinyal enable perlu aktif sebelum data menjadi valid? Diagram waktu menjawab pertanyaan-pertanyaan ini secara visual.

🛠️ Komponen Kunci dari Diagram Waktu

Untuk menafsirkan diagram dengan benar, Anda harus mengenali elemen-elemen standar yang digunakan untuk menunjukkan perilaku sinyal. Komponen-komponen ini menentukan aturan berinteraksi bagi perangkat keras.

| Komponen | Deskripsi | Indikator Visual |

|---|---|---|

| Nama Sinyal | Mengidentifikasi kabel atau jaringan tertentu | Label teks di sebelah kiri |

| Tingkat Logika | Keadaan Tinggi (1) atau Rendah (0) | Garis horizontal datar di bagian atas atau bawah |

| Sudut Transisi | Perubahan dari Tinggi ke Rendah atau sebaliknya | Garis vertikal yang menghubungkan tingkat-tingkat |

| Sudut Clock | Titik pemicu untuk logika sinkron | Garis putus-putus atau tanda segitiga |

| Zona Tidak Valid | Wilayah di mana data tidak dapat dibaca | Area yang diarsir atau bergaris |

Memahami komponen-komponen ini memungkinkan Anda menganalisis interaksi yang kompleks. Sebagai contoh, area yang diarsir sering menunjukkan persyaratan waktu setup atau hold di mana perangkat penerima tidak dapat menangkap data secara andal.

👁️ Cara Membaca Diagram Waktu Langkah demi Langkah

Membaca diagram waktu memerlukan pendekatan sistematis. Anda pada dasarnya menerjemahkan pola visual menjadi urutan kejadian. Ikuti proses ini untuk memastikan akurasi.

1. Identifikasi Sumber Clock

Sebagian besar sistem embedded bersifat sinkron, yang berarti sinyal clock menentukan kecepatan operasi. Temukan jalur clock. Biasanya menunjukkan gelombang persegi yang teratur dan periodik.

- Periksa frekuensinya. Apakah 1 MHz atau 100 MHz? Ini menentukan kecepatan seluruh sistem.

- Identifikasi jenis tepi. Apakah perangkat beroperasi pada tepi naik (Rendah ke Tinggi) atau tepi turun (Tinggi ke Rendah)?

2. Peta Jendela Validitas Data

Data hanya valid selama jendela tertentu yang berkaitan dengan clock. Perhatikan hubungan antara tepi clock dan jalur data.

- Waktu Setup: Data harus stabil selama periode tertentu sebelumtepi clock.

- Waktu Hold: Data harus tetap stabil selama periode tertentu setelahtepi clock.

Jika data berubah selama jendela-jendela ini, terjadi pelanggaran waktu, yang dapat menyebabkan metastabilitas atau penangkapan data yang salah.

3. Analisis Sinyal Kendali

Sinyal kendali seperti Chip Select (CS), Enable (EN), atau Reset (RST) menentukan kapan komunikasi dapat terjadi.

- Apakah Chip Select aktif rendah atau aktif tinggi?

- Apakah sinyal Enable perlu dinyatakan sebelum clock mulai berubah-ubah?

- Apakah ada peristiwa asinkron yang menggantikan logika clock?

4. Verifikasi Mekanisme Handshaking

Banyak protokol menggunakan handshaking untuk mengelola kontrol aliran. Perhatikan sinyal Acknowledge (ACK) atau Ready (RDY).

- Apakah pengirim menunggu sinyal sebelum mengirim byte berikutnya?

- Apakah ada kondisi timeout yang diwakili dalam diagram?

📐 Cara Membuat Diagram Waktu yang Akurat

Membuat diagram waktu sebanding pentingnya dengan membacanya. Diagram ini berfungsi sebagai spesifikasi bagi insinyur perangkat keras dan panduan verifikasi bagi pengembang perangkat lunak. Anda dapat membuatnya dari persyaratan, alat pengukuran, atau data simulasi.

Langkah 1: Tentukan Persyaratan Protokol

Sebelum menggambar, kumpulkan spesifikasi. Biasanya spesifikasi ini berasal dari datasheet komponen yang sedang Anda hubungkan.

- Ekstrak frekuensi jam minimum dan maksimum.

- Catat tingkat tegangan untuk logika Tinggi dan Rendah.

- Catat batasan waktu setup dan hold.

Langkah 2: Tangkap Data Sinyal

Gunakan alat perangkat keras untuk menangkap perilaku dunia nyata. Ini memastikan diagram Anda mencerminkan kenyataan, bukan idealisme teoretis.

- Osiloskop:Terbaik untuk integritas sinyal analog dan tingkat tegangan.

- Penganalisis Logika:Terbaik untuk transisi keadaan digital dan waktu multi-saluran.

- Model Simulasi:Cocok untuk memverifikasi logika sebelum perangkat keras tersedia.

Langkah 3: Plot Gelombang Sinyal

Gambar sinyal secara kronologis. Pastikan skala waktu konsisten di semua saluran.

- Gunakan garis lurus untuk tingkat logika.

- Gunakan garis miring untuk transisi agar menunjukkan waktu naik dan turun.

- Beri label pada titik-titik penting seperti tepi jam dan perubahan data.

Langkah 4: Beri Keterangan pada Batasan Penting

Keterangan memberikan konteks yang tidak dapat disampaikan oleh visual saja.

- Beri tanda jendela waktu setup dan hold secara eksplisit.

- Tunjukkan durasi keadaan protokol tertentu (misalnya, Bit Mulai, Bit Berhenti).

- Soroti setiap latensi atau keterlambatan yang diketahui dalam jalur sinyal.

🌐 Diagram Waktu dalam Protokol Embedded Umum

Protokol komunikasi yang berbeda memiliki karakteristik waktu yang berbeda. Memahami perbedaan halus ini sangat penting untuk integrasi.

1. Sirkuit Terpadu Antar (I2C)

I2C adalah bus serial sinkron dua kabel. Ia menggunakan SDA (Data) dan SCL (Jam).

- Kondisi Mulai: SDA bertransisi dari Tinggi ke Rendah saat SCL dalam keadaan Tinggi.

- Kondisi Berhenti:SDA berpindah dari Rendah ke Tinggi saat SCL tinggi.

- Transfer Data:Data valid saat SCL tinggi; perubahan terjadi saat SCL rendah.

- ACK/NACK:Penerima menarik SDA rendah selama pulsa jam kesembilan untuk mengonfirmasi penerimaan.

2. Antarmuka Periferal Serial (SPI)

SPI adalah bus sinkron empat kabel yang menawarkan kecepatan lebih tinggi daripada I2C.

- Kabel:MOSI (Master Keluar), MISO (Master Masuk), SCK (Jam), SS (Pemilih Slave).

- CPOL:Polaritas Jam menentukan keadaan idle (Tinggi atau Rendah).

- CPHA:Fasa Jam menentukan kapan data diambil (pada tepi pertama atau kedua).

- Pemilihan Chip:Harus dinyatakan (aktif) sebelum jam mulai berpindah.

3. Penerima-Pengirim Asinkron Universal (UART)

UART bersifat asinkron, artinya tidak ada sinyal jam bersama. Waktu bergantung pada laju baud.

- Bit Mulai:Menarik kabel ke rendah untuk menandakan awal dari sebuah frame.

- Bit Data:Dikirimkan bit paling tidak signifikan terlebih dahulu, biasanya 8 bit.

- Bit Berhenti:Menarik kabel ke tinggi untuk menandakan akhir dari sebuah frame.

- Paritas:Bit opsional untuk pemeriksaan kesalahan.

| Fitur | I2C | SPI | UART |

|---|---|---|---|

| Jam | Sinkron (Berbagi) | Sinkron (Berbagi) | Asinkron (Tanpa Jam) |

| Kabel | 2 (SDA, SCL) | 4+ (MOSI, MISO, SCK, SS) | 2 (TX, RX) |

| Penentuan Alamat | Ya (Alamat Byte) | Tidak (Berdasarkan Kabel) | Tidak |

| Kecepatan Maksimal | ~400 kHz | ~50 MHz | ~3 Mbps |

⚠️ Pelanggaran Waktu Umum dan Debugging

Bahkan dengan desain yang hati-hati, pelanggaran waktu dapat terjadi. Ini sering menjadi akar masalah dari bug yang bersifat sementara dan sulit direproduksi.

1. Pelanggaran Waktu Persiapan dan Waktu Tahan

Ini terjadi ketika data tiba terlalu awal atau terlalu terlambat dibandingkan dengan tepi jam.

- Gejala: Kerusakan data atau kesalahan acak dalam tangkapan analis logika.

- Perbaikan: Perlambat kecepatan jam atau optimalkan panjang jalur papan sirkuit (PCB).

2. Penyimpangan Jam

Penyimpangan jam terjadi ketika sinyal jam tiba di komponen yang berbeda pada waktu yang berbeda.

- Gejala:Kondisi persaingan di mana satu flip-flop menangkap data sebelum yang lain siap.

- Perbaikan: Sesuaikan panjang jalur atau gunakan jaringan distribusi jam khusus.

3. Penundaan Propagasi

Sinyal membutuhkan waktu untuk menempuh jalur melalui kabel dan gerbang. Jalur yang panjang menambahkan penundaan yang signifikan.

- Gejala:Masalah integritas sinyal atau pantulan pada jalur berkecepatan tinggi.

- Perbaikan:Gunakan resistor terminasi dan buat jalur sependek mungkin.

4. Metastabilitas

Ketika sinyal asinkron melintasi domain jam, flip-flop penerima dapat memasuki keadaan metastabil.

- Gejala:Sistem macet atau reset acak.

- Perbaikan:Gunakan rantai sinkronisasi (dua atau lebih flip-flop secara seri) untuk menyelesaikan sinyal.

📝 Praktik Terbaik untuk Dokumentasi

Membuat diagram waktu untuk dokumentasi memastikan bahwa pengembang masa depan dapat memahami sistem tanpa perlu melakukan reverse engineering perangkat keras.

- Konsistensi:Gunakan simbol dan gaya garis standar di seluruh diagram dalam proyek ini.

- Skala:Pastikan sumbu waktu bersifat linier dan diberi label jelas dengan satuan (ns, µs, ms).

- Referensi:Selalu hubungkan diagram dengan bagian spesifik datasheet atau standar protokol.

- Kesederhanaan:Hindari kekacauan. Jika suatu sinyal tetap, tampilkan sebagai garis datar daripada gangguan yang berubah-ubah.

- Versi:Perbarui diagram setiap kali perangkat keras atau firmware mengalami perubahan signifikan.

🔗 Pikiran Akhir tentang Integritas Sinyal

Diagram waktu menghubungkan celah antara logika abstrak dan kenyataan fisik. Mereka memungkinkan insinyur untuk memvisualisasikan batasan tak terlihat dari elektronika digital. Dengan belajar membacanya, Anda dapat mendiagnosis masalah perangkat keras yang kompleks. Dengan belajar membuatnya, Anda dapat merancang sistem yang tangguh yang berfungsi secara andal dalam semua kondisi.

Proses ini melibatkan kesabaran dan perhatian terhadap detail. Setiap tepi, setiap penundaan, dan setiap tingkat tegangan sangat penting. Seiring sistem tertanam menjadi lebih cepat dan kompleks, ketergantungan pada diagram waktu yang akurat akan terus meningkat. Anggaplah diagram ini sebagai spesifikasi kritis, bukan dokumentasi opsional.

Mulailah dengan menganalisis datasheet komponen yang Anda gunakan. Cari spesifikasi waktu. Kemudian, coba gambar diagram berdasarkan angka-angka tersebut. Bandingkan gambar Anda dengan pengukuran aktual dari alat Anda. Siklus prediksi dan verifikasi ini membangun intuisi yang diperlukan untuk desain embedded tingkat tinggi.

Ingatlah bahwa diagram adalah alat komunikasi. Harus menyampaikan informasi yang diperlukan kepada insinyur lain dengan ambiguitas sekecil mungkin. Diagram waktu yang jelas dan akurat mengurangi waktu pengembangan dan mencegah revisi perangkat keras yang mahal. Luangkan waktu untuk menguasai keterampilan ini, dan itu akan memberi manfaat sepanjang karier teknik Anda.