Komunikasi rekayasa sangat bergantung pada presisi visual. Saat membahas interaksi sistem, propagasi sinyal, atau aliran data, diagram waktu yang dibuat dengan baik berfungsi sebagai bahasa universal. Diagram ini menangkap hubungan antar peristiwa sepanjang waktu, memungkinkan insinyur mendiagnosis masalah, memverifikasi logika, dan mendokumentasikan perilaku sistem secara efektif. Namun, diagram yang berantakan, ambigu, atau berskala tidak tepat dapat menyebabkan kesalahpahaman yang mahal. Panduan ini menjelaskan standar penting untuk membuat diagram yang menyampaikan kebenaran teknis tanpa kebingungan.

📊 Memahami Dasar-Dasar Diagram Waktu

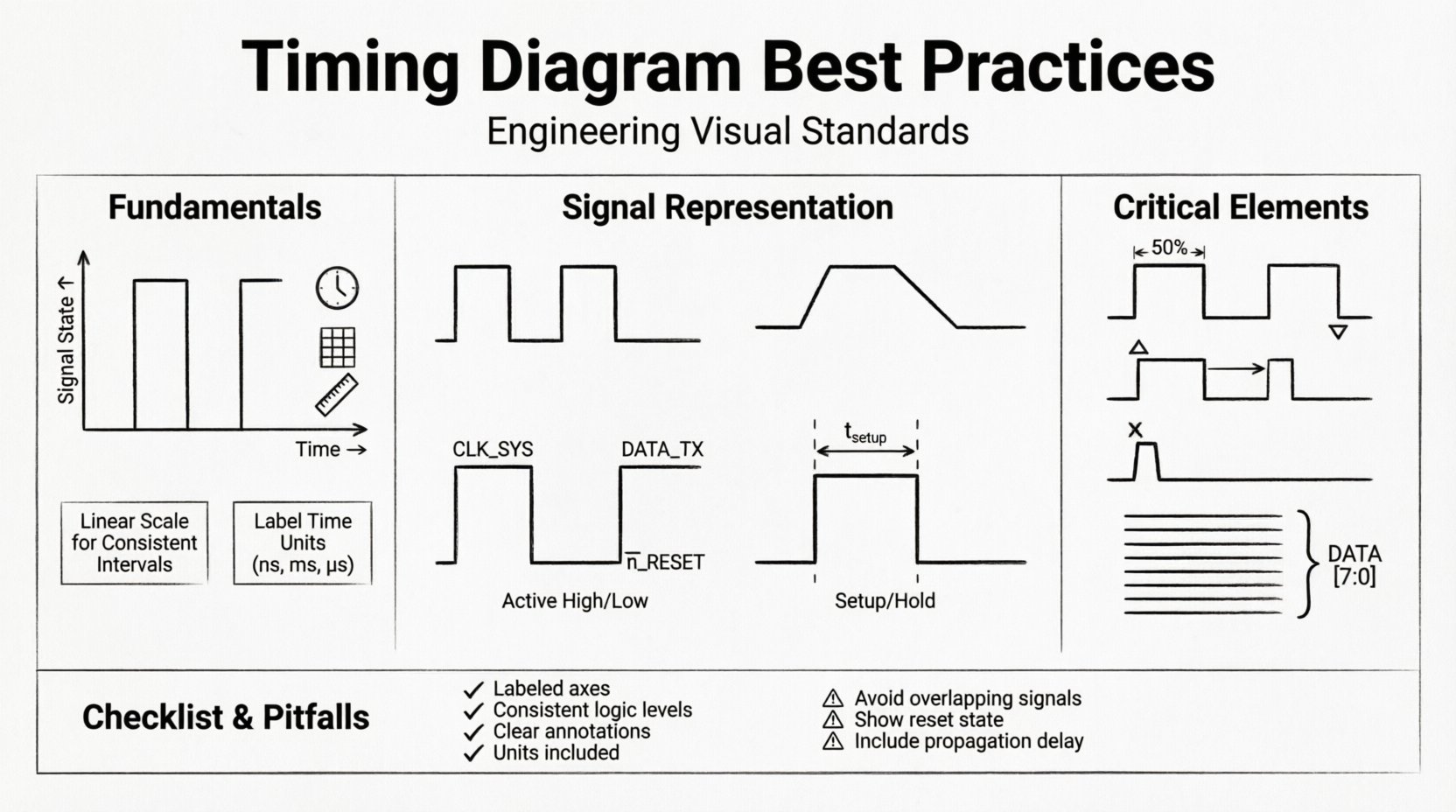

Diagram waktu adalah representasi grafis tentang bagaimana sinyal berubah keadaan sepanjang waktu. Ini bukan sekadar gambar; ini adalah spesifikasi. Baik Anda bekerja pada antarmuka perangkat keras, sistem tertanam, atau protokol perangkat lunak, prinsip dasar yang sama tetap berlaku: waktu mengalir secara horizontal, dan keadaan sinyal digambarkan secara vertikal. Kejelasan dalam konteks ini bukanlah kemewahan; ini adalah keharusan untuk keselamatan dan keandalan.

Saat membuat visualisasi ini, tujuannya adalah mengurangi beban kognitif bagi pembaca. Mereka seharusnya tidak harus menebak di mana jam dimulai, garis mana yang mewakili data, atau berapa ambang tegangan yang digunakan. Setiap elemen harus memiliki tujuan yang jelas.

- Sumbu Waktu: Dimensi horizontal mewakili perkembangan waktu. Ini bisa linear atau logaritmik tergantung pada peristiwa yang direkam.

- Garis Sinyal: Dimensi vertikal mewakili keadaan suatu sinyal, seperti Tinggi/Rendah, 1/0, atau tingkat tegangan.

- Peristiwa: Titik-titik tertentu dalam waktu ketika terjadi perubahan, seperti tepi, pulsa, atau transfer data.

📏 Menyiapkan Kanvas dan Skala Anda

Dasar dari diagram yang jelas adalah kisi. Tanpa skala yang konsisten, hubungan antar peristiwa menjadi terdistorsi. Sketsa yang tampak benar pada satu tingkat zoom dapat mengungkap pelanggaran waktu kritis pada tingkat zoom lainnya.

1. Menentukan Skala Waktu

Skala waktu harus dipilih berdasarkan peristiwa tercepat dalam sistem. Jika Anda mendokumentasikan interaksi tingkat mikrodetik, menggambar timeline dalam milidetik akan menyembunyikan rincian. Sebaliknya, jika peristiwa berlangsung dalam hitungan detik, skala mikrodetik akan menciptakan kebisingan yang tidak perlu. Selalu label satuan waktu dengan jelas pada sumbu.

- Skala Linear: Gunakan ini untuk interval yang konsisten. Ini adalah standar untuk dokumentasi protokol sebagian besar.

- Skala Logaritmik: Jarang digunakan, tetapi diperlukan ketika peristiwa mencakup berbagai orde besar (misalnya, penundaan startup dibandingkan dengan waktu pemrosesan).

2. Garis Kisi dan Titik Referensi

Garis kisi membantu mata melacak interval waktu di seluruh diagram. Garis kisi tebal harus menandai satuan utama (misalnya, 10ms), sementara garis lebih tipis menandai satuan kecil (misalnya, 1ms). Hierarki visual ini mencegah pembaca kehilangan arah.

Pastikan garis kisi vertikal sejajar dengan peristiwa penting. Jika tepi jam jatuh tepat pada garis kisi, ini memberikan titik acuan alami untuk membaca waktu setup dan hold. Jangan memaksa peristiwa agar sesuai dengan kisi jika peristiwa tersebut mewakili pengukuran dunia nyata; alih-alih, sesuaikan kisi atau gunakan anotasi untuk menunjukkan pergeseran.

⚡ Mewakili Sinyal Secara Akurat

Cara menggambar suatu sinyal menentukan bagaimana sinyal tersebut diinterpretasikan. Tepi naik mengimplikasikan transisi dari rendah ke tinggi, tetapi kecepatan dan bentuk transisi tersebut dapat membawa makna terkait integritas sinyal.

1. Keadaan dan Tingkat Sinyal

Tentukan secara jelas apa yang membentuk keadaan logis. Dalam logika digital, ini biasanya 0 (Rendah) dan 1 (Tinggi). Dalam konteks analog atau sinyal campuran, tingkat tegangan (misalnya, 0V hingga 5V) diperlukan. Gunakan gaya garis yang berbeda untuk membedakan antara:

- Aktif Tinggi: Sinyal benar ketika garis berada pada level atas.

- Aktif Rendah: Sinyal benar ketika garis berada pada level bawah (sering dilambangkan dengan garis di atas nama sinyal).

2. Representasi Sisi

Sisi adalah bagian paling krusial dari diagram. Mereka menunjukkan momen tepat saat perubahan keadaan terjadi. Gunakan garis tajam dan padat untuk transisi ideal. Jika Anda perlu merepresentasikan laju perubahan fisik atau waktu naik, gambarlah sebagai garis miring alih-alih puncak vertikal.

Hindari garis bergelombang kecuali Anda secara khusus mendokumentasikan gangguan atau kegagalan sinyal. Garis yang bersih menunjukkan stabilitas; garis bergelombang menunjukkan gangguan. Buatlah pilihan secara sengaja terhadap bentuk yang Anda gambar.

3. Konvensi Penamaan Sinyal

Nama sinyal bukan sekadar label; itu adalah definisi. Hindari nama umum sepertiSignal_A atau Kabel_1. Sebaliknya, gunakan nama fungsional yang menggambarkan tujuan, sepertiCLOCK_SYS atau DATA_TX.

- Awalan: Gunakan awalan standar untuk menunjukkan jenis sinyal (misalnya,

Nuntuk logika negatif,CLKuntuk clock). - Kasus: Gunakan huruf kapital untuk konstanta dan sinyal, campuran huruf besar dan kecil untuk variabel jika berlaku.

- Konsistensi: Pastikan nama pada diagram sama persis dengan nama dalam kode atau datasheet.

⏱️ Penjadwalan dan Sinkronisasi

Jam menggerakkan waktu pada sistem sinkron. Menyajikan jam secara keliru dapat membuat seluruh diagram menjadi tidak valid. Sinyal jam sering menjadi titik referensi pertama yang diperiksa pembaca.

1. Siklus Tugas dan Periode

Gambar sinyal jam dengan siklus tugas yang konsisten kecuali sistem secara khusus membutuhkan waktu yang bervariasi. Jika siklus tugas bukan 50%, beri keterangan durasi tinggi dan rendah. Periode (waktu untuk satu siklus lengkap) harus ditandai dengan jelas.

Untuk sistem frekuensi bervariasi, jangan asumsikan panjang garis yang konstan mewakili waktu yang konstan. Beri label pada setiap periode secara terpisah jika berbeda secara signifikan.

2. Pemicu Sisi

Tunjukkan apakah sistem dipicu pada sisi naik (positif) atau sisi turun (negatif). Anda dapat menggunakan panah atau segitiga kecil di titik sisi tersebut. Ini sangat penting untuk memahami kapan data diambil.

- Tepi Naik:Tandai dengan segitiga kecil yang mengarah ke atas.

- Tepi Turun:Tandai dengan segitiga kecil yang mengarah ke bawah.

3. Jitter dan Fase

Pada sistem berkecepatan tinggi, jitter (perubahan dalam waktu) merupakan faktor yang diketahui. Jika Anda menggambar ideal teoretis, garis lurus sudah cukup. Jika Anda mendokumentasikan perilaku yang diukur, gunakan daerah yang diarsir atau beberapa jejak untuk menunjukkan variasi. Hubungan fase antara beberapa clock harus dinyatakan secara eksplisit.

🔄 Penanganan Transisi Data

Sinyal data sering lebih kompleks daripada clock. Perubahan terjadi berdasarkan keadaan sistem. Mendokumentasikan transisi ini secara tepat memerlukan perhatian terhadap hubungan antara data dan clock.

1. Waktu Setup dan Waktu Hold

Ini adalah batasan kritis untuk penangkapan data yang dapat diandalkan. Waktu setup adalah durasi sebelum tepi clock di mana data harus stabil. Waktu hold adalah durasi setelah tepi clock di mana data harus tetap stabil. Visualisasikan ini sebagai jendela yang relatif terhadap tepi clock.

Gambar garis putus-putus vertikal untuk menunjukkan jendela setup dan hold. Beri label durasi dalam satuan waktu (misalnya, t_setup = 5ns). Ini memvisualisasikan margin yang tersedia agar sistem dapat berfungsi dengan benar.

2. Meta-stabilitas

Ketika sinyal melintasi domain clock, meta-stabilitas dapat terjadi. Ini adalah keadaan di mana sinyal tidak sepenuhnya tinggi maupun rendah. Representasikan ini dengan garis putus-putus atau arsiran khusus dalam jendela waktu. Mendokumentasikan hal ini memperingatkan pembaca bahwa sinyal mungkin membutuhkan waktu lebih lama dari biasanya untuk terselesaikan.

3. Glitch dan Gangguan

Pulsa tidak sah, yang dikenal sebagai glitch, dapat menyebabkan kesalahan logika. Jika glitch merupakan masalah yang diketahui, gambarlah sebagai pulsa sempit yang tidak memenuhi persyaratan lebar pulsa minimum dari logika penerima. Jangan menyembunyikan artefak ini; seringkali mereka adalah akar penyebab kegagalan yang bersifat sesekali.

🏷️ Anotasi dan Penandaan

Teks pada diagram membawa bobot. Memadati diagram dengan teks membuatnya tidak dapat dibaca. Kurangnya penandaan membuatnya ambigu. Temukan keseimbangan melalui penempatan strategis.

1. Penempatan Teks

Tempatkan teks di dekat bagian relevan dari sinyal tetapi hindari tumpang tindih dengan garis sinyal. Gunakan garis penunjuk (garis tipis yang menghubungkan teks dengan sinyal) jika sinyal terlalu ramai untuk menempatkan teks langsung di atas atau di bawahnya.

2. Satuan dan Simbol

Selalu sertakan satuan. Waktu harus dalam detik, milidetik, atau nanodetik. Tegangan harus dalam volt. Jangan mengandalkan pembaca untuk menebak. Gunakan simbol standar untuk operasi logika (misalnya, ! untuk NOT, & untuk AND) jika Anda menampilkan persamaan logika bersamaan dengan waktu.

3. Kemudahan Dibaca

Ukuran font penting. Dalam dokumen cetak atau di layar, teks harus dapat dibaca tanpa perlu memperbesar. Jika diagram kompleks, pertimbangkan untuk membaginya menjadi beberapa tampilan: gambaran umum tingkat tinggi dan tampilan dekat rinci dari peristiwa tertentu.

🚫 Kesalahan Umum yang Harus Dihindari

Bahkan insinyur yang berpengalaman membuat kesalahan saat membuat visualisasi ini. Kesadaran akan kesalahan umum dapat menghemat berjam-jam debugging.

- Mengabaikan Penundaan Propagasi:Sinyal membutuhkan waktu untuk menempuh jalur melalui kabel dan gerbang logika. Jika sinyal berubah di titik A dan tiba di titik B, gambarkan penundaannya. Garis vertikal di titik B menyiratkan perjalanan instan, yang secara fisik tidak mungkin terjadi.

- Tingkat Logika yang Tidak Konsisten:Pastikan definisi High dan Low tidak berubah di tengah diagram. Ini membingungkan dan berbahaya.

- Sinyal yang Tumpang Tindih:Jika dua sinyal harus saling melintas, pastikan keduanya dapat dibedakan dengan jelas. Gunakan ketebalan garis atau warna yang berbeda jika diperbolehkan oleh media output.

- Kondisi Reset yang Hilang:Sistem sering kali dimulai dalam keadaan tertentu. Tunjukkan keadaan awal sebelum jam mulai berjalan. Ini mencegah kebingungan tentang apa yang dilakukan sinyal pada waktu nol.

🧠 Pertimbangan Lanjutan

Ketika sistem menjadi lebih kompleks, diagram waktu harus berkembang untuk menangani skenario multi-saluran dan asinkron.

1. Penjadwalan Multi-Saluran

Ketika menangani bus (seperti bus data), kelompokkan sinyal-sinyal yang terkait bersama. Gunakan kurung untuk menunjukkan bahwa garis-garis di atas mewakili lebar bus (misalnya, DATA[7:0]). Tunjukkan transisi seluruh kelompok untuk menunjukkan transfer paralel.

2. Penyambungan Asinkron

Tidak semua sistem menggunakan jam global. Protokol penyambungan bergantung pada sinyal permintaan dan konfirmasi. Gambar dengan jelas menggunakan panah yang menunjukkan arah penyambungan. Tunjukkan status tunggu di mana sistem berhenti sampai sinyal diterima.

3. Status Manajemen Daya

Sistem modern memasuki mode hemat daya. Tunjukkan transisi ini pada diagram waktu. Sinyal mungkin turun untuk menunjukkan mode tidur, tetapi jam mungkin berhenti atau melambat. Dokumentasikan status daya bersamaan dengan status waktu.

✅ Daftar Periksa Tinjauan

Sebelum menyelesaikan diagram, lakukan pemeriksaan daftar ini untuk memastikan kepatuhan terhadap praktik terbaik.

| Item Pemeriksaan | Kriteria |

|---|---|

| Sumbu Waktu | Apakah skala linear dan diberi label satuan? |

| Nama Sinyal | Apakah semua sinyal diberi nama secara fungsional dan konsisten? |

| Sudut Jam | Apakah tepi naik/turun dengan jelas ditandai? |

| Transisi | Apakah waktu setup/hold terlihat dan diberi label? |

| Keterlambatan | Apakah keterlambatan propagasi disertakan di tempat yang relevan? |

| Anotasi | Apakah teks mudah dibaca dan bebas dari tumpang tindih? |

| Satuan | Apakah semua pengukuran disertai satuan (ns, V, dll.)? |

| Keadaan Awal | Apakah keadaan reset atau idle ditampilkan di awal? |

| Kesederhanaan | Apakah insinyur sejawat dapat memahami ini tanpa harus bertanya? |

📝 Pikiran Akhir tentang Dokumentasi

Kualitas diagram waktu mencerminkan kualitas rekayasa di baliknya. Diagram yang jelas memfasilitasi kolaborasi antara tim perangkat keras dan perangkat lunak, mengurangi waktu debugging, dan memastikan bahwa pemelihara masa depan memahami perilaku sistem. Ini adalah alat untuk kebenaran, bukan sekadar ilustrasi.

Fokus pada presisi daripada estetika. Meskipun diagram yang cantik terasa menyenangkan, diagram yang benar sangat penting. Luangkan waktu untuk memverifikasi pengukuran, beri label pada setiap batasan, dan sesuaikan bahasa visual Anda dengan spesifikasi teknis. Dengan mengikuti praktik-praktik ini, Anda memastikan informasi waktu tetap terjaga secara akurat sepanjang siklus hidup produk.

Ingat, diagram ini adalah kontrak. Ini mendefinisikan bagaimana sistem berperilaku. Saat Anda menggambar garis, Anda membuat janji tentang perilaku sinyal. Pertahankan janji itu dengan jelas, akurat, dan tidak ambigu.

Menerapkan standar ini meningkatkan profesionalisme dokumentasi Anda. Ini menandakan kepada tim dan pemangku kepentingan bahwa Anda menghargai keandalan dan kejelasan. Dalam dunia desain sistem yang kompleks, diagram yang baik sering menjadi perbedaan antara peluncuran yang sukses dan masalah yang terus berulang.

🔧 Kesimpulan

Membuat diagram waktu yang efektif membutuhkan pendekatan disiplin terhadap tata letak, penandaan, dan representasi. Dengan memprioritaskan kejelasan, konsistensi, dan akurasi teknis, insinyur dapat menghasilkan visual yang berfungsi sebagai referensi andal untuk pengembangan dan pemeliharaan. Ikuti panduan mengenai representasi sinyal, sinkronisasi jam, dan anotasi untuk memastikan dokumentasi Anda mampu bertahan terhadap ujian waktu dan kompleksitas.