Diagram waktu adalah alat penting untuk memvisualisasikan perilaku sinyal digital selama periode tertentu. Di bidang elektronika digital dan teknik komputer, memahami bagaimana sinyal berinteraksi sangat penting untuk stabilitas dan kinerja sistem. Panduan ini memberikan penjelasan mendalam mengenai notasi diagram waktu, memastikan Anda dapat membaca, membuat, dan menafsirkan gelombang dengan presisi. Kami akan mengeksplorasi tingkat sinyal, sumbu waktu, transisi, dan parameter waktu kritis tanpa bergantung pada alat perangkat lunak tertentu.

🔍 Memahami Komponen Utama Diagram Waktu

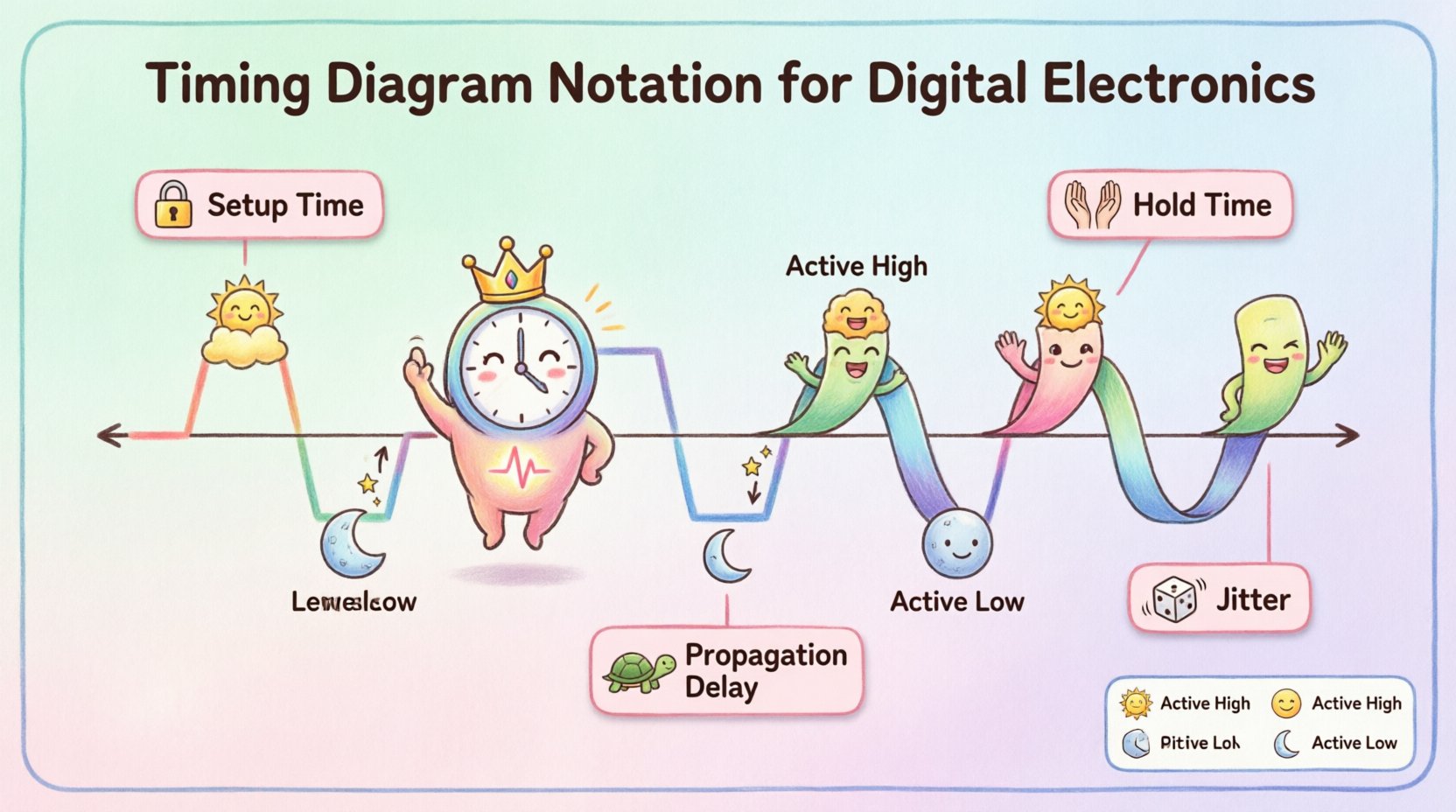

Pada dasarnya, diagram waktu mewakili keadaan logis sinyal relatif terhadap waktu. Diagram ini berfungsi sebagai gambaran rancangan bagaimana data bergerak melalui suatu sistem. Untuk menafsirkan diagram ini secara benar, seseorang harus memahami sumbu dasar dan representasi sinyal.

- Sumbu Horizontal:Mewakili waktu. Sumbu ini mengalir dari kiri ke kanan, menunjukkan urutan kejadian.

- Sumbu Vertikal:Mewakili keadaan logis atau tingkat tegangan dari saluran sinyal tertentu.

- Garis Sinyal:Setiap garis horizontal sesuai dengan kabel tertentu, jaringan, atau variabel logis dalam rangkaian.

- Tingkat Logika:Sinyal umumnya berpindah antara dua keadaan, biasanya disebut Tinggi dan Rendah.

Saat menganalisis diagram waktu, penonton mencari hubungan antara perubahan pada satu sinyal dan perubahan pada sinyal lainnya. Hubungan ini menentukan apakah data ditangkap dengan benar atau terjadi kesalahan. Notasi yang tepat memastikan hubungan ini tidak ambigu bagi insinyur yang meninjau desain.

⚡ Tingkat dan Keadaan Logika Sinyal

Sistem digital beroperasi berdasarkan prinsip biner, tetapi representasi fisiknya bervariasi. Notasi harus dengan jelas mendefinisikan apa yang membentuk satu logis dan nol logis. Salah menafsirkan tingkat ini dapat menyebabkan kegagalan desain yang mengerikan.

Tinggi Aktif vs. Rendah Aktif

Sinyal dapat aktif saat berada pada tingkat tinggi atau aktif saat berada pada tingkat rendah. Konsep ini sangat penting untuk sinyal kontrol seperti reset atau enable.

- Tinggi Aktif:Sinyal melakukan fungsinya ketika tegangan tinggi (logika 1). Ini adalah standar untuk sebagian besar jalur data.

- Rendah Aktif:Sinyal melakukan fungsinya ketika tegangan rendah (logika 0). Sinyal kontrol sering menggunakan notasi ini untuk mengurangi gangguan atau sesuai dengan kebutuhan perangkat keras tertentu.

- Indikator Notasi:Sinyal rendah aktif sering ditandai dengan garis di atas nama atau bulatan di ujung garis dalam diagram skematik.

Tingkat Tegangan Logika

Meskipun logika 0 dan 1 bersifat abstrak, diagram waktu mewakili tegangan fisik. Notasi sebaiknya secara ideal menentukan ambang tegangan.

- Logika Tinggi:Umumnya direpresentasikan oleh tegangan di atas ambang tertentu (misalnya 3,3V atau 5V).

- Logika Rendah:Umumnya direpresentasikan oleh tegangan di bawah ambang tertentu (misalnya 0V).

- Zona Tidak Didefinisikan: Area di antara ambang tinggi dan rendah di mana status sinyal tidak pasti. Diagram harus menghindari berada di zona ini.

⏱️ Sumbu Waktu dan Sinkronisasi

Representasi waktu adalah aspek kedua yang paling kritis dalam diagram waktu. Berbeda dengan tegangan, waktu bersifat kontinu, tetapi sinyal digital berubah pada saat-saat tertentu. Notasi harus mampu menangani peristiwa sinkron dan asinkron.

Sinyal Jam

Sebagian besar sistem digital bergantung pada jam untuk menyinkronkan operasi. Sinyal jam adalah detak jantung sistem.

- Periode: Waktu yang dibutuhkan untuk satu siklus lengkap jam.

- Frekuensi: Jumlah siklus per detik, biasanya diukur dalam Hertz.

- Duty Cycle: Persentase periode di mana sinyal berada dalam keadaan tinggi.

- Notasi: Sinyal jam sering digambarkan dengan pola gelombang persegi.

Waktu Relatif vs. Waktu Absolut

Diagram waktu dapat menggunakan waktu relatif atau waktu absolut.

- Waktu Relatif: Pengukuran diambil dari titik acuan, seperti tepi jam tertentu. Ini umum digunakan untuk analisis waktu setup dan hold.

- Waktu Absolut: Timestamp tertentu diberikan pada peristiwa, berguna untuk mendiagnosis protokol komunikasi dalam durasi panjang.

Skala Waktu

Memilih skala waktu yang tepat sangat penting untuk kejelasan.

- Nanosekon: Digunakan untuk logika berkecepatan tinggi di mana sinyal berubah dengan cepat.

- Mikrosekon: Digunakan untuk interaksi perangkat peripheral yang lebih lambat.

- Milisekon: Digunakan untuk manajemen daya tingkat sistem atau peristiwa berfrekuensi rendah.

🔄 Transisi Tepi dan Notasi

Momen ketika sinyal berubah status sama pentingnya dengan status itu sendiri. Notasi harus dengan jelas menunjukkan bagaimana dan kapan transisi ini terjadi.

Tepi Naik dan Tepi Turun

Sisi mewakili transisi antara tingkat logika.

- Sisi Naik:Transisi dari Rendah ke Tinggi. Sering ditandai dengan garis vertikal atau panah yang mengarah ke atas.

- Sisi Turun:Transisi dari Tinggi ke Rendah. Sering ditandai dengan garis vertikal atau panah yang mengarah ke bawah.

- Kemiringan:Pada diagram ideal, sisi berupa vertikal. Pada diagram dunia nyata, sisi memiliki kemiringan yang mewakili waktu naik atau waktu turun.

Penundaan Transisi

Sinyal tidak berpindah secara instan. Notasi harus mempertimbangkan penundaan propagasi.

- Penundaan Propagasi:Waktu yang dibutuhkan agar perubahan pada input menghasilkan perubahan pada output.

- Notasi:Sering ditandai dengan jarak antara transisi input dan transisi output.

Glitch dan Bahaya

Transisi yang tidak diinginkan dapat terjadi karena keterlambatan sirkuit. Ini sering ditampilkan sebagai loncatan singkat.

- Glitch:Pulsa pendek yang seharusnya tidak ada. Notasi dapat menggunakan garis putus-putus atau warna yang berbeda.

- Bahaya:Kemungkinan output yang salah akibat perbedaan waktu.

📏 Parameter Waktu Kritis

Beberapa parameter menentukan keandalan antarmuka digital. Ini adalah metrik yang diukur insinyur untuk memastikan integritas data.

| Parameter | Deskripsi | Satuan |

|---|---|---|

| Waktu Siap | Waktu data harus stabil sebelum tepi jam. | Waktu (ns) |

| Waktu Tahan | Waktu data harus tetap stabil setelah tepi jam. | Waktu (ns) |

| Keterlambatan Propagasi | Waktu dari perubahan input hingga perubahan output. | Waktu (ns) |

| Clock-to-Q | Waktu dari tepi clock hingga perubahan output. | Waktu (ns) |

| Jitter | Variasi dalam waktu tepi sinyal. | Waktu (ps/ns) |

Waktu Setup dan Waktu Hold

Ini adalah batasan paling kritis untuk sistem sinkron.

- Pelanggaran Waktu Setup: Jika data berubah terlalu dekat dengan tepi clock, sistem mungkin tidak menangkap nilai yang benar.

- Pelanggaran Waktu Hold: Jika data berubah terlalu cepat setelah tepi clock, sistem mungkin kehilangan nilai tersebut.

- Notasi: Biasanya ditampilkan sebagai jendela waktu di sekitar tepi clock di mana jalur data tidak boleh berubah.

Keterlambatan Propagasi

Keterlambatan ini memengaruhi frekuensi maksimum sistem.

- Tinggi ke Rendah:Waktu yang dibutuhkan sinyal untuk berpindah dari Tinggi ke Rendah.

- Rendah ke Tinggi:Waktu yang dibutuhkan sinyal untuk berpindah dari Rendah ke Tinggi.

- Notasi: Sering ditampilkan sebagai jarak horizontal antara bentuk gelombang input dan output.

🛠️ Sinyal Kendali dan Status Aktif

Sinyal kendali mengelola aliran data. Notasinya harus jelas menunjukkan kapan sinyal tersebut aktif.

| Jenis Sinyal | Status Aktif | Contoh Notasi |

|---|---|---|

| Reset | Aktif Rendah | Reset# atau Reset_bar |

| Aktifkan | Aktif Tinggi | Aktifkan |

| Interupsi | Aktif Tinggi atau Rendah | IRQ atau IRQ_bar |

| Pemilihan Chip | Aktif Rendah | CS# |

Sinyal Reset

Sinyal reset menginisialisasi sistem. Mereka dapat asinkron atau sinkron.

- Reset Asinkron:Berlaku segera, terlepas dari jam. Notasi menunjukkan sinyal reset menjadi aktif kapan saja.

- Reset Sinkron:Berlaku hanya pada tepi jam. Notasi menunjukkan sinyal reset aktif sebelum tepi jam.

Sinyal Aktifasi

Sinyal aktifasi memungkinkan atau memblokir operasi.

- Aktifasi Tinggi:Operasi terjadi ketika sinyal berada pada tinggi.

- Aktifasi Rendah:Operasi terjadi ketika sinyal berada pada rendah.

📖 Membaca dan Menganalisis Gelombang

Membaca diagram waktu membutuhkan pendekatan sistematis. Insinyur harus mengikuti langkah-langkah tertentu untuk menghindari kesalahan interpretasi.

Analisis Langkah demi Langkah

- Identifikasi Jam:Temukan referensi waktu utama. Semua peristiwa sinkron terkait dengan ini.

- Lacak Aliran Data: Ikuti jalur data dari sumber ke tujuan.

- Periksa Jendela Waktu:Verifikasi waktu setup dan hold terhadap tepi clock.

- Cari Anomali:Identifikasi glitch, loncatan, atau transisi yang tidak diharapkan.

- Verifikasi Tingkat Logika:Pastikan status aktif sesuai dengan spesifikasi komponen.

Kesalahan Pemahaman Umum

- Mengasumsikan Perubahan Instan:Sinyal nyata memiliki waktu naik dan turun. Mengasumsikan tepi vertikal dapat menyembunyikan pelanggaran waktu.

- Mengabaikan Sinyal Asinkron:Sinyal kontrol yang tidak dikunci dapat muncul kapan saja dan harus diperiksa secara independen.

- Salah Memahami Status Aktif:Membingungkan Active High dengan Active Low merupakan sumber umum kesalahan desain.

🚀 Pertimbangan Waktu Lanjutan

Ketika sistem menjadi lebih cepat, analisis waktu menjadi lebih kompleks. Notasi lanjutan menangani tantangan ini.

Metastabilitas

Ketika suatu sinyal berubah selama jendela setup atau hold, output dapat memasuki keadaan metastabil.

- Definisi: Sinyal beristirahat pada tingkat tegangan menengah.

- Notasi: Sering ditampilkan sebagai tanda tanya atau daerah berbayang antara High dan Low.

- Resolusi: Sinyal akhirnya beresolusi menjadi High atau Low, tetapi waktu yang dibutuhkan tidak dapat diprediksi.

Skew Sinkronisasi

Jalur yang berbeda mungkin membutuhkan waktu yang berbeda untuk mencapai tujuan.

- Skew Clock: Sinyal clock tiba di komponen yang berbeda pada waktu yang berbeda.

- Skew Data: Sinyal data tiba di tujuan yang berbeda pada waktu yang berbeda.

- Notasi: Ditampilkan sebagai pergeseran horizontal antara waktu kedatangan yang diharapkan dan yang sebenarnya.

Jitter

Jitter adalah penyimpangan tepi sinyal dari posisi idealnya.

- Jitter Siklus-ke-Siklus: Variasi antara satu siklus jam dan siklus berikutnya.

- Jitter Periode: Variasi dalam durasi total siklus jam.

- Notasi: Sering ditampilkan sebagai area yang diarsir di sekitar posisi tepi ideal.

📝 Praktik Terbaik untuk Dokumentasi

Membuat diagram waktu yang jelas memastikan bahwa orang lain dapat memahami desain Anda. Menuruti praktik terbaik mengurangi ambiguitas.

- Penamaan Konsisten: Gunakan nama yang jelas dan unik untuk semua sinyal. Hindari nama umum seperti Signal1 atau Signal2.

- Simbol Standar: Gunakan notasi standar untuk tepi, tingkat, dan penundaan untuk memastikan kompatibilitas industri.

- Skala Waktu yang Jelas: Beri label sumbu waktu secara eksplisit dengan satuan (ns, µs, ms).

- Kelompokkan Sinyal yang Terkait: Kelompokkan sinyal yang termasuk dalam protokol atau subsistem yang sama bersama-sama.

- Soroti Waktu Kritis: Gunakan garis tebal atau warna untuk menyoroti jendela setup dan hold.

- Sediakan Legenda: Sertakan kunci untuk simbol atau singkatan khusus yang digunakan dalam diagram.

🔚 Ringkasan Poin-Poin Utama

Notasi diagram waktu adalah keterampilan dasar bagi siapa saja yang bekerja dalam desain digital. Dengan memahami komponen utama, tingkat sinyal, dan parameter waktu, insinyur dapat memastikan kinerja sistem yang kuat. Notasi yang tepat menghilangkan ambiguitas dan mencegah kesalahan desain yang mahal. Ingatlah untuk fokus pada waktu setup dan hold, definisikan secara jelas status aktif, dan pertimbangkan karakteristik sinyal dunia nyata seperti penundaan propagasi dan jitter. Mengikuti panduan ini akan menghasilkan dokumentasi yang jelas dan efektif.

Ketika membuat atau meninjau diagram ini, selalu verifikasi tingkat logika terhadap spesifikasi perangkat keras. Pastikan sumbu waktu mencerminkan frekuensi operasi aktual sistem. Akhirnya, pertahankan konsistensi dalam gaya notasi Anda di seluruh dokumentasi untuk memudahkan kolaborasi. Dengan latihan, membaca dan membuat diagram ini akan menjadi bagian alami dari alur kerja desain.

Catatan Akhir tentang Implementasi

Meskipun panduan ini membahas aspek teoritis dan notasi, implementasi praktis membutuhkan perhatian terhadap lapisan fisik. Integritas sinyal, margin kebisingan, dan pengiriman daya semua memengaruhi perilaku waktu. Selalu silangkan diagram waktu dengan data lembaran teknis dan hasil simulasi untuk memvalidasi desain. Pembelajaran berkelanjutan dan kepatuhan terhadap standar industri akan menjaga desain Anda tetap andal dan efisien.