Di dunia yang rumit dari rekayasa sistem tertanam, presisi bukan sekadar pilihan; itu adalah keharusan. Diagram waktu berfungsi sebagai gambaran visual untuk memahami bagaimana sinyal berinteraksi seiring waktu. Representasi grafis ini memetakan tingkat tegangan, siklus jam, dan transisi data terhadap sumbu waktu. Bagi insinyur yang merancang mikrokontroler, sensor, atau antarmuka komunikasi, menguasai pembacaan dan pembuatan diagram ini sangat penting untuk menjamin keandalan sistem.

Tanpa pandangan yang jelas mengenai hubungan temporal, komponen perangkat keras dapat gagal berkomunikasi, yang menyebabkan kerusakan data atau kegagalan sistem. Panduan ini mengeksplorasi aplikasi praktis diagram waktu di berbagai bidang dalam pengembangan sistem tertanam, memberikan wawasan mendalam mengenai manfaatnya tanpa bergantung pada alat perangkat lunak tertentu.

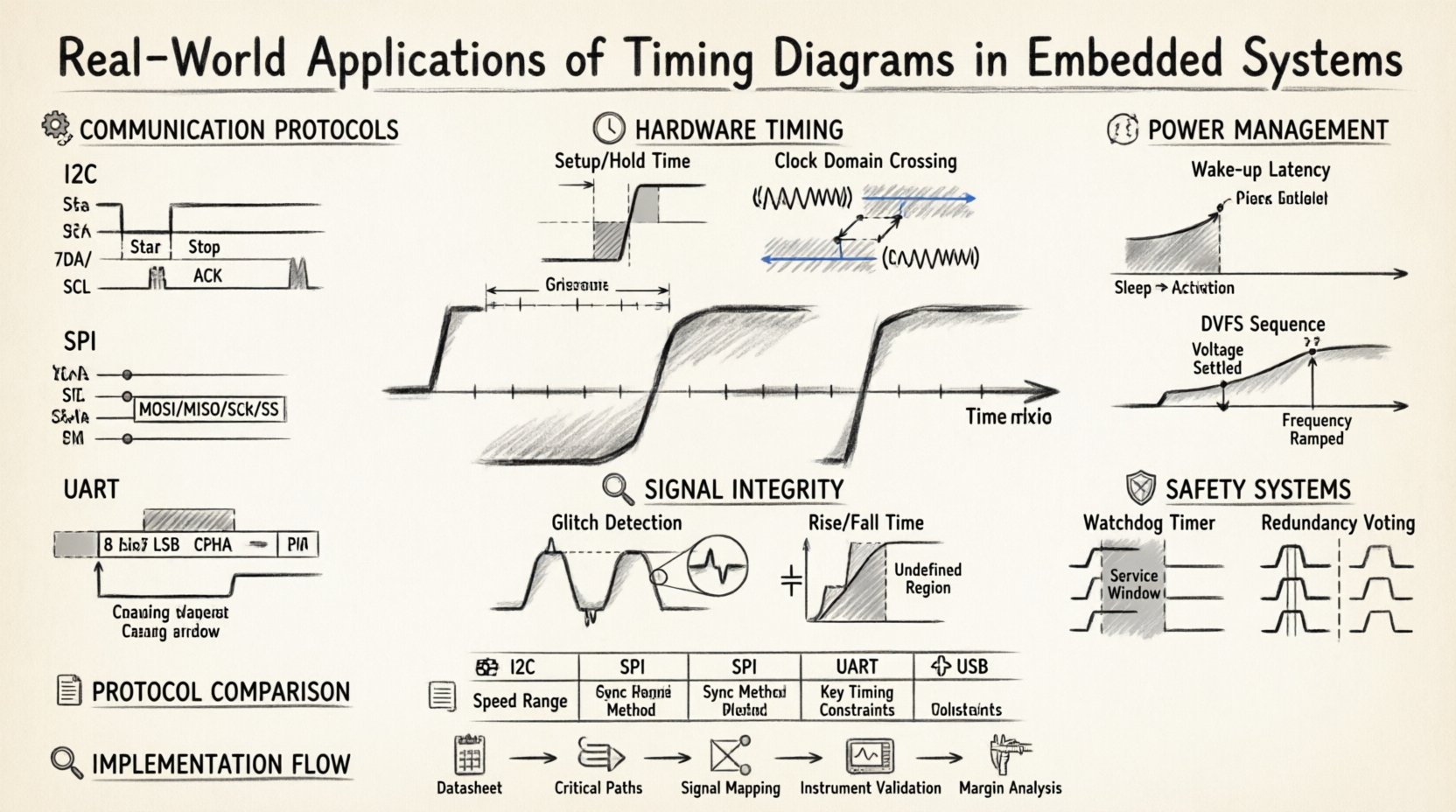

🔌 Analisis Protokol Komunikasi

Komunikasi serial adalah tulang punggung sistem tertanam modern. Data jarang tetap berada dalam satu chip; ia berpindah antara prosesor, memori, dan perangkat peripheral. Diagram waktu sangat penting untuk mendefinisikan dan memverifikasi interaksi ini.

Sirkuit Terpadu Antar (I2C)

Protokol I2C menggunakan antarmuka dua kabel: Data Serial (SDA) dan Jam Serial (SCL). Diagram waktu untuk I2C mengungkapkan urutan khusus yang diperlukan untuk transmisi data.

- Kondisi Mulai: Jalur SDA berpindah dari tinggi ke rendah sementara jalur SCL tetap tinggi. Ini menandakan bus untuk memulai transaksi.

- Kerangka Alamat: Byte pertama yang dikirim berisi alamat 7-bit perangkat tujuan ditambah bit baca/tulis.

- Konfirmasi: Penerima menarik jalur SDA ke rendah selama pulsa jam kesembilan untuk mengonfirmasi penerimaan.

- Kondisi Berhenti: Jalur SDA berpindah dari rendah ke tinggi sementara SCL tinggi, melepaskan bus.

Insinyur menggunakan diagram ini untuk mendeteksi masalah seperti peregangan jam. Jika perangkat slave tidak dapat memproses data cukup cepat, ia menahan jalur SCL tetap rendah. Diagram waktu menunjukkan perpanjangan ini, memungkinkan desainer menyesuaikan loop pemrosesan atau ukuran buffer.

Antarmuka Periferal Serial (SPI)

SPI adalah protokol sinkron yang sering digunakan untuk komunikasi berkecepatan tinggi. Ini melibatkan empat jalur: Master Keluar Slave Masuk (MOSI), Master Masuk Slave Keluar (MISO), Jam Serial (SCK), dan Pemilih Slave (SS).

- Polaritas Jam (CPOL): Menentukan keadaan idle jalur jam. Apakah tinggi atau rendah sebelum data dimulai?

- Fasa Jam (CPHA): Menentukan kapan data diambil. Apakah pada tepi jam pertama atau kedua?

- Waktu Pemilihan Chip: Jalur SS harus tetap rendah selama seluruh durasi transaksi. Jika terjadi gangguan ke tinggi, transaksi dibatalkan.

Memahami fase-fase ini sangat penting. Ketidaksesuaian dalam CPOL atau CPHA antara master dan slave menghasilkan data yang tidak valid. Diagram waktu memvisualisasikan tepi-tepi ini, membuatnya mudah untuk mengidentifikasi ketidaksesuaian saat melakukan pengaktifan perangkat keras.

Penerima/Pengirim Asinkron Universal (UART)

Berbeda dengan SPI dan I2C, UART tidak menggunakan jalur jam. Sinkronisasi bergantung pada tingkat baud yang disepakati. Diagram waktu di sini berfokus pada durasi bit dan bingkai.

- Bit Mulai: Pulsa rendah menunjukkan awal dari satu byte.

- Bit Data: Biasanya 8 bit, dikirimkan dari Bit Paling Tidak Signifikan (LSB) terlebih dahulu.

- Bit Berhenti:Pulsa tinggi menandakan akhir dari satu byte.

Diagram waktu membantu insinyur menghitung jendela toleransi. Jika jam dari dua perangkat berbeda terlalu jauh, titik pengambilan sampel bergeser, menyebabkan kesalahan. Diagram ini menggambarkan jendela pengambilan sampel, biasanya berada di tengah waktu bit.

⏱️ Sinkronisasi Perangkat Keras dan Waktu Persiapan

Di luar komunikasi, diagram waktu sangat diperlukan untuk memahami bagaimana gerbang logika dan flip-flop berinteraksi. Logika digital bergantung pada batasan waktu yang tepat agar berfungsi dengan benar.

Waktu Persiapan dan Waktu Tahan

Ketika data memasuki register atau flip-flop, harus memenuhi persyaratan waktu tertentu terhadap tepi jam.

- Waktu Persiapan:Durasi minimum data harus tetap stabilsebelumtepi jam tiba.

- Waktu Tahan:Durasi minimum data harus tetap stabilsetelahtepi jam tiba.

Jika suatu sinyal melanggar waktu persiapan, register mungkin menangkap nilai yang salah. Jika melanggar waktu tahan, metastabilitas dapat terjadi. Diagram waktu menggambarkan sinyal data relatif terhadap tepi jam, menyoroti zona terlarang di mana perubahan data tidak diperbolehkan.

Penyeberangan Domain Jam (CDC)

Sistem yang kompleks sering menjalankan bagian logika yang berbeda pada frekuensi jam yang berbeda. Memindahkan data dari domain jam cepat ke lambat, atau sebaliknya, membawa risiko.

- Sinkronisasi:Menggunakan rangkaian flip-flop untuk memastikan sinyal stabil sebelum digunakan.

- Penyambungan tangan:Menggunakan sinyal permintaan dan pengakuan untuk mengoordinasikan transfer data tanpa jam bersama.

Diagram waktu untuk CDC menunjukkan urutan penyambungan tangan. Ini memastikan data valid sebelum domain penerima mengakui adanya data. Ini mencegah kehilangan data dalam transfer asinkron.

🔍 Debugging dan Integritas Sinyal

Ketika sistem tertanam berperilaku tidak sesuai harapan, diagram waktu sering menjadi tempat pertama yang dilihat insinyur. Mereka memberikan catatan historis perilaku sinyal yang tidak dapat ditangkap oleh pengujian statis.

Mengidentifikasi Gangguan

Gangguan adalah pulsa singkat yang tidak diinginkan pada jalur sinyal. Dapat berlangsung hanya beberapa nanodetik tetapi dapat memicu perubahan keadaan pada flip-flop.

- Kondisi Balapan:Terjadi ketika urutan kejadian penting, dan waktu terlalu ketat.

- Keterlambatan Propagasi:Sinyal membutuhkan waktu untuk menempuh jalur melalui gerbang logika. Diagram waktu menunjukkan keterlambatan ini dengan jelas.

Dengan mengimpitkan diagram waktu yang diharapkan dengan sinyal aktual yang tercatat, insinyur dapat menentukan secara tepat di mana terjadi penyimpangan. Hal ini memungkinkan perbaikan yang terfokus pada perangkat lunak atau desain perangkat keras.

Margin Kebisingan dan Waktu Naik/Turun

Sinyal dunia nyata bukan gelombang persegi yang sempurna. Mereka memiliki waktu naik dan turun karena kapasitansi dan induktansi pada jalur sirkuit.

- Waktu Naik:Waktu yang dibutuhkan oleh sinyal untuk berpindah dari rendah ke tinggi.

- Waktu Turun:Waktu yang dibutuhkan oleh sinyal untuk berpindah dari tinggi ke rendah.

Jika transisi ini terlalu lambat, sinyal mungkin menghabiskan terlalu banyak waktu di wilayah tegangan yang tidak terdefinisi antara logika 0 dan logika 1. Hal ini dapat menyebabkan beberapa tepi jam dipicu atau terjadi kesalahan logika. Diagram waktu membantu mengukur kemiringan ini untuk memastikan memenuhi spesifikasi chip penerima.

💤 Manajemen Daya dan Status Daya Rendah

Efisiensi energi merupakan perhatian utama dalam perangkat bawaan yang menggunakan baterai. Diagram waktu berperan dalam mengoptimalkan konsumsi daya.

Latensi Bangun Kembali

Ketika perangkat memasuki mode tidur, jam akan dihentikan untuk menghemat daya. Bangun kembali memerlukan pemulihan jam dan menstabilkan tegangan.

- Waktu Transisi:Waktu yang dibutuhkan untuk berpindah dari mode tidur ke status aktif.

- Latensi:Keterlambatan antara kejadian bangun kembali dan prosesor menjalankan kode.

Diagram waktu urutan hidup menunjukkan keterlambatan antara sinyal pemicu dan jam sistem menjadi stabil. Informasi ini sangat penting untuk aplikasi waktu nyata di mana keterlambatan beberapa milidetik menjadi penting.

Skalabilitas Tegangan dan Frekuensi Dinamis (DVFS)

Sistem dapat menyesuaikan tegangan dan frekuensi berdasarkan beban kerja. Diagram waktu membantu memverifikasi transisi antara status kinerja yang berbeda.

- Kemiringan Frekuensi:Apakah jam berubah secara halus atau tiba-tiba?

- Penetapan Tegangan:Apakah tegangan stabil sebelum frekuensi baru diterapkan?

Penyusunan urutan yang salah selama DVFS dapat menyebabkan brownout atau kesalahan logika. Diagram waktu menyediakan verifikasi urutan yang diperlukan untuk memastikan transisi yang aman.

🛡️ Sistem Kritis Keselamatan

Dalam aplikasi otomotif, medis, dan industri, keselamatan sangat penting. Diagram waktu digunakan untuk memverifikasi bahwa mekanisme keselamatan berfungsi dalam batas waktu yang diperlukan.

Penjaga Waktu (Watchdog Timers)

Penjaga waktu akan mereset sistem jika perangkat lunak macet. Diagram waktu menentukan periode waktu habis (timeout).

- Periode Waktu Habis: Waktu maksimum yang diizinkan antara reset.

- Jendela Layanan: Waktu yang dimiliki perangkat lunak untuk mereset timer.

Jika jendela layanan terlalu panjang, penjaga waktu (watchdog) bisa aktif secara tidak perlu. Jika terlalu pendek, interupsi lambat bisa menyebabkan reset yang salah. Diagram ini memastikan waktu sesuai dengan persyaratan standar keselamatan.

Redundansi dan Pemungutan Suara

Beberapa sistem menggunakan beberapa prosesor untuk memilih output yang benar. Diagram waktu memastikan semua prosesor mencapai tahap pemungutan suara secara bersamaan.

- Sinkronisasi: Semua saluran harus menyelaraskan data mereka.

- Waktu Habis: Jika satu saluran terlambat, sistem harus mendeteksi ketidaksesuaian tersebut.

Ini sangat penting dalam sistem kontrol rem atau kemudi di mana keterlambatan bisa berbahaya. Diagram waktu memetakan latensi setiap saluran untuk memastikan logika pemungutan suara bekerja dengan benar.

📋 Gambaran Umum Perbandingan Protokol

Tabel berikut merangkum karakteristik waktu kunci dari antarmuka bawaan umum untuk membantu dalam pemilihan dan desain.

| Protokol | Kisaran Kecepatan | Metode Sinkronisasi | Kasus Penggunaan Umum | Kendala Waktu Kunci |

|---|---|---|---|---|

| I2C | 100 kHz hingga 3,4 MHz | Jam Bersama | Sensor, EEPROM | Pemanjangan Jam |

| SPI | 1 MHz hingga 50 MHz+ | Jam Utama | Memori Flash, Tampilan | Persiapan Pemilihan Chip |

| UART | 9600 hingga 921600 bps | Asinkron | Debug, GPS, Bluetooth | Toleransi Laju Baud |

| USB | 1,5 Mbps hingga 20 Gbps | Berdasarkan Paket | Periferal, Penyimpanan | Waktu Token/Tangan Pertama |

🛠️ Langkah-Langkah Implementasi Nyata

Membuat diagram waktu melibatkan pendekatan sistematis. Dimulai dengan memahami spesifikasi dan berakhir dengan verifikasi.

- Tinjau Data Lembaran:Setiap komponen memiliki bagian waktu. Cari tabel karakteristik AC.

- Identifikasi Jalur Kritis: Tentukan sinyal mana yang menentukan kecepatan maksimum sistem.

- Peta Ketergantungan: Gambarkan hubungan antar sinyal. Yang mana yang memicu yang lain?

- Validasi dengan Alat Ukur: Gunakan analis logika atau osiloskop untuk menangkap gelombang nyata.

- Analisis Margin: Pastikan ada cukup waktu antar sinyal untuk mempertimbangkan variasi suhu dan tegangan.

Dokumentasi sangat penting. Diagram waktu yang dilengkapi keterangan menjadi acuan untuk pemeliharaan di masa depan. Ini menjelaskan mengapa tertentu penundaan ditambahkan atau mengapa resistor pull-up tertentu dipilih.

🚀 Pertimbangan Lanjutan

Ketika sistem menjadi lebih kompleks, analisis waktu membutuhkan perhatian yang lebih mendalam.

Jitter dan Kebisingan Fasa

Jam tidak sepenuhnya stabil. Jitter adalah penyimpangan tepi jam dari posisi idealnya. Diagram waktu menunjukkan variasi penempatan tepi selama beberapa siklus.

- Jitter Periode:Variasi dalam periode jam.

- Jitter Siklus ke Siklus:Variasi dari satu siklus ke siklus berikutnya.

Jitter tinggi mengurangi margin setup dan hold. Pada antarmuka berkecepatan tinggi seperti memori DDR, hal ini dapat menyebabkan kesalahan baca/tulis. Diagram waktu membantu mengukur jitter ini agar tetap berada dalam batas yang dapat diterima.

Efek Termal

Suhu memengaruhi kecepatan transistor. Saat chip memanas, sinyal menjadi lebih lambat.

- Analisis Kasus Terburuk:Desain untuk suhu operasi maksimum.

- Pembatasan Termal:Pastikan sistem tidak melampaui batas termal aman selama operasi berkecepatan tinggi.

Diagram waktu yang dibuat pada suhu ruangan mungkin tidak berlaku pada 85°C. Insinyur harus mempertimbangkan pergeseran termal ini untuk memastikan ketahanan sistem.

📝 Pikiran Akhir

Diagram waktu lebih dari sekadar gambar; mereka adalah bahasa sinkronisasi. Mereka menghubungkan celah antara logika teoretis dan kenyataan fisik. Dalam sistem tertanam, di mana perangkat keras dan perangkat lunak saling terkait, pemahaman yang jelas tentang waktu sinyal mencegah perancangan ulang yang mahal dan menjamin keandalan.

Apakah Anda sedang mendiagnosis protokol komunikasi, mengoptimalkan konsumsi daya, atau menjamin keselamatan dalam sistem kritis, diagram ini memberikan kejelasan yang dibutuhkan untuk membuat keputusan yang tepat. Dengan fokus pada waktu setup, keterlambatan propagasi, dan integritas sinyal, insinyur dapat membangun sistem yang berkinerja konsisten dalam kondisi dunia nyata.

Investasi dalam memahami hubungan waktu membawa hasil dalam stabilitas dan kinerja. Seiring kemajuan teknologi, prinsip-prinsipnya tetap sama. Waktu adalah hal yang konstan, dan menguasai pengukurannya adalah kunci desain tertanam yang sukses.