No mundo da eletrônica digital e da engenharia de computadores, os sinais não existem em um vácuo. Eles viajam por trilhas, através de portas e até processadores com restrições temporais específicas. Para entender como um sistema funciona, os engenheiros precisam visualizar como esses sinais mudam ao longo do tempo. Essa visualização é alcançada por meio de um diagrama de tempo. Para um iniciante, esses gráficos podem parecer hieróglifos complexos, mas na verdade são a ferramenta mais fundamental para depuração e design de lógica digital.

Este guia oferece uma análise detalhada dos diagramas de tempo. Exploraremos a anatomia de um sinal, os parâmetros críticos que definem a confiabilidade e os erros comuns que levam à falha do sistema. Seja você estudando para uma prova ou projetando seu primeiro circuito de microcontrolador, entender esses diagramas é essencial.

🧠 O que é um Diagrama de Tempo?

Um diagrama de tempo é uma representação gráfica do estado de sinais digitais ao longo do tempo. Diferentemente de um esquemático de circuito, que mostrao queestá conectado ao que, um diagrama de tempo mostraquandoas coisas acontecem. Ele representa níveis de tensão em relação a um eixo do tempo, permitindo que engenheiros vejam a sequência de eventos.

Esses diagramas são indispensáveis por várias razões:

- Depuração: Revelam condições de corrida em que os sinais chegam fora de ordem.

- Verificação: Confirmam que um circuito atende às especificações de velocidade exigidas.

- Documentação: Servem como referência sobre como diferentes chips se comunicam.

- Projeto: Ajudam a determinar a frequência máxima do clock que um sistema pode suportar.

Quando você olha para um diagrama de tempo, está olhando para uma fotografia do comportamento físico dos elétrons se movendo por um sistema. Ele captura a realidade da latência, propagação e sincronização.

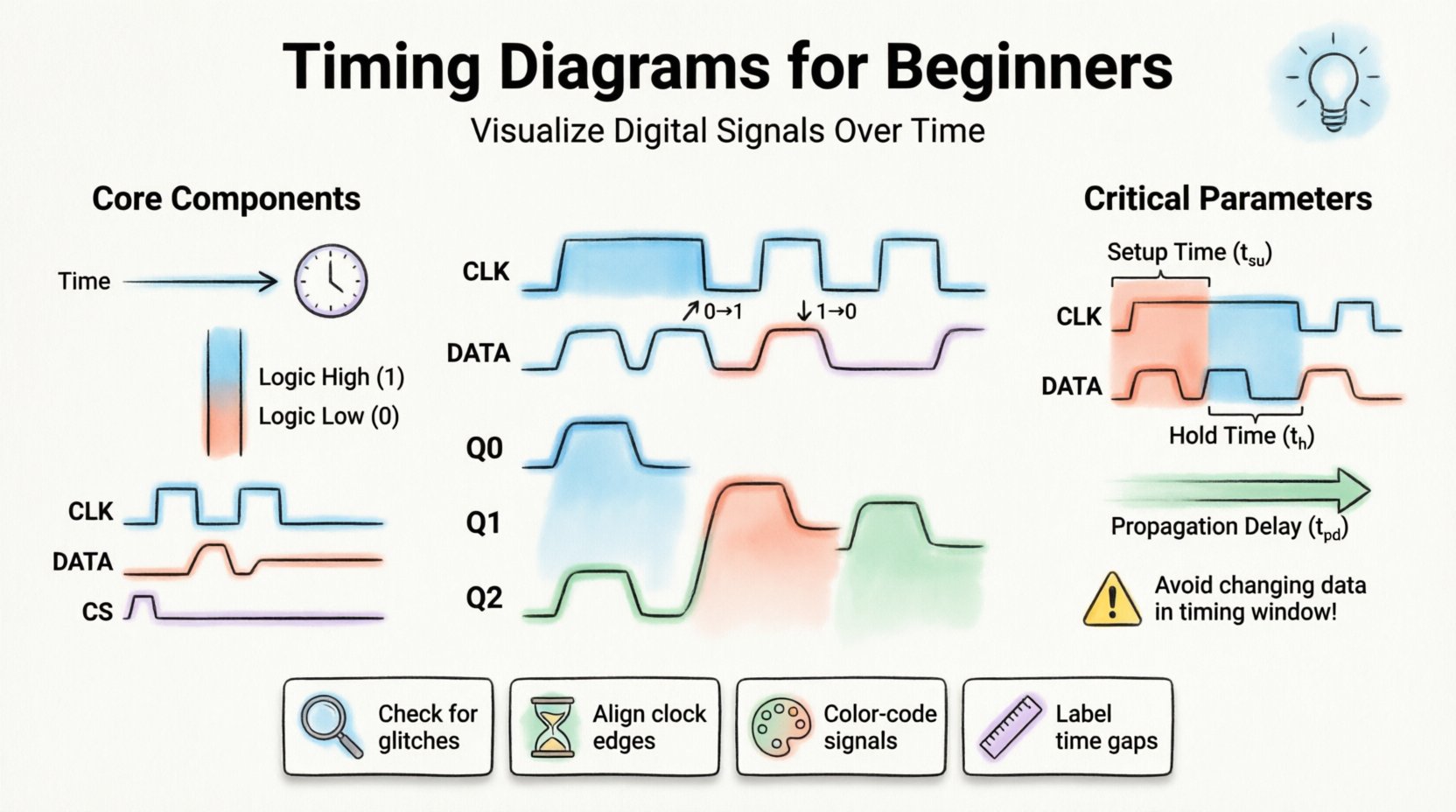

📊 Componentes Principais de um Diagrama de Tempo

Antes de analisar formas de onda complexas, você precisa entender os blocos de construção. Todo diagrama de tempo consiste em alguns elementos fundamentais.

1. O Eixo do Tempo

O eixo horizontal representa o tempo. Ele flui da esquerda para a direita. No design digital, esse eixo é frequentemente dividido em ciclos de clock, marcado por linhas verticais de grade. A escala pode variar de nanossegundos (ns) para processadores de alta velocidade até milissegundos (ms) para lógica de controle mais lenta.

2. O Eixo do Nível de Tensão

O eixo vertical representa o estado lógico do sinal. Nas famílias de lógica padrão, isso geralmente é binário:

- Lógica Alta (1):Geralmente representado como VCC ou 5V.

- Lógica Baixa (0):Freqüentemente representado como Terra ou 0V.

- High-Z (Alta Impedância):Um estado em que o pino está efetivamente desconectado, comum em sistemas de barramento.

3. Linhas de Sinal

Cada linha horizontal representa um fio específico ou nome de sinal. Essas linhas são rotuladas claramente (por exemplo, CLK, DATA_IN, CS) para identificar qual parte do circuito está sendo monitorada.

🔄 Lendo Transições de Sinal

O movimento da linha de sinal para cima e para baixo é onde os dados estão armazenados. Compreender a direção desses movimentos é essencial.

⬆️ Aresta de Subida

Uma aresta de subida ocorre quando um sinal passa de Baixo para Alto. Na lógica binária, isso geralmente é o ponto de gatilho para muitas operações. Representa uma mudança de 0 para 1.

⬇️ Aresta de Queda

Uma aresta de queda ocorre quando um sinal passa de Alto para Baixo. Isso representa uma mudança de 1 para 0.

⚡ Gatilhamento por Aresta

Muitos componentes digitais, como flip-flops, respondem apenas a essas arestas e não ao estado estável. Um flip-flop pode capturar dados apenas na aresta de subidade um sinal de clock. Se você perder a aresta, os dados são perdidos.

| Transição | Direção | Mudança Binária | Tipo Comum de Gatilho |

|---|---|---|---|

| Aresta de Subida | Baixo ➔ Alto | 0 ➔ 1 | Gatilhado por Aresta Positiva |

| Aresta de Queda | Alto ➔ Baixo | 1 ➔ 0 | Gatilhado por Aresta Negativa |

| Nível Alto | Estável em Alto | Estável em 1 | Sensível ao Nível |

| Nível Baixo | Baixo Estável | Estável 0 | Sensível ao Nível |

⏳ Parâmetros Críticos de Temporização

Diagramas de temporização não são apenas imagens; contêm medições. O espaço entre as mudanças de sinal é onde a confiabilidade é determinada. Três parâmetros específicos dominam a análise de temporização digital.

1. Atraso de Propagação (tpd)

Os sinais não viajam instantaneamente. Quando uma entrada muda, leva um tempo finito para que a saída reflita essa mudança. Esse é o atraso de propagação. Ele é causado pela resistência física e capacitância dos materiais.

- Definição: A diferença de tempo entre a mudança de entrada e a mudança de saída.

- Impacto: Em uma cadeia de portas lógicas, os atrasos se acumulam. Se o atraso for muito longo, o sinal pode chegar após o início do próximo ciclo de clock, causando erros.

2. Tempo de Preparação (tsu)

O tempo de preparação é a exigência para que um sinal de dados permaneça estável antes a chegada de uma borda de clock. Se os dados mudarem muito perto da borda de clock, o circuito receptor não poderá capturá-los corretamente.

- Regra: Os dados devem ser válidos durante uma duração específica antes do disparo do clock.

- Visual: Em um diagrama, esse é o espaço entre a estabilização da linha de dados e a borda de clock.

3. Tempo de Manutenção (th)

O tempo de manutenção é a exigência para que o sinal de dados permaneça estável após quando chega a borda do clock. Se os dados mudarem imediatamente após a borda do clock, o circuito pode não capturar o valor correto.

- Regra:Os dados devem permanecer inalterados durante uma duração específica após o disparo do clock.

- Visual:Em um diagrama, esse é o espaço entre a borda do clock e a próxima transição de dados.

⚠️ A Janela de Tempo

A combinação do tempo de setup e do tempo de hold cria uma janela válida para capturar dados. Se o seu diagrama de tempo mostrar dados mudando dentro dessa janela, o sistema está em risco de falha.

⚡ Sistemas Síncronos vs. Assíncronos

Os diagramas de tempo diferem significativamente dependendo da arquitetura do sistema.

Sistemas Síncronos

No design síncrono, todas as operações são coordenadas por um sinal de clock global. A mudança de estado ocorre em cada borda desse clock. Os diagramas de tempo para esses sistemas apresentam uma aparência muito regular.

- Características:Previsíveis, mais fáceis de projetar, limitados pela velocidade do clock.

- Aspecto do Diagrama:As linhas verticais da grade se alinham perfeitamente com todas as mudanças de sinal.

Sistemas Assíncronos

No design assíncrono, não há um clock global. Os sinais mudam sempre que as entradas mudam. Isso oferece maior potencial de velocidade, mas torna a análise de tempo muito mais difícil.

- Características:Resposta mais rápida às entradas, análise de riscos complexa.

- Aspecto do Diagrama:As transições de sinal ocorrem em intervalos irregulares. Você deve medir os intervalos exatos de tempo entre os eventos.

📝 Como Desenhar um Diagrama de Tempo

Criar um diagrama de tempo é um processo sistemático. Siga estas etapas para documentar um circuito ou verificar um projeto.

- Identifique os Sinais: Liste todas as entradas, saídas e linhas de controle internas. Rotule-as claramente.

- Estabeleça a Base de Tempo: Decida sobre a escala de tempo. Para circuitos lógicos, os ciclos de clock geralmente são a unidade padrão.

- Desenhe o Clock: Desenhe sempre o sinal de clock primeiro. É a referência para todos os outros eventos.

- Mapeie as Entradas: Desenhe as formas de onda de entrada com base na operação lógica ou sequência de teste.

- Calcule os Atrasos:Desloque os sinais de saída para a direita com base no atraso de propagação das portas envolvidas.

- Verifique as Restrições:Verifique se os tempos de setup e hold são atendidos para cada flip-flop.

- Revise as Transições:Garanta que não haja glitches. Um glitch é um pulso breve e indesejado que pode acionar a lógica incorretamente.

🔄 Exemplo do Mundo Real: Um Contador Simples

Para visualizar como esses conceitos funcionam juntos, considere um contador binário simples de 3 bits. Este circuito incrementa seu valor toda vez que o sinal de clock pulsa.

Imagine três linhas de saída: Q0, Q1 e Q2. Q0 muda de estado em cada ciclo de clock. Q1 muda de estado toda vez que Q0 completa um ciclo completo. Q2 muda de estado toda vez que Q1 completa um ciclo completo.

Análise Passo a Passo

- Clock (CLK): Uma onda quadrada com um ciclo de trabalho de 50%.

- Q0 (bit menos significativo): Muda de estado em cada borda ascendente do clock. A frequência é metade da do clock.

- Q1: Muda de estado em cada borda ascendente de Q0. A frequência é metade de Q0.

- Q2 (bit mais significativo): Muda de estado em cada borda ascendente de Q1. A frequência é metade de Q1.

Ao desenhar isso, você notará um efeito de ondulação. Q0 muda primeiro. Q1 espera Q0 se estabilizar antes de mudar. Q2 espera Q1. Essa acumulação de atrasos é a essência de um contador de ondulação.

| Ciclo de Clock | Q2 | Q1 | Q0 | Valor Decimal |

|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 1 |

| 3 | 0 | 1 | 0 | 2 |

| 4 | 0 | 1 | 1 | 3 |

| 5 | 1 | 0 | 0 | 4 |

⚠️ Armadilhas Comuns para Evitar

Mesmo engenheiros experientes podem cometer erros ao ler diagramas de tempo. Esteja atento a esses erros comuns.

- Ignorando Glitchs:Um pulso breve pode não ser visível se a escala de tempo for muito grande, mas pode acionar uma trava. Verifique sempre a existência de pulsos estreitos.

- Interpretação Incorreta do Ciclo de Trabalho:Supor que um clock é de 50% quando na verdade está enviesado. Isso afeta a janela de tempo.

- Ignorando Estados de Alta Impedância:Em sistemas de barramento, os sinais ficam flutuantes. Um diagrama de tempo deve indicar quando um sinal está sendo conduzido e quando está flutuando.

- Confundindo Setup e Hold:Setup é antes da borda; Hold é depois. Confundir esses conceitos leva a projetos incorretos de circuitos.

- Ignorar a Referência de Terra: Todos os níveis de tensão devem ser medidos em relação à mesma terra. Se as terras forem diferentes, os níveis lógicos serão inválidos.

🛠 Melhores Práticas para Documentação

Ao criar diagramas de temporização para documentação ou depuração, siga estas diretrizes para garantir clareza.

- Use Escala Consistente: Certifique-se de que o eixo do tempo seja linear. Não comprima uma seção e estique outra, a menos que esteja explicitamente marcado.

- Alinhe as Bordas Críticas: Certifique-se de que a borda do clock esteja perfeitamente alinhada com o ponto de amostragem dos dados.

- Rotule os Espaços: Se houver um atraso, rotule-o com o valor específico de tempo (por exemplo, tpd= 5ns).

- Codificação por Cor: Use cores distintas para diferentes tipos de sinal (por exemplo, azul para clock, vermelho para dados, verde para controle).

- Marque os Estados Ativos: Indique claramente se um sinal é ativo alto ou ativo baixo (por exemplo, usando uma barra sobre o nome, como /CS).

🧩 Metastabilidade e Riscos de Temporização

Diagramas de temporização avançados frequentemente revelam um fenômeno chamado metastabilidade. Isso ocorre quando um sinal muda exatamente na janela de setup/hold de um flip-flop. A saída não se estabiliza imediatamente em 0 ou 1; ela permanece em um nível de tensão intermediário.

Embora rara, a metastabilidade pode causar falhas no sistema. Diagramas de temporização ajudam a prever isso ao mostrar a relação entre entradas assíncronas e o clock síncrono. Se um sinal externo mudar muito perto da borda do clock, o diagrama mostrará os dados cruzando o limiar no momento errado.

🔍 Analisando Dados Reais

Quando você analisa um diagrama de temporização gerado por um analisador lógico, as linhas raramente são quadrados perfeitos. Os sinais do mundo real apresentam:

- Tempo de Subida: O tempo necessário para passar do baixo para o alto. Raramente é instantâneo.

- Tempo de Queda: O tempo necessário para passar do alto para o baixo.

- Sobre-sinalização/Insuficiência: Picos de tensão que ultrapassam os níveis de alimentação.

- Jitter: Variações no tempo das bordas do sinal.

Compreender essas imperfeições é vital para o design de alta velocidade. Uma onda quadrada perfeita é uma idealização teórica; os sinais reais são formas de onda analógicas que representam lógica digital.

📚 Resumo dos Principais Pontos Aprendidos

Diagramas de tempo são a linguagem do tempo digital. Eles traduzem a lógica abstrata em realidade física. Ao dominá-los, você adquire a capacidade de:

- Visualizar o fluxo de dados através de um sistema.

- Identificar onde os sinais poderiam entrar em conflito.

- Garantir que os dados sejam capturados de forma confiável.

- Calcular a velocidade máxima de operação de um circuito.

Comece praticando com portas lógicas simples. Desenhe a entrada, calcule o atraso e trace a saída. À medida que avança, passe para barramentos complexos e domínios de clock. Com paciência e prática, ler esses diagramas tornar-se-á algo natural.

🚀 Avançando

Continue explorando os detalhes da integridade de sinal e das redes de distribuição de clock. À medida que os sistemas ficam mais rápidos, as margens de tempo tornam-se menores. A habilidade de ler diagramas de tempo com precisão permanecerá uma competência fundamental para qualquer engenheiro que trabalhe com hardware digital.