No mundo da eletrônica digital e da engenharia de hardware, a comunicação entre componentes depende de uma coordenação precisa. Sem uma compreensão clara de quando os sinais mudam de estado, os sistemas falham. O diagrama de tempo serve como o plano para essa coordenação. Ele visualiza a relação entre os sinais ao longo do tempo, revelando se os dados são válidos, estáveis e prontos para processamento. Este guia aborda as perguntas fundamentais que engenheiros e estudantes enfrentam ao analisar essas ferramentas visuais críticas.

Seja você quem está projetando uma interface de microcontrolador, depurando um protocolo de comunicação ou estudando lógica digital, compreender os aspectos temporais do seu projeto é indispensável. Este artigo explora a anatomia dos diagramas de tempo, explica parâmetros-chave e responde perguntas comuns sobre integridade de sinal e sincronização.

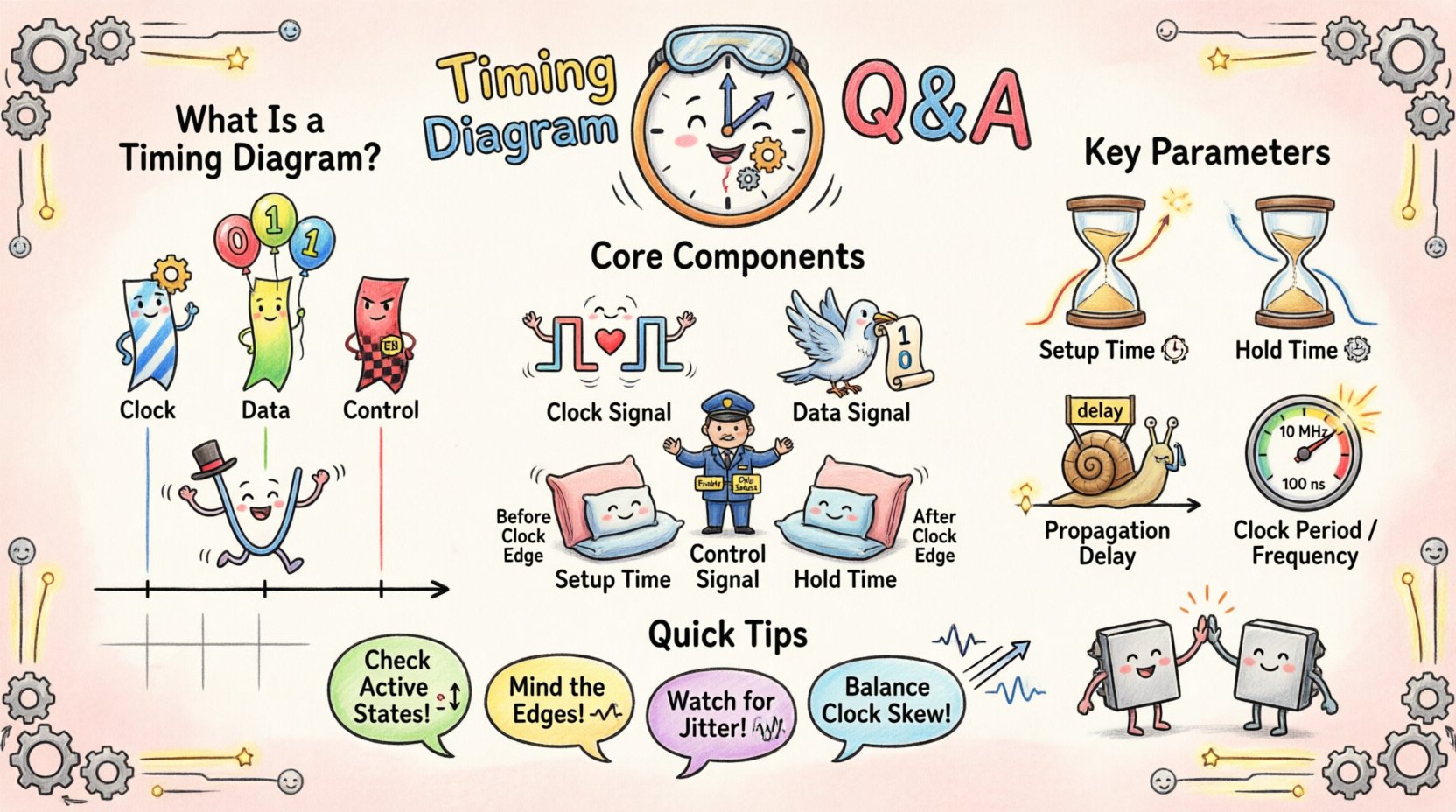

O que exatamente é um diagrama de tempo? 📊

Um diagrama de tempo é uma representação gráfica da sequência de eventos em um sistema. Ele representa os níveis dos sinais em relação a um eixo horizontal do tempo. Diferentemente de um diagrama lógico, que mostra conectividade, um diagrama de tempo mostra o comportamento. Permite verificar se um sinal muda para alto ou baixo antes ou depois de outro sinal. Esse contexto visual é essencial para verificar se o receptor tem tempo suficiente para ler os dados antes da chegada da próxima borda do clock.

Características principais incluem:

- Eixo do Tempo:Normalmente corre horizontalmente da esquerda para a direita.

- Linhas de Sinal:Linhas horizontais que representam fios individuais ou barramentos de dados.

- Níveis Lógicos:Estados Alto (1) e Baixo (0) são representados como platôs de tensão distintos.

- Bordas:Linhas verticais que indicam a transição de um estado para outro.

Componentes Principais de um Diagrama de Tempo 🧩

Para ler esses diagramas de forma eficaz, você deve identificar os elementos padrão que compõem a onda. Cada elemento desempenha um papel específico na sincronização do sistema.

| Componente | Descrição | Indicador Visual |

|---|---|---|

| Sinal de Relógio | Fornece o batimento cardíaco do sistema. Outros sinais são frequentemente amostrados em relação a este. | Padrão de onda quadrada regular |

| Sinal de Dados | Transporta a informação real que está sendo transferida. | Transições irregulares baseadas na entrada |

| Sinal de Controle | Gerencia o fluxo de dados (por exemplo, Habilitar, Seleção de Chip, Escrita). | Pulsos ativos alto ou ativos baixo |

| Tempo de Preparação | A duração durante a qual os dados devem permanecer estáveis antes de uma borda do clock. | Distância horizontal antes da borda |

| Tempo de retenção | A duração em que os dados devem permanecer estáveis após uma borda do sinal de clock. | Distância horizontal após a borda |

Compreendendo os Parâmetros de Tempo-Chave ⚙️

Os parâmetros de tempo definem as restrições dentro das quais um circuito digital opera corretamente. Violá-los frequentemente leva a um comportamento imprevisível. Abaixo estão as definições e implicações das métricas mais críticas.

1. Tempo de preparação ⏳

O tempo de preparação é a quantidade mínima de tempo em que o sinal de dados deve permanecer estável antes da borda de ativação do sinal de clock. Se os dados mudarem muito perto da borda do clock, o flip-flop pode não capturar o valor corretamente. Este é frequentemente o limite mais crítico em projetos de alta velocidade, pois determina a frequência máxima de operação.

2. Tempo de retenção ⏳

O tempo de retenção é a quantidade mínima de tempo em que o sinal de dados deve permanecer estável após a borda de ativação do sinal de clock. Diferentemente do tempo de preparação, o tempo de retenção geralmente é independente da frequência do clock. Ele depende do atraso interno do flip-flop e do atraso de propagação externo da trajetória dos dados.

3. Atraso de propagação ⏳

Este é o tempo necessário para um sinal percorrer do entrada de um componente até sua saída. Ele varia conforme a temperatura, a tensão e as tolerâncias de fabricação. Em um diagrama de tempo, isso aparece como atraso entre uma mudança em um sinal e a mudança resultante em outro.

4. Período e Frequência do Clock ⏳

O período do clock é a duração de um ciclo completo do sinal de clock. A frequência é o inverso do período. Um período mais curto significa uma frequência mais alta, o que permite um processamento mais rápido, mas reduz a janela de estabilidade do sinal.

Perguntas Frequentes ❓

Engenheiros frequentemente enfrentam cenários específicos que causam confusão. Aqui estão respostas detalhadas às perguntas mais urgentes sobre análise de tempo.

Q: O que acontece se o tempo de preparação for violado? 🛑

Quando o requisito de tempo de preparação não é atendido, o flip-flop entra em um estado conhecido como metastabilidade. Neste estado, a saída não se estabiliza imediatamente em um nível lógico alto ou baixo válido. Em vez disso, ela pode oscilar ou permanecer em um nível de tensão intermediário por um tempo imprevisível. Isso pode fazer com que a lógica posterior leia um valor corrompido, levando a erros no sistema ou travamentos. Em casos graves, a metastabilidade pode se propagar por todo o circuito, causando uma falha funcional que é difícil de depurar.

Q: Como devo lidar com o desvio de clock? 🔄

O desvio de clock ocorre quando o sinal de clock chega em componentes diferentes em tempos diferentes. Isso pode acontecer devido a comprimentos de trajeto variáveis ou diferenças de carga. Para gerenciar o desvio:

- Roteamento equilibrado: Certifique-se de que os traçados de clock sejam roteados com comprimentos e larguras semelhantes.

- Bufferização: Use buffers de clock para alimentar múltiplas cargas de forma uniforme.

- Margens de tempo: Projete o sistema com folga suficiente nos tempos de preparação e retenção para absorver pequenas variações de desvio.

Q: Qual é a diferença entre tempo síncrono e assíncrono? ⚖️

Em síncrono sistemas, todas as operações são coordenadas por um único sinal de relógio. Diagramas de tempo para esses sistemas mostram bordas de relógio regulares e repetidas. Em assíncrono sistemas, os sinais acionam ações sem um relógio global. Diagramas de tempo para esses sistemas mostram transições acionadas por eventos, frequentemente com mais variação nos intervalos entre os sinais. Projetos assíncronos são mais difíceis de analisar, mas podem ser mais eficientes em termos de energia em aplicações específicas de baixo consumo.

P: Como o jitter afeta um diagrama de tempo? 📉

O jitter é a variação de curto prazo de um sinal em relação à sua posição ideal no tempo. Em um diagrama de tempo, isso se manifesta como as bordas do sinal de relógio aparecendo ligeiramente antes ou depois do que deveriam. Um jitter excessivo reduz a janela efetiva para capturar dados. Ele reduz efetivamente os margens de setup e hold, aumentando o risco de violações de tempo. Interfaces de alta velocidade exigem controle rigoroso do jitter para manter a integridade dos dados.

P: Posso ler diagramas de tempo sem um relógio? 🕵️

Sim, mas exige uma abordagem diferente. Protocolos assíncronos como I2C ou UART nem sempre usam uma linha de relógio compartilhada. Em vez disso, dependem de taxas de baud pré-definidas ou sinais de handshake. Nesses diagramas, você deve observar as larguras dos pulsos e o tempo entre as transições para inferir a taxa de dados. Por exemplo, no UART, a duração do bit de início define o tempo para os bits de dados subsequentes.

Leitura e Interpretação de Ondas 🔍

Interpretar um diagrama de tempo exige uma abordagem sistemática. Escanear aleatoriamente as linhas frequentemente leva a detalhes perdidos. Siga este processo para uma análise precisa.

- Identifique a Referência: Encontre o sinal de relógio ou o sinal de controle principal. Todos os outros tempos são relativos a este.

- Verifique os Estados Ativos: Determine se os sinais são ativos alto ou ativos baixo. Um pulso baixo pode significar “habilitado”, enquanto um pulso alto significa “desabilitado”. Isso é frequentemente indicado por um símbolo de bolha no nome do pino em esquemáticos.

- Analise a Alinhamento de Borda: Observe com atenção onde as bordas de dados se alinham com as bordas do relógio. Os dados deveriam mudar idealmente quando o relógio estiver estável (por exemplo, na fase baixa) e permanecer estáveis durante a borda ativa.

- Rastreie Dependências: Siga a relação de causa e efeito. Se o sinal A aciona o sinal B, deve haver um atraso claro entre eles correspondente ao atraso de propagação.

- Verifique as Larguras dos Pulsos: Certifique-se de que os pulsos ativos sejam suficientemente largos para que o componente receptor os detecte. Um pulso muito estreito pode ser filtrado como ruído.

Erros Comuns na Interpretação de Diagramas ❌

Mesmo engenheiros experientes podem mal interpretar diagramas se ignorarem detalhes específicos. Evite esses erros comuns.

- Ignorando Níveis Lógicos: Supondo que todos os sinais são ativos alto sem verificação. Sempre verifique o datasheet ou o esquemático.

- Ignorando Atrasos de Propagação: Supondo que os sinais mudam instantaneamente. Componentes do mundo real têm tempos de resposta finitos.

- Lendo incorretamente as Escalas de Tempo: Falhando em notar a unidade de tempo (nanossegundos versus microssegundos). Um sinal que parece estável em um zoom lento pode mostrar falhas em um zoom rápido.

- Ignorando Estados de Energia: Diagramas de tempo frequentemente mudam quando um dispositivo entra no modo de suspensão. Certifique-se de estar olhando para a sequência de tempo ativa.

Estratégias para Análise Precisa 🛠️

Para garantir que sua análise de tempo seja robusta, adote estas estratégias. Esses métodos ajudam a manter a consistência e reduzem a chance de erro.

- Use Linhas de Grade:Alinhe seus cursores ou marcadores com as linhas de grade no diagrama para medir intervalos de tempo com precisão.

- Documente Suposições:Anote a frequência de clock assumida e os níveis lógicos antes de iniciar a análise. Isso evita confusão posteriormente.

- Verificação Cruzada:Compare o diagrama de tempo com a lógica da máquina de estados. Cada transição de estado deve ter um evento de tempo correspondente.

- Simule Variações:Considere cenários piores. O que acontece se a temperatura aumentar e os atrasos aumentarem? E se a tensão cair e a força de condução diminuir?

- Concentre-se nas Rotas Críticas:Identifique o caminho mais longo na sua lógica. Esse caminho determina a velocidade máxima de clock do sistema. Priorize a análise de tempo para essas rotas específicas.

O Impacto das Violações de Tempo ⚠️

Compreender por que o tempo é importante é crucial. Quando ocorre uma violação de tempo, o comportamento físico do circuito muda. A consequência mais comum é a corrupção de dados. Um registrador pode capturar um ‘1’ quando deveria ter capturado um ‘0’. Em protocolos de comunicação, isso resulta em erros de enquadramento ou pacotes perdidos. Em sistemas de controle, pode levar a comandos incorretos para atuadores, potencialmente causando danos físicos ou riscos de segurança.

Além disso, violações de tempo podem causar falhas intermitentes. Um sistema pode funcionar perfeitamente à temperatura ambiente, mas falhar quando esquenta. Isso acontece porque os atrasos de propagação aumentam com a temperatura. Projetar com margens de tempo suficientes leva em conta essas mudanças ambientais.

Melhores Práticas para Diagramas de Tempo 📝

Criar diagramas de tempo claros e precisos é uma habilidade que melhora com a prática. Siga estas diretrizes para produzir diagramas que sejam fáceis de entender para outros.

- Rotule Tudo:Cada linha de sinal deve ter um nome claro. Evite rótulos genéricos como “Sinal 1”.

- Use uma Escala Consistente:Mantenha uma escala de tempo uniforme em todo o diagrama, a menos que precise ampliar um evento específico.

- Destaque Eventos Críticos:Use cores diferentes ou linhas mais grossas para marcar os intervalos de setup e hold.

- Inclua Anotações:Adicione notas de texto para explicar interações complexas ou restrições específicas.

- Verifique com Folhas de Dados:Sempre verifique os parâmetros do seu diagrama com as especificações oficiais dos componentes.

Considerações Avançadas: Domínios de Clock Múltiplos 🌐

Sistemas modernos frequentemente usam múltiplos domínios de clock. Por exemplo, um processador pode operar a 2 GHz enquanto um controlador de memória opera a 400 MHz. Os diagramas de tempo para esses sistemas tornam-se significativamente mais complexos. Você deve levar em conta:

- Amostragem entre Clocks: Como os dados se movem de uma frequência para outra.

- Buffers FIFO: Como sincronizar o fluxo de dados entre relógios assíncronos.

- Sincronização de Reinicialização: Garantindo que todos os domínios sejam reiniciados de forma coordenada para evitar inconsistências de estado.

Ao analisar esses diagramas, procure a lógica de sincronização, como sinais de handshake ou cadeias de sincronização. Esses componentes foram projetados especificamente para pontuar com segurança a lacuna entre diferentes domínios de tempo.

Conclusão: A precisão é essencial 🔑

Diagramas de tempo são mais do que apenas imagens; são a prova matemática de um sistema funcional. Eles definem os limites de confiabilidade e desempenho. Ao compreender os componentes principais, parâmetros e armadilhas potenciais, você pode projetar sistemas que funcionam corretamente em condições do mundo real. A atenção aos tempos de setup, tempos de hold e atrasos de propagação separa um protótipo funcional de um produto pronto para produção. A prática contínua na leitura e criação desses diagramas aprimorará sua intuição técnica e melhorará seus resultados de engenharia.

Lembre-se de que cada borda conta uma história sobre o fluxo de informações. Respeite o tempo que leva para essas informações percorrerem seu caminho, e seus projetos resistirão ao teste do tempo.