Diagramas de temporização são a base do design de sistemas digitais. Eles servem como o contrato visual entre lógica, hardware e software, definindo exatamente quando os sinais devem mudar de estado. No entanto, apesar de sua ubiquidade na engenharia, há uma névoa persistente de mal-entendidos sobre como esses diagramas são criados, interpretados e utilizados. Muitos profissionais os tratam como ilustrações estáticas, em vez de representações dinâmicas do comportamento do sistema.

Este guia tem como objetivo esclarecer os pontos confusos. Analisaremos mitos comuns, exploraremos as realidades técnicas da propagação de sinais e estabeleceremos uma estrutura para criar documentação de temporização precisa. Separando fato da ficção, os engenheiros podem reduzir o tempo de depuração e melhorar a confiabilidade do sistema.

O que é um Diagrama de Temporização? 🤔

Um diagrama de temporização é uma representação gráfica do comportamento dos sinais em um circuito digital ao longo do tempo. Diferentemente de um esquemático, que mostra conectividade, um diagrama de temporização mostra causalidade e relações temporais. Ele representa os níveis de sinal (alto, baixo ou flutuante) em relação a um eixo do tempo, permitindo que os projetistas verifiquem se os dados estão estáveis quando esperado.

Características principais incluem:

- Eixo do Tempo:Normalmente corre horizontalmente, representando a progressão dos eventos.

- Linhas de Sinal:Linhas verticais que representam fios específicos, barramentos ou estados lógicos.

- Bordas:Transições de baixo para alto (subida) ou alto para baixo (descida).

- Rótulos:Anotações que indicam tempos de preparação, tempos de manutenção ou atrasos.

Sem uma compreensão clara desses componentes, o diagrama torna-se fonte de confusão, e não de clareza.

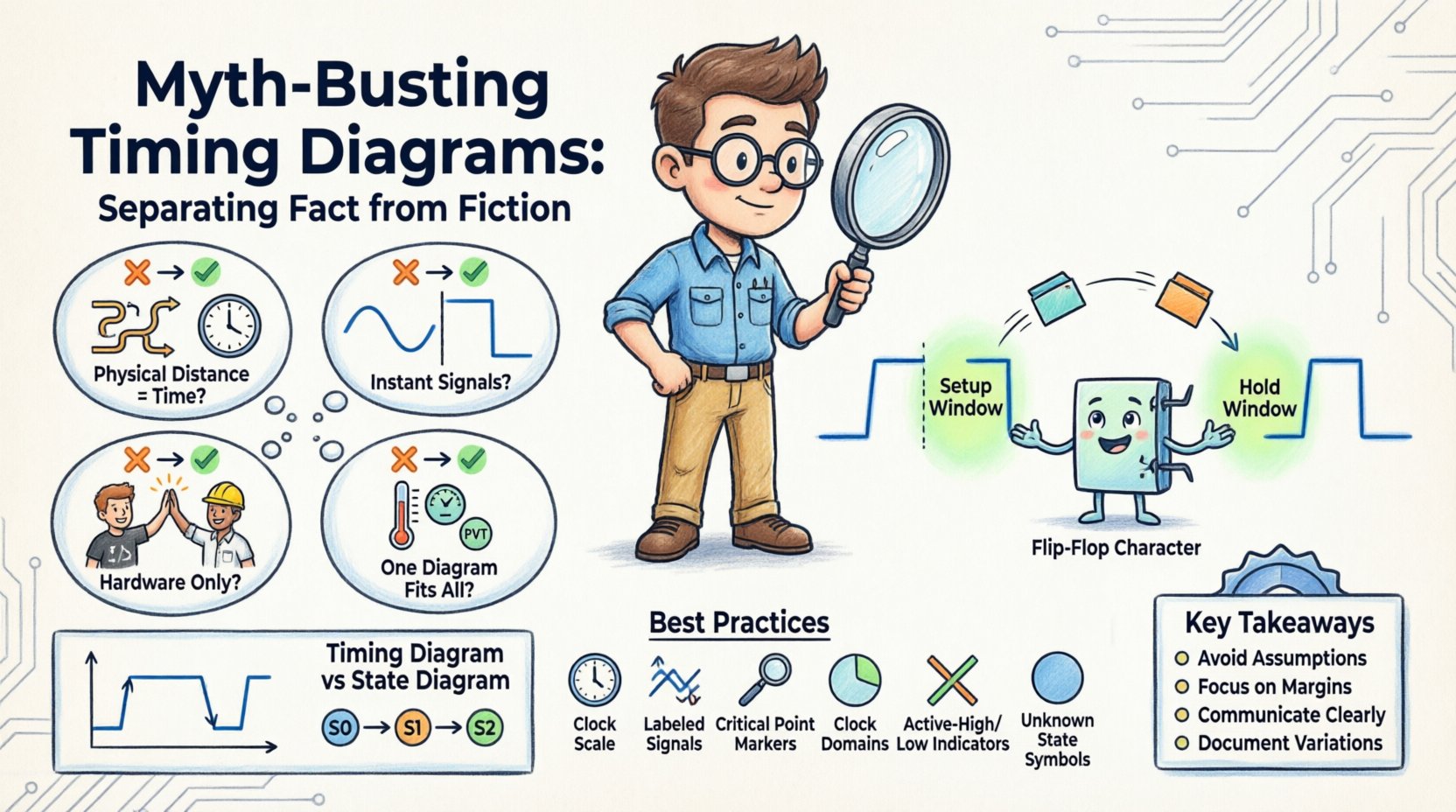

Mitos Comuns Sobre Diagramas de Temporização 🚫

Para melhorar a qualidade do design, devemos primeiro identificar as crenças falsas que levam a erros. Abaixo estão os mitos mais comuns que circulam nos círculos técnicos.

Mito 1: Diagramas de Temporização Mostram Distância Física Exata 📏

A Ficção:Engenheiros frequentemente assumem que a distância horizontal entre duas bordas em um diagrama está diretamente correlacionada ao comprimento físico da trilha em uma placa de circuito impresso.

O Fato:Diagramas de temporização representam tempo lógico ou elétrico, e não espaço físico. Embora o comprimento da trilha afete o atraso de propagação, o diagrama se concentra no resultadodesse atraso, e não na geometria em si. Um atraso de 1 nanossegundo pode representar uma trilha de 15 cm em uma placa FR4 ou uma trilha de 10 cm em uma trilha de cobre com constantes dielétricas diferentes. O diagrama abstrai o meio físico para se concentrar na janela de tempo.

- O comprimento físico determina o atraso, mas o diagrama mostra o valor do atraso.

- A complexidade de roteamento é oculta; apenas o resultado final importa.

- Assumir uma escala 1:1 entre tempo e distância leva a erros no layout.

Mito 2: As Transições de Sinal São Instantâneas ⚡

A Ficção:Em muitos diagramas, linhas verticais indicam que um sinal muda de estado imediatamente.

O Fato:Nenhum sinal físico muda de estado instantaneamente. Sempre há um tempo de subida e um tempo de descida. Quando um diagrama mostra uma borda vertical, representa uma transição rápida em relação ao período do clock, mas não nula. Ignorar os tempos de transição pode levar a problemas com a integridade do sinal, como oscilações ou crosstalk, que não são visíveis em diagramas idealizados.

- O tempo de subida é a duração para passar de 10% a 90% da tensão.

- Diagramas frequentemente simplificam isso para melhor legibilidade, mas a simulação deve levar isso em conta.

- Projetos de alta velocidade exigem modelagem explícita das inclinações de transição.

Mitologia 3: Diagramas de Temporização São Apenas para Engenheiros de Hardware 🛠️

A Ficção:Desenvolvedores de software e arquitetos de sistemas frequentemente ignoram os diagramas de temporização, assumindo que são irrelevantes para a lógica do código.

O Fato:O software deve respeitar as restrições de temporização do hardware. Interrupções, transferências DMA e E/S mapeadas em memória dependem todas do timing estabelecido pelo hardware. Se um driver tentar ler dados antes que o hardware ative o sinal “Pronto”, ocorre um erro de barramento. Diagramas de temporização são essenciais para a comunicação entre áreas multidisciplinares.

- Interrupções de software devem estar alinhadas com os ciclos de clock do hardware.

- As janelas de acesso à memória são definidas pelas especificações de temporização.

- Tanto as equipes de hardware quanto de software precisam de uma compreensão compartilhada da cronologia.

Mitologia 4: Um Diagrama Serve para Todos os Contextos 🌍

A Ficção:Um único diagrama de temporização pode descrever todo um sistema, independentemente das condições de operação.

O Fato:O temporização varia com temperatura, tensão e variações de processo (PVT). Um diagrama traçado para condições nominais pode falhar nos extremos. Os projetistas devem levar em conta os cenários mais desfavoráveis. Um diagrama que mostra o comportamento em condições ideais é frequentemente menos útil do que um que destaca os limites de operação.

- O atraso no pior caso determina o período mínimo do clock.

- A temperatura afeta a resistência e a capacitância.

- A variação de processo altera as velocidades de comutação dos transistores.

Aprofundamento: Tempos de Setup e Hold ⏱️

Compreender as violações de temporização é crítico. Dois conceitos específicos dominam a análise da integridade dos dados: Tempo de Setup e Tempo de Hold. Eles são frequentemente a fonte dos bugs mais difíceis de identificar em sistemas digitais.

Tempo de Setup (Tsu)

O tempo de setup é a quantidade mínima de tempoantesum borda de clock que os dados devem estar estáveis. Se os dados mudarem muito perto da borda de clock, o flip-flop receptor pode não capturar o valor correto.

- Ele garante que os dados estejam estabilizados antes que a janela de captura se feche.

- Violações causam metastabilidade ou estados lógicos incorretos.

- O atraso no caminho deve ser menor que o período do clock menos o tempo de setup.

Tempo de Manutenção (Th)

O tempo de manutenção é o tempo mínimo apósum borda de clock que os dados devem permanecer estáveis. Se os dados mudarem muito cedo após a borda do clock, o flip-flop pode perder o valor anteriormente capturado.

- Ele garante que os dados permaneçam estáveis por tempo suficiente para serem capturados.

- Violações são frequentemente mais difíceis de corrigir do que as violações de setup.

- O atraso no caminho deve ser maior que o requisito de tempo de manutenção.

Cenários de Violação de Temporização

Ao analisar um diagrama de temporização, procure os seguintes padrões:

- Violação de Setup: O sinal de dados ainda está mudando quando a borda do clock chega.

- Violação de Manutenção: O sinal de dados muda imediatamente após a borda do clock.

- Glitch: Um pulso curto que ocorre dentro da janela de setup/manutenção, mas não é uma transição válida.

Diagrama de Temporização vs. Diagrama de Estados 🔄

A confusão muitas vezes surge entre diagramas de temporização e diagramas de estados. Embora ambos descrevam o comportamento do sistema, eles respondem a perguntas diferentes. Um diagrama de estados mostra o queo sistema faz (fluxo lógico), enquanto um diagrama de temporização mostra quandoisso acontece (fluxo temporal).

| Funcionalidade | Diagrama de Temporização | Diagrama de Estados |

|---|---|---|

| Foco Principal | Tempo e Níveis de Sinal | Lógica e Fluxo de Controle |

| Representação dos Eixos | Horizontal = Tempo | Horizontal = Estados Lógicos |

| Melhor Para | Integridade de Sinal, Sincronização | Design de Algoritmos, Lógica de FSM |

| Complexidade | Alta detalhamento temporal | Alta ramificação lógica |

| Detalhes do Sinal | Mostra níveis de tensão (Alto/Baixo) | Mostra estados abstratos (Inativo/Executando) |

Usar o diagrama correto para a tarefa evita mal-entendidos. Uma máquina de estados pode ser projetada sem um diagrama de tempo, mas uma interface de barramento de alta velocidade não pode.

Melhores Práticas para Criar Diagramas Precisos ✅

Para garantir que sua documentação seja eficaz, siga estas diretrizes. A precisão na documentação reduz a ambiguidade na implementação.

- Defina a Escala de Tempo: Sempre especifique as unidades (ns, µs, ciclos). Se usar ciclos, defina a frequência do clock.

- Rotule Todos os Sinais: Não use nomes genéricos como “Sinal 1”. Use nomes descritivos como “CLK_IN” ou “DATA_VALID”.

- Marque Pontos Críticos: Destaque explicitamente as janelas de setup e hold com sombreamento ou anotações.

- Inclua Domínios de Clock: Se existirem múltiplos clocks, distinga-os claramente. Mostre a relação entre clocks assíncronos, se aplicável.

- Mostre Ativo Alto/Baixo: Esclareça se um estado ativo é Alto (1) ou Baixo (0) para evitar erros de polaridade.

- Indique Estados Desconhecidos: Use X ou Z para representar estados indefinidos ou de alta impedância em vez de deixá-los em branco.

Manuseio de Sinais Assíncronos 🔄

Uma das partes mais desafiadoras dos diagramas de tempo é o manuseio de sinais assíncronos. São sinais que não estão sincronizados com o clock principal do sistema. Eles introduzem incerteza que deve ser gerenciada.

- Metastabilidade: Quando um sinal assíncrono chega perto de uma borda de clock, o flip-flop pode entrar em um estado metastável. Ele eventualmente se estabilizará em 0 ou 1, mas o tempo necessário é imprevisível.

- Sincronizadores: Use cadeias de flip-flops para resolver a metastabilidade. Os diagramas de tempo devem mostrar a região metastável sendo resolvida antes da próxima borda de clock.

- Handshaking: Protocolos como I2C ou SPI usam handshaking assíncrono. O diagrama de tempo deve mostrar os estados de espera em que o mestre aguarda o escravo.

Aplicação no Mundo Real: Depuração de uma Condição de Corrida 🐞

Imagine um cenário em que uma barramento de dados não está sendo lido corretamente. O sistema trava ocasionalmente. Uma análise de diagrama de tempo revela o problema.

- Observação: O sinal “Pronto” é ativado ligeiramente após o estrobo de “Leitura”.

- Verificação do Diagrama: O diagrama de tempo mostra que a borda do sinal “Pronto” cai dentro da janela de setup do estrobo de “Leitura”.

- Conclusão: Os dados estão sendo lidos antes de serem válidos.

- Correção: Ajuste a lógica para atrasar o estrobo de “Leitura” ou estender o pulso do sinal “Pronto”.

Este exemplo destaca por que visualizar o cronograma é crucial. Sem o diagrama, a condição de corrida permanece oculta na lógica do código.

Ferramentas e Métodos de Análise 🔍

Embora nomes específicos de software não sejam o foco, os métodos de análise permanecem constantes. A engenharia moderna depende de simulações e visualizadores de ondas para validar diagramas de tempo.

- Simulação: Execute testbenches para gerar ondas que correspondam à intenção do projeto.

- Análise de Tempo Estática (STA): Calcule atrasos sem simulação para verificar violações em todos os caminhos.

- Depuração em Hardware: Use osciloscópios para capturar ondas do mundo real e compará-las com o diagrama teórico.

- Controle de Versão: Mantenha os diagramas de tempo sob controle de versão. Mudanças no hardware frequentemente exigem atualizações nas especificações de tempo.

O Impacto do Jitter e do Desvio 📉

Diagramas de tempo são frequentemente desenhados com linhas perfeitas e retas. A realidade é mais bagunçada. O jitter e o desvio são fontes de ruído que afetam a precisão do tempo.

- Jitter: Variações no tempo das bordas de um sinal. O jitter do clock faz com que a janela de amostragem se mova.

- S skew: A diferença no tempo de chegada do mesmo sinal de clock em pontos diferentes do circuito.

- Impacto: Ambos reduzem a margem de tempo. Um diagrama de tempo deveria, idealmente, mostrar a margem, e não apenas a borda ideal.

Resumo dos Principais Aprendizados 📝

Diagramas de tempo são mais do que simples desenhos; são especificações de comportamento. Ao compreender os mitos e fatos que os cercam, engenheiros podem projetar sistemas mais robustos.

- Evite Suposições: Não assuma transições instantâneas ou sincronização perfeita.

- Concentre-se nas Margens: Os tempos de setup e hold são os buffers de segurança que evitam falhas.

- Comunique-se Claramente: Use diagramas para pontuar a lacuna entre equipes de hardware e software.

- Documente Variações: Reconheça que o tempo muda com o ambiente e o processo.

Quando você olha para um diagrama de tempo, veja o tempo. Veja as restrições. Veja a confiabilidade. Essa perspectiva transforma uma imagem estática em uma ferramenta poderosa para a excelência em engenharia.