Sistemas digitais dependem de uma sincronização precisa para funcionar corretamente. Sem um tempo preciso, a corrupção de dados, travamentos do sistema e falhas de segurança tornam-se inevitáveis. Um diagrama de tempo fornece uma representação visual de como os sinais mudam ao longo do tempo, oferecendo uma visão clara das relações entre ciclos de clock, validade de dados e sinais de controle. Este guia explora o papel crítico dos diagramas de tempo em diversos setores, detalhando exemplos práticos e soluções técnicas para desafios comuns.

🔍 Compreendendo os Fundamentos

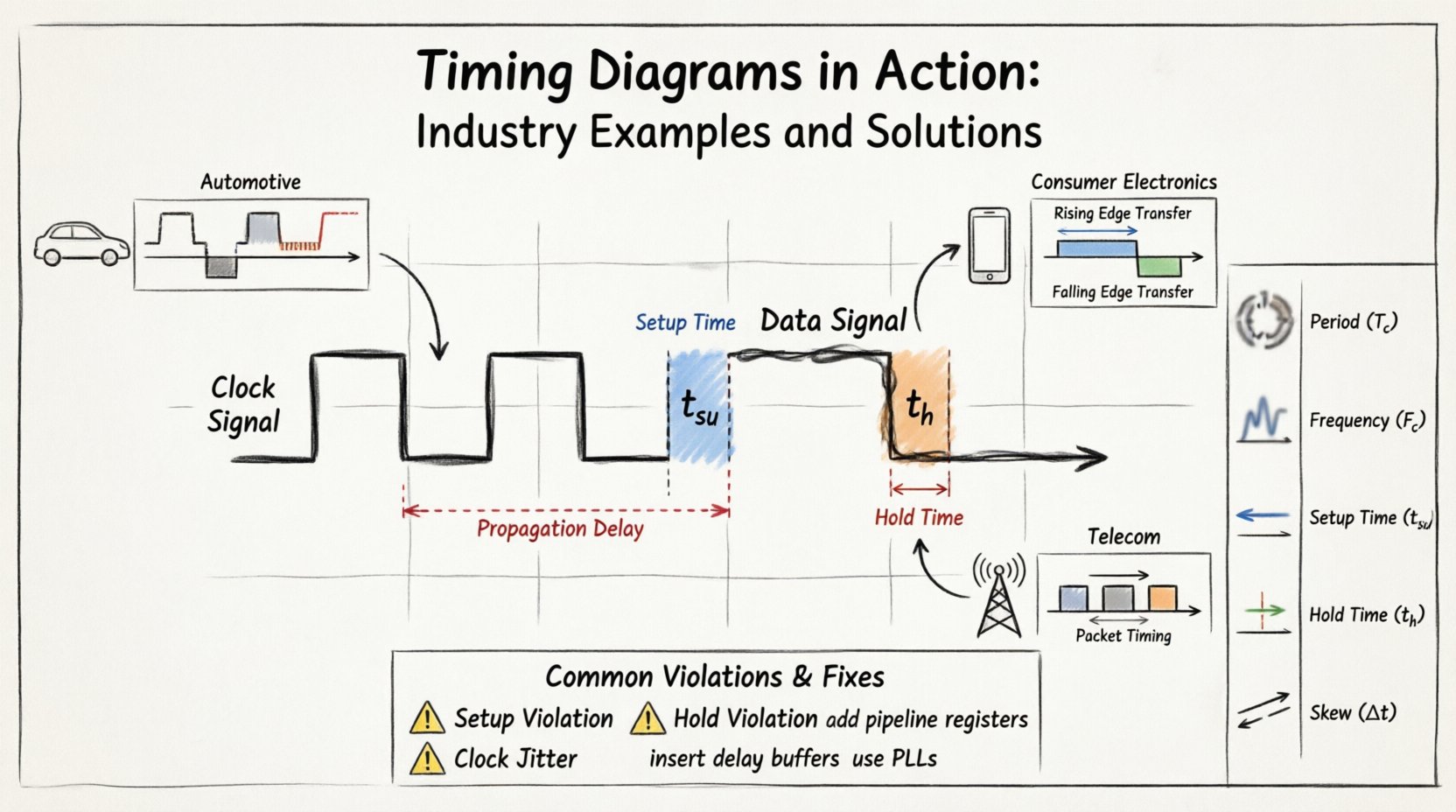

Antes de mergulhar em aplicações específicas, é essencial compreender os componentes principais de um diagrama de tempo. Esses diagramas mapeiam o comportamento dos sinais em relação a um clock de referência. Eles não são meros desenhos; são restrições matemáticas que determinam o comportamento do hardware.

- Bordas de Sinal: A transição de baixo para alto (borda ascendente) ou de alto para baixo (borda descendente) dispara mudanças de estado na lógica sequencial.

- Período do Clock: A duração entre duas bordas consecutivas do mesmo polaridade define o tempo disponível para a lógica se estabilizar.

- Atraso de Propagação: O tempo que leva para um sinal viajar de um pino de entrada até um pino de saída através de portas lógicas.

- Tempos de Setup e Hold: Restrições críticas que garantem que os dados estejam estáveis antes e após a borda do clock.

Quando esses parâmetros são violados, o circuito pode entrar em um estado metastável, levando a um comportamento imprevisível. Engenheiros usam diagramas de tempo para verificar se a implementação física de um projeto atende a esses requisitos lógicos.

🚗 Eletrônica Automotiva: Tempo Crítico para a Segurança

A indústria automobilística exige o mais alto nível de confiabilidade. Veículos contêm dezenas de Unidades de Controle Eletrônico (ECUs) que se comunicam por barramentos como CAN (Rede de Área de Controle), LIN (Rede de Interconexão Local) e FlexRay. A análise de tempo aqui não é apenas sobre velocidade; é sobre determinismo e segurança.

1. Arbitragem no Barramento CAN

O barramento CAN permite que múltiplos nós se comuniquem em um único fio. O diagrama de tempo para a arbitragem CAN revela como a prioridade é determinada durante a concorrência no barramento.

- Dominante vs. Receptivo: Níveis lógicos são representados por estados de tensão. Um bit dominante (0) sobrepõe um bit receptivo (1).

- Sincronização: Os nós se sincronizam com o bit de início de quadro usando segmentos de sincronização.

- Ponto de Amostragem: Os dados são amostrados em uma porcentagem específica do tempo do bit para evitar ruídos.

Se o ponto de amostragem estiver muito próximo da borda, o ruído pode causar erros de bit. Se for muito tarde, os dados podem não estar estáveis. Diagramas de tempo ajudam engenheiros a definir corretamente o ponto de amostragem, geralmente em torno de 80% do tempo do bit.

2. Amostragem de ADC na Fusão de Sensores

Veículos modernos usam múltiplos sensores (radar, lidar, câmeras) para criar uma percepção do ambiente. Conversores Analógico-Digitais (ADCs) devem amostrar sinais em intervalos precisos para evitar o fenômeno de aliasing.

- Jitter do Clock:Variações no tempo da borda do clock introduzem ruído no sinal digitalizado.

- Latência: O tempo desde a entrada do sensor até a saída de dados processados deve ser minimizado para controle em tempo real.

- Interleaving:Múltiplos ADCs frequentemente operam em paralelo. Diagramas de tempo garantem que suas fases estejam alinhadas para evitar lacunas nos dados.

📱 Eletrônicos de Consumo: Interfaces de Alta Velocidade

Dispositivos de consumo priorizam desempenho e eficiência energética. Interfaces como memória DDR e links de exibição exigem janelas de tempo rigorosas para alcançar largura de banda elevada sem aumentar o consumo de energia.

1. Interfaces de Memória DDR

A memória de taxa dupla (DDR) transfere dados tanto na borda ascendente quanto na descendente do sinal de clock. Isso duplica a taxa efetiva de dados, mas reduz pela metade a janela de tempo para estabilidade dos dados.

| Parâmetro | Definição | Impacto da Violacão |

|---|---|---|

| Tempo de Setup | Tempo em que os dados devem estar estáveis antes da borda do clock | Transferência de dados perdida, travamento do sistema |

| Tempo de Hold | Tempo em que os dados devem permanecer estáveis após a borda do clock | Dados corrompidos, inversão de bits |

| Clock Skew | Diferença no tempo de chegada do clock em diferentes chips | Margem de tempo reduzida, instabilidade |

| Ciclo de Trabalho | Razão entre o tempo alto e o período total | Desempenho desbalanceado, aumento de jitter |

Na DDR4 e DDR5, o barramento de comandos e endereços frequentemente opera em frequência mais baixa que o barramento de dados. Diagramas de tempo devem levar em conta os sinais de strobe fonte-síncronos (DQS) que acompanham os dados para indicar janelas válidas.

2. Interfaces de Exibição (MIPI DSI)

Dispositivos móveis usam a Interface Serial de Exibição MIPI (DSI) para conectar o processador à tela. Essa interface utiliza faixas diferenciais de alta velocidade.

- Modo de Comando LP:Modo de baixo consumo para envio de comandos, dependendo de tempo rigoroso para sequências de ativação.

- Modo de Dados HS:Transmissão de alta velocidade em que a recuperação do clock é realizada na corrente de dados.

- Tempo de Troca:O tempo necessário para alternar do modo de transmissão para o modo de recepção na mesma faixa.

Desalinhamento nestes diagramas de tempo resulta em artefatos na tela, piscar ou perda total da saída de vídeo.

📡 Telecomunicações: Latência e Largura de Banda

Em telecomunicações, o tempo é sinônimo de latência. Os tempos de entrega de pacotes e a sincronização em redes distribuídas são críticos para serviços como 5G e negociação de alta frequência.

1. Sinalização PCIe

O padrão Peripheral Component Interconnect Express (PCIe) é amplamente utilizado para conectar componentes de alta velocidade. Ele utiliza faixas seriais com relógios embutidos ou relógios fonte-síncronos.

- Equalização:A integridade do sinal degrada com a distância. Diagramas de tempo mostram como os filtros de equalização compensam as perdas.

- Treinamento de Link: Uma sequência de estados com tempo definido para estabelecer a velocidade do link e a largura da faixa.

- Controle de Fluxo:Janelas de tempo para controle de fluxo baseado em créditos evitam estouros de buffer.

2. PHYs de Ethernet

Ethernet padrão depende de um relógio compartilhado ou recuperação de relógio. Ethernet de Gigabit e além usam codificação 8b/10b para garantir transições suficientes para recuperação de relógio.

- Períodos de Inatividade: Janelas de tempo definidas em que nenhum dado é enviado para manter a sincronização.

- Delimitador de Início de Quadro: Um padrão específico de bits que marca o início de um pacote, exigindo tempo de detecção preciso.

- Intervalo entre Pacotes: Uma demora obrigatória entre pacotes para permitir que o hardware seja reiniciado.

⚠️ Violações Comuns de Tempo e Soluções

Mesmo com um projeto cuidadoso, ocorrem violações de tempo. Identificar a causa raiz exige analisar o diagrama de tempo para ver onde os sinais divergem das expectativas.

1. Violações de Tempo de Setup

Ocorre quando os dados chegam muito tarde para serem capturados pela borda do relógio.

- Causas: Profundidade excessiva da lógica, atrasos longos em fios ou desvio de relógio (clock skew).

- Soluções:

- Insira registradores de pipeline para quebrar caminhos longos.

- Otimize a síntese lógica para reduzir o número de portas.

- Ajuste a frequência do relógio para fornecer mais tempo.

2. Violações de Tempo de Hold

Ocorre quando os dados mudam muito rapidamente após o borda do clock, sobrescrevendo o valor capturado.

- Causas:Atrasos em caminhos curtos, desvio de clock onde o clock de captura chega muito tarde.

- Soluções:

- Insira buffers de atraso na trajetória de dados.

- Use técnicas de retiming para equilibrar caminhos.

- Garanta que a rede de distribuição de clock tenha o mínimo de desvio possível.

3. Desvio de Clock e Jitter

O desvio é a diferença no tempo de chegada do sinal de clock em diferentes registradores. O jitter é a variação de curto prazo da borda do clock.

- Impacto:Reduz a margem de tempo efetiva disponível para os dados.

- Soluções:

- Use geradores de clock com baixo jitter.

- Projete árvores de clock balanceadas com traços de comprimento igual.

- Implemente laços de fase (PLLs) para limpar os sinais de clock.

✅ Melhores Práticas para Implementação

Alcançar um tempo robusto exige uma abordagem sistemática durante todo o ciclo de vida do projeto. Documentação e verificação são tão importantes quanto o próprio circuito.

1. Defina Restrições de Tempo cedo

Não espere até a fase de implementação para definir os requisitos de tempo. Documente as frequências de clock, atrasos de entrada e atrasos de saída na especificação do projeto. Isso garante que todos os envolvidos compreendam os limites do sistema.

2. Use Análise de Tempo Estática

Ferramentas de Análise de Tempo Estática (STA) calculam os caminhos de atraso no pior caso sem simular todas as combinações de entrada. Este método é eficiente e cobre todos os estados possíveis, garantindo que nenhuma violação de tempo seja perdida.

3. Valide com Simulação

Embora a STA seja poderosa, a simulação dinâmica fornece uma visão do comportamento dos sinais sob condições específicas. Use a simulação para verificar caminhos críticos, especialmente aqueles que envolvem lógica assíncrona ou máquinas de estado complexas.

4. Considerações de Projeto Físico

O layout físico do chip ou placa afeta diretamente o tempo.

- Comprimento do Fio:Fios mais longos introduzem mais capacitância e resistência, aumentando o atraso.

- Crosstalk:Sinais vizinhos podem induzir ruído, causando transições falsas.

- Ruído na Alimentação Elétrica:Quedas de tensão podem reduzir a velocidade de comutação das portas.

🛠️ Solução de Problemas em Cenários do Mundo Real

Quando um sistema falha em atender aos requisitos de tempo, é necessário um processo estruturado de depuração. Os seguintes passos descrevem uma abordagem lógica para resolver problemas de tempo.

- Passo 1: Identifique a Trilha.Localize a trilha específica de registrador para registrador que está causando a falha. Consulte o relatório de tempo para o slack mais negativo.

- Passo 2: Analise os Sinais.Use um visualizador de diagrama de tempo para inspecionar as transições reais do sinal. Compare-as com os valores esperados.

- Passo 3: Verifique o Clock.Verifique a qualidade do sinal de clock. Procure por jitter, distorção no ciclo de trabalho ou glitches.

- Passo 4: Revise as Restrições.Garanta que as restrições no arquivo de projeto correspondam à realidade física do hardware.

- Passo 5: Itere.Faça alterações na lógica ou no layout, depois execute novamente a análise de tempo.

📊 Resumo dos Parâmetros de Tempo

Para facilitar a consulta rápida, aqui está um resumo dos principais parâmetros de tempo utilizados em diversas indústrias.

| Parâmetro | Símbolo | Unidade Típica | Descrição |

|---|---|---|---|

| Período | Tc | ns | Tempo entre bordas consecutivas do clock |

| Frequência | Fc | Hz | Inverso do período |

| Tempo de Setup | tsu | ns | Estabilidade de dados necessária antes do front do clock |

| Tempo de retenção | th | ns | Estabilidade de dados necessária após o front do clock |

| Atraso de propagação | tpd | ns | Tempo necessário para o sinal passar pelo circuito lógico |

| Desvio | Δt | ps | Diferença de tempo de chegada do clock |

🔄 Gerenciamento de Projetos Assíncronos

Nem todos os sistemas funcionam com um único clock. Projetos assíncronos envolvem dados que cruzam entre domínios de clock diferentes. Isso introduz o risco de metastabilidade, em que um flip-flop entra em um estado indefinido.

- Cadeias de Sincronização: Use um sincronizador de múltiplos estágios (normalmente dois flip-flops) para permitir que o sinal se estabilize antes de ser utilizado.

- Protocolos de Handshake: Implemente mecanismos de solicitação-confirmação para garantir que o receptor esteja pronto antes de os dados serem enviados.

- Buffers FIFO: Use estruturas de memória FIFO para desacoplar as velocidades do produtor e do consumidor.

Diagramas de tempo para projetos assíncronos mostram a relação entre os dois clocks independentes. A chave é garantir que o caminho de dados tenha tempo suficiente para se estabilizar antes que o clock receptor o amostrasse.

🌟 Considerações Finais

Diagramas de tempo são a base da verificação de sistemas digitais. Eles pontuam a lacuna entre a lógica abstrata e a realidade física. Ao compreender as nuances do tempo de setup, tempo de retenção, desvio de clock e jitter, engenheiros podem projetar sistemas robustos, eficientes e confiáveis.

Seja em sistemas de segurança automotiva, dispositivos de consumo ou infraestrutura de telecomunicações, os princípios permanecem os mesmos. Precisão no tempo leva à precisão no desempenho. Monitoramento contínuo e aderência às melhores práticas garantem que os projetos permaneçam funcionais ao longo de sua vida útil. À medida que a tecnologia avança e as velocidades aumentam, a importância da análise detalhada de tempo só crescerá.

Para equipes que buscam melhorar a qualidade de seus projetos, investir tempo em diagramas de tempo precisos e fluxos de verificação é essencial. Isso reduz o risco, diminui os custos de depuração e garante que o produto final atenda às suas especificações. Com as ferramentas e metodologias certas, os desafios de tempo tornam-se limitações gerenciáveis em vez de obstáculos.