Na arquitetura de sistemas digitais, o fluxo de informações é regido pelo tempo. Um diagrama de tempo não é meramente um desenho; é um contrato entre a intenção do projeto e a implementação física. Quando os sinais não se alinham dentro de janelas temporais precisas, surgem condições de corrida, ocorre corrupção de dados e a confiabilidade do sistema colapsa. Este guia fornece uma estrutura rigorosa para validar modelos de tempo, garantindo que cada transição, borda e restrição reflita a realidade operacional do hardware.

A precisão na representação de tempo é a diferença entre um protótipo funcional e uma falha no campo. Seja ao definir um protocolo de comunicação ou especificar o comportamento de um registrador, a clareza do diagrama de tempo determina o sucesso das fases de verificação e implementação. Este checklist apresenta os elementos críticos necessários para manter alta fidelidade em seus modelos de tempo.

Por que a Precisão do Diagrama de Tempo Importa 🎯

Diagramas de tempo servem como referência principal para engenheiros durante a implementação de máquinas de estados finitos, protocolos de barramento e lógica de interface. Eles traduzem a lógica abstrata em restrições temporais que o silício físico deve obedecer. Inaccurácias nesses modelos frequentemente decorrem de representações simplificadas de eventos assíncronos ou estados de sinal indefinidos.

Erros na documentação de tempo se propagam por toda a vida útil do desenvolvimento. Uma definição incorreta de borda de clock pode levar a violações de setup. Uma polaridade de reset ambígua pode causar o sistema a inicializar em um estado indefinido. O custo de corrigir um erro de tempo na fase de projeto é significativamente menor do que o custo de um novo ciclo de fabricação de silício ou de um patch de firmware implantado no campo.

Principais razões para manter uma precisão rigorosa incluem:

- Alinhamento de Verificação:Testbenches de simulação dependem desses diagramas para gerar estímulos. Se o diagrama estiver errado, o testbench validará um comportamento incorreto.

- Consistência na Implementação:O código em linguagem de descrição de hardware deve corresponder à especificação de tempo. Discrepâncias levam a avisos de síntese e falhas no fechamento de tempo.

- Interoperabilidade: Ao interagir com componentes externos, as margens de tempo garantem uma comunicação confiável entre diferentes sistemas.

- Eficiência na Depuração: Quando um sistema falha, diagramas de tempo precisos fornecem uma base para a análise da causa raiz.

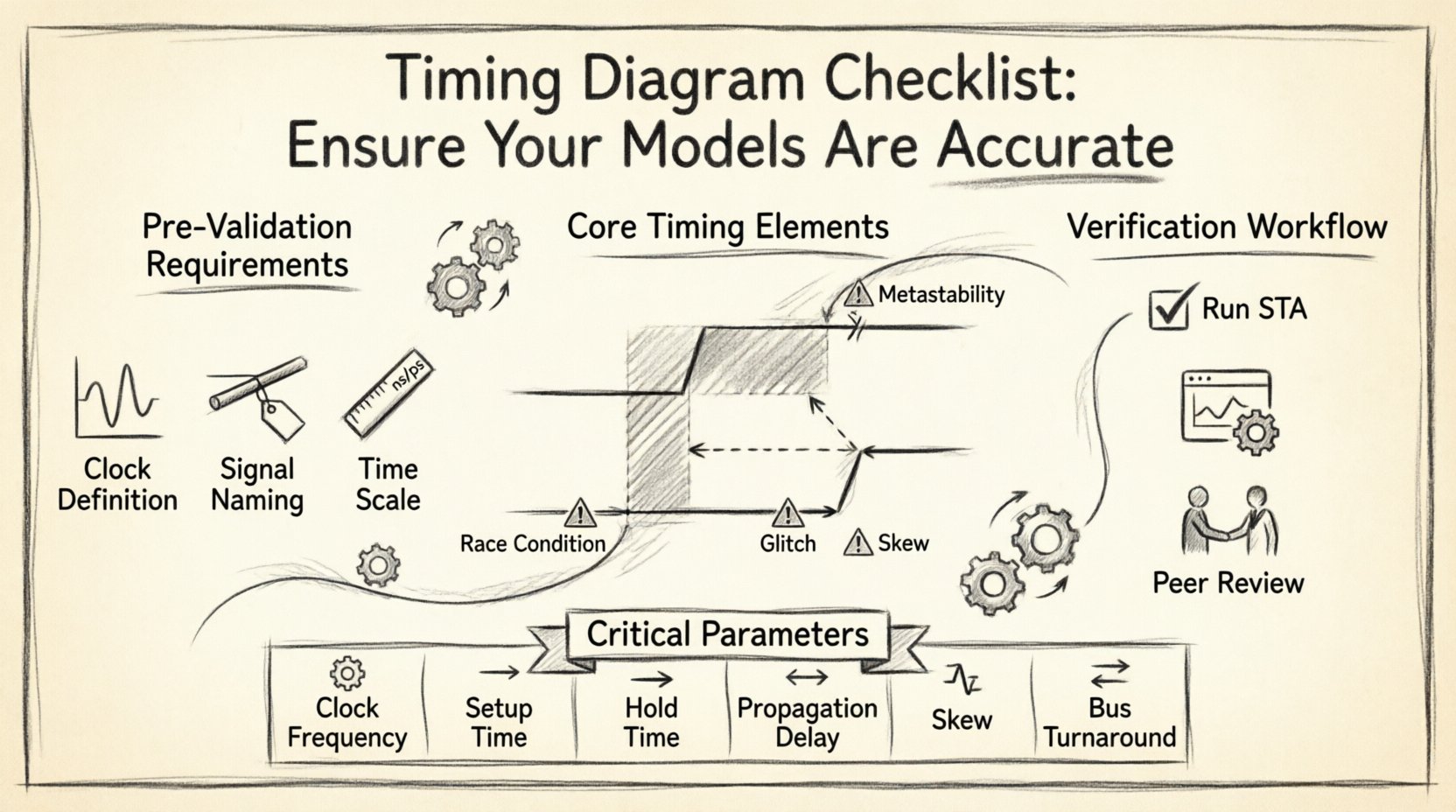

Requisitos de Pré-Validação ✅

Antes de revisar o próprio diagrama, o contexto ao redor dos sinais deve ser estabelecido. Um diagrama sem contexto é uma coleção de linhas que pouco significam. Certifique-se de que os seguintes elementos fundamentais estejam definidos antes de prosseguir para o checklist de nível de sinal.

1. Definição do Clock do Sistema

Todo sistema síncrono depende de uma fonte de clock. O diagrama deve indicar explicitamente a frequência, a relação de fase e o ciclo de trabalho. A ambiguidade aqui leva a problemas de cruzamento de domínios de clock.

- A frequência do clock está especificada em Hertz?

- Há múltiplos domínios de clock? Se sim, eles são rotulados de forma distinta?

- A borda do clock está definida (subida ou descida) para todos os elementos sequenciais?

2. Convenções de Nomeação de Sinais

A consistência na nomeação evita mal-entendidos durante a implementação do código. Os sinais devem seguir uma convenção padrão que indique o tipo, a direção e a polaridade.

- Use indicadores ativos-alto ou ativos-baixo de forma consistente.

- Garanta que os sinais de barramento sejam agrupados logicamente (por exemplo, DATA[7:0]).

- Evite nomes genéricos comoSig1 ou Ctrl sem contexto.

3. Escala de Tempo e Unidades

O eixo horizontal representa o tempo. Sem unidades claras, o diagrama torna-se inútil para análise de tempo.

- Especifique a unidade de tempo (ns, ps, µs, ciclos de clock).

- Garanta que a escala seja linear, a menos que o diagrama indique explicitamente uma visualização ampliada de um evento específico.

- Marque marcadores de tempo em intervalos regulares para facilitar a medição.

Lista de Verificação dos Elementos Principais de Temporização 📋

Esta seção detalha as características específicas do sinal que devem ser verificadas. Cada elemento representa um ponto potencial de falha se não for definido explicitamente.

1. Estados e Níveis de Sinal

Os sinais digitais existem em estados discretos. O diagrama deve representar claramente o que constitui um nível lógico um e um nível lógico zero, bem como estados de alta impedância.

- Níveis Lógicos: São níveis de tensão ou estados lógicos (0/1) utilizados? Garanta consistência em todo o documento.

- Estado High-Z: Para barramentos tri-estado, o diagrama deve mostrar a transição para o estado de alta impedância. Isso é crítico para evitar conflitos de barramento.

- Estados Indefinidos: Se um sinal puder entrar em um estado flutuante ou desconhecido, ele deve ser marcado. Não assuma um valor padrão.

2. Bordas de Transição

O momento em que um sinal muda de estado é o momento mais crítico na lógica digital. Violações de tempo ocorrem frequentemente nessas bordas.

- Borda de Subida: Marque claramente a transição de baixo para alto.

- Borda de Queda: Marque claramente a transição de alto para baixo.

- Taxa de Subida (Slew Rate): Embora frequentemente abstraídos, a inclinação da transição pode afetar as margens de tempo. Indique se transições lentas são esperadas devido à capacitância de carga.

- Glitches: Se um sinal for propenso a glitches transitórios, indique-os explicitamente. Não desenhe uma linha limpa se o sinal for ruidoso.

3. Tempos de Setup e Hold

Para flip-flops e latchs, os dados devem ser estáveis antes e após a borda ativa do clock. Essas restrições são irrenunciáveis no design síncrono.

- Tempo de Setup (tsu): O tempo mínimo em que os dados devem permanecer estáveis antes do fronteira do clock.

- Tempo de retenção (th): O tempo mínimo em que os dados devem permanecer estáveis após o fronteira do clock.

- Margens de violação: Inclua margens de segurança no diagrama para levar em conta variações de processo e mudanças de temperatura.

4. Latência e Atrasos

A propagação do sinal não é instantânea. Os atrasos se acumulam em portas lógicas e interconexões.

- Especifique os atrasos de propagação entre entrada e saída.

- Leve em conta os atrasos da lógica combinacional no caminho.

- Indique se os atrasos são no pior caso, típicos ou no melhor caso.

Integridade do Sinal e Níveis 🔌

A integridade do sinal abrange a qualidade do sinal enquanto ele percorre o sistema. Em diagramas de tempo, isso é frequentemente representado pela clareza da forma de onda.

1. Ruído e Jitter

Sinais do mundo real estão sujeitos a ruído. Um diagrama de tempo que mostra bordas perfeitas é teoricamente útil, mas praticamente enganoso.

- Jitter: Variações no tempo de uma borda do sinal. Um jitter alto pode reduzir a margem de tempo efetiva.

- Nível de ruído: Se o sinal opera próximo a um limiar de ruído, o diagrama deve refletir a faixa de incerteza.

- Janelas de amostragem: Defina a janela dentro da qual o receptor amostra o sinal. Essa janela deve acomodar o jitter.

2. Dependências da fonte de alimentação

O tempo de sinal pode variar com base nos níveis de tensão. Flutuações na alimentação podem causar desvio de tempo.

- Especifique a faixa de tensão de operação para os componentes envolvidos.

- Indique se as restrições de tempo mudam sob diferentes condições de tensão (por exemplo, operação em baixa tensão).

- Considere as sequências de desligamento e ligamento no modelo de tempo.

Tabela: Referência de Parâmetros Críticos de Tempo

| Parâmetro | Definição | Impacto do Erro | Método de Verificação |

|---|---|---|---|

| Frequência do Clock | Taxa de ciclos de clock por segundo | Descompasso de velocidade do sistema, perda de dados | Contador de frequência, Osciloscópio |

| Tempo de Preparação | Tempo em que os dados devem estar estáveis antes do fronte do clock | Metastabilidade, captura incorreta de dados | Análise de Temporização Estática |

| Tempo de Manutenção | Tempo em que os dados devem estar estáveis após o fronte do clock | Metastabilidade, corrupção de dados | Análise de Temporização Estática |

| Atraso de Propagação | Tempo necessário para o sinal percorrer do entrada à saída | Violações de temporização, condições de corrida | Ondas de Simulação |

| Desvio | Diferença no tempo de chegada do clock em diferentes registradores | Margem de temporização reduzida, problemas de domínio de clock | Análise da Árvore de Clock |

| Tempo de Inversão de Bus | Tempo para mudar do estado de driver para receptor | Contenção de bus, colisão de dados | Simulação de Integridade de Sinal |

Domínio de Clock e Sincronização ⏲️

Sistemas modernos frequentemente operam em múltiplos domínios de clock. Cruzar essas fronteiras introduz uma complexidade significativa que deve ser capturada no diagrama de temporização.

1. Cenários de Multi-Clock

Quando os sinais cruzam de um domínio de clock para outro, a relação entre os clocks deve ser definida.

- Razão de frequência:Um clock é múltiplo do outro?

- Relação de fase:Os clocks estão alinhados ou há um deslocamento de fase fixo?

- Clocks assíncronos:Se os clocks forem independentes, o diagrama deve indicar a necessidade de lógica de sincronização (por exemplo, sincronizadores, FIFOs).

2. Tratamento de metastabilidade

Quando sinais assíncronos entram em um sistema síncrono, há risco de causar metastabilidade. O diagrama de tempo deve levar em conta o tempo de recuperação necessário.

- Especifique o tempo de recuperação da metastabilidade.

- Indique o uso de sincronizadores de múltias etapas.

- Defina a probabilidade de falha aceitável para a aplicação.

3. Gating de clock

Para economizar energia, os clocks são frequentemente desligados quando a lógica está ociosa. Isso introduz complexidades de tempo.

- Mostre o sinal de habilitação para o gate de clock.

- Defina a largura mínima do pulso necessária para acionar o clock com gate.

- Garanta que a lógica de gating não introduza glitches.

Transições de estado e lógica de reset 🔄

O comportamento da lógica é definido pelas transições de estado. O diagrama de tempo deve refletir com precisão como o sistema se move entre estados e como ele é inicializado.

1. Sequência de reset

Todo sistema digital precisa de um estado inicial definido. O sinal de reset é crítico para isso.

- Nível ativo:O reset é ativo em nível alto ou em nível baixo?

- Largura do pulso:Por quanto tempo o sinal de reset deve permanecer ativo para garantir que todos os registradores sejam limpos?

- Ordem de liberação:Se existirem múltiplos sinais de reset, há uma ordem específica de liberação? (por exemplo, reset do núcleo antes do reset de I/O).

- Assíncrono vs. Síncrono:O reset limpa imediatamente ou na próxima borda de clock?

2. Transições da máquina de estados

Máquinas de Estados Finitos (FSM) definem a lógica operacional. O diagrama de tempo deve mapear as condições de transição.

- Identifique as condições de entrada que desencadeiam uma mudança de estado.

- Mostre a duração da saída associada a cada estado.

- Destaque quaisquer estados ilegais e como o sistema os trata.

3. Protocolos de Handshake

Muitas interfaces usam handshakes para gerenciar o fluxo de dados. O tempo desses sinais é vital.

- Requisição (REQ): Quando os dados estão prontos para serem enviados?

- Confirmação (ACK): Quando o receptor confirma a recepção?

- Tempo limite: O que acontece se o handshake não for concluído dentro de um determinado tempo?

Verificação e Cruzamento de Verificação 🔍

Uma vez que o diagrama é elaborado, ele deve passar por um processo rigoroso de revisão. Isso envolve comparar o diagrama com os resultados da simulação e com as restrições físicas.

1. Comparação de Formas de Onda de Simulação

Execute uma simulação usando as restrições de tempo definidas no diagrama. Compare as formas de onda de saída reais com o diagrama planejado.

- As bordas dos sinais estão alinhadas com as bordas do clock conforme esperado?

- Os tempos de setup e hold foram atendidos na simulação?

- Os valores de dados correspondem à sequência esperada?

2. Análise de Tempo Estática (STA)

Ferramentas de STA analisam os caminhos de tempo sem executar simulações. Elas fornecem uma prova matemática da correção do tempo.

- Verifique as violações de tempo relatadas pela engine de STA.

- Revise os valores de folga para os caminhos críticos.

- Garanta que as restrições de tempo no diagrama correspondam aos arquivos de restrições usados pela ferramenta de análise.

3. Revisão por Pares

A revisão humana é essencial para detectar erros lógicos que as ferramentas podem ignorar.

- Tenha um segundo engenheiro revisar o diagrama quanto à clareza e consistência.

- Verifique convenções de nomeação e consistência de unidades.

- Verifique se o diagrama corresponde à especificação arquitetônica.

Violações Comuns de Tempo 🚫

Mesmo com uma lista de verificação, ocorrem erros. O conhecimento dos perigos comuns ajuda na prevenção e na resolução de problemas.

1. Condições de Corrida

Ocorre quando a saída de um sinal depende da ordem em que outros sinais chegam.

- Evite lógica em que dois sinais acionam o mesmo nó com tempos diferentes.

- Garanta que os laços de feedback sejam interrompidos ou corretamente sincronizados.

- Verifique se há caminhos lógicos com atrasos muito diferentes alimentando o mesmo registrador.

2. Metastabilidade

Quando um sinal muda muito perto da borda do clock, o flip-flop pode não se estabilizar em 0 ou 1.

- Minimize a probabilidade de entradas assíncronas atingirem a borda de amostragem.

- Use sincronizadores para quaisquer entradas externas.

- Projete para o pior caso de jitter e desvio.

3. Glitchs

Pulsos indesejados causados por atrasos na propagação da lógica.

- Garanta que a lógica combinacional não alimente diretamente linhas de controle sensíveis.

- Use lógica de bloqueio de clock que evite que os glitchs alcancem a árvore de clock.

- Verifique se os sinais de habilitação estão estáveis antes da borda do clock.

4. Desvio de Clock

O clock chega em registradores diferentes em tempos diferentes.

- Minimize o desvio na rede de distribuição de clock.

- Leve em conta o desvio nos cálculos de tempo de setup e hold.

- Use árvores de clock com buffer para manter a uniformidade.

Documentação e Manutenção 📝

Um diagrama de tempo é um documento vivo. À medida que o projeto evolui, o diagrama deve ser atualizado para refletir as mudanças.

1. Controle de Versão

Mantenha o controle das mudanças no diagrama de tempo ao longo do tempo.

- Inclua uma tabela de histórico de revisões na documentação.

- Controle a versão dos arquivos do diagrama juntamente com o código.

- Registre o motivo de cada mudança (por exemplo, “Atualizado para refletir nova frequência de clock”).

2. Notas Contextuais

Adicione notas ao diagrama para explicar comportamentos complexos.

- Use caixas de texto para explicar janelas de tempo específicas.

- Referencie as seções relacionadas da especificação.

- Inclua avisos sobre restrições críticas.

3. Entrega para a Implementação

Garanta que a equipe construindo o sistema tenha a versão correta do diagrama.

- Forneça o diagrama em um formato acessível a todos os interessados.

- Realize uma sessão de revisão com a equipe de implementação.

- Reúna feedback da equipe de implementação para melhorar diagramas futuros.

Pensamentos Finais sobre Rigor de Tempo 🛡️

Criar um diagrama de tempo preciso é uma disciplina que exige atenção aos detalhes e um profundo entendimento da tecnologia subjacente. Não basta desenhar linhas; é necessário compreender a física e a lógica que regem essas linhas. Ao seguir esta lista de verificação, você garante que seus modelos sejam robustos, confiáveis e prontos para implementação.

O esforço investido na validação de diagramas de tempo traz dividendos em tempo reduzido de depuração e qualidade superior do sistema. Em uma indústria onde as margens são apertadas e os custos são altos, a precisão é o ativo mais valioso que você possui. Trate cada borda e cada atraso com a seriedade que exigem.

Lembre-se, o diagrama é a fonte da verdade. Se o diagrama estiver errado, o projeto está errado. Mantenha o diagrama preciso, mantenha o projeto funcional e mantenha o sistema rodando suavemente.