No mundo da eletrônica digital e do design de sistemas, o tempo não é apenas uma dimensão; é um parâmetro crítico que determina se um circuito funcionará corretamente ou falhará catastroficamente.Diagramas de temposervem como a linguagem visual que engenheiros usam para comunicar como os sinais se comportam ao longo do tempo. Seja você quem está projetando uma interface de microcontrolador, depurando uma barramento de memória ou analisando a transmissão de dados de alta velocidade, entender esses diagramas é indispensável.

Este guia explora a mecânica dos diagramas de tempo, decompondo comportamentos complexos de sinais em componentes compreensíveis. Avançaremos desde definições fundamentais até técnicas avançadas de análise, garantindo que você tenha as ferramentas necessárias para interpretar formas de onda com precisão.

🔍 O que é um Diagrama de Tempo?

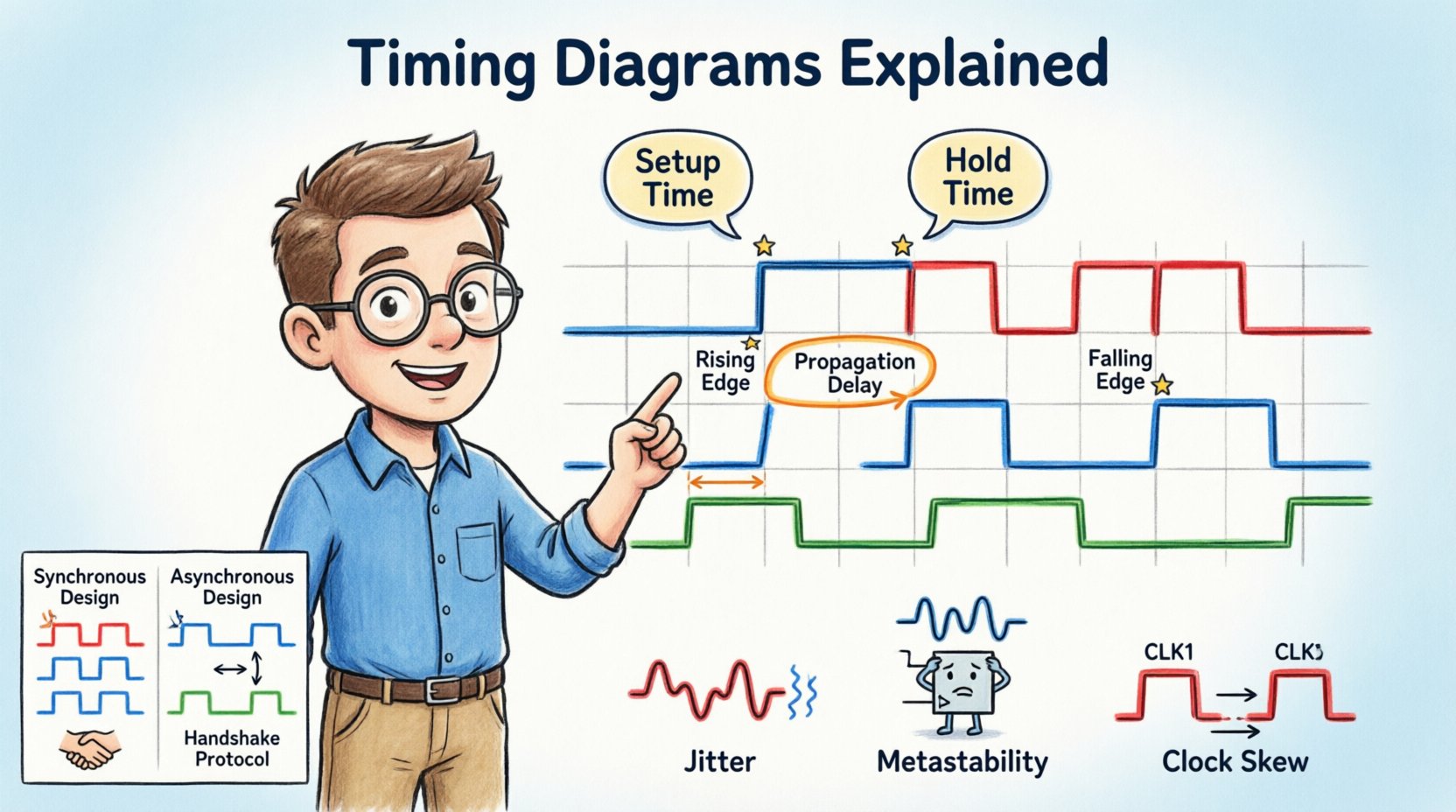

Um diagrama de tempo é uma representação gráfica da sequência de mudanças de sinal em um sistema digital. Diferentemente de um esquemático, que mostra como os componentes estão conectados, um diagrama de tempo ilustraquandoessas conexões mudam de estado. Ele mapeia a atividade dos sinais ao longo de um eixo horizontal do tempo, permitindo que os projetistas verifiquem se os dados estão estáveis antes de um flanco de clock ou se os sinais de controle são ativados na hora certa.

Esses diagramas são essenciais para:

- Verificar interações entre hardware e software.

- Depurar protocolos de comunicação.

- Garantir que os requisitos de tempo de setup e hold sejam atendidos.

- Documentar o comportamento do sistema para manutenção futura.

Sem uma compreensão clara do tempo, até mesmo um circuito logicamente correto pode falhar devido a corridas de sinal ou metastabilidade.

🛠️ Componentes Principais de um Diagrama de Tempo

Para ler um diagrama de tempo de forma eficaz, você deve identificar seus blocos fundamentais. Cada elemento carrega informações específicas sobre o estado e o fluxo do sistema digital.

1. O Eixo do Tempo

A linha horizontal representa a progressão do tempo. Ela geralmente flui da esquerda para a direita. Em documentos técnicos detalhados, esse eixo pode ser marcado com unidades de tempo específicas (nanossegundos, picossegundos) ou ciclos de clock.

2. Linhas de Sinal

Linhas verticais representam sinais individuais, como linhas de clock, barramentos de dados ou linhas de controle (como seleção de chip ou leitura/escrita). Cada linha corresponde a um nó específico no circuito.

3. Níveis Lógicos

Os sinais geralmente existem em um dos dois estados:

- Alto (Lógica 1 / VCC):Geralmente representado por uma linha na parte superior da trilha do sinal.

- Baixo (Lógica 0 / GND):Representado por uma linha na parte inferior da trilha do sinal.

Alguns sistemas usamLógica Ativa Baixalógica, em que o sinal realiza sua função quando a tensão é baixa. Nos diagramas, isso geralmente é indicado por um círculo no nome do sinal ou por uma notação específica.

4. Transições

As transições são os momentos em que um sinal muda de Alto para Baixo ou de Baixo para Alto.

- Aresta de Subida:Transição de Baixo para Alto. Crucial para disparar eventos.

- Aresta de Descida:Transição de Alto para Baixo. Usada em sequências de controle específicas.

- Disparado por Aresta:O sinal é avaliado apenas durante a transição, e não no estado estável.

⚙️ Parâmetros-Chave de Temporização

Um projeto digital preciso depende da quantificação da relação entre os sinais. Os seguintes parâmetros são a base da análise de temporização.

1. Atraso de Propagação (tpd)

Este é o tempo que leva para um sinal viajar da entrada de uma porta lógica ou componente até sua saída. Nenhum sinal muda instantaneamente; limitações físicas causam um atraso.

- Significância:Se o atraso for muito longo, a lógica subsequente pode receber os dados muito tarde, causando erros.

- Medição:Medido a partir do ponto de 50% da tensão da transição de entrada até o ponto de 50% da tensão da transição de saída.

2. Tempo de Preparação (tsu)

O tempo de preparação é a duração mínima durante a qual os sinais de dados devem permanecer estáveisantesde chegar uma borda do clock.

- Cenário:Se um flip-flop precisar que os dados estejam prontos 5 nanossegundos antes do clock disparar, esse é o tempo de preparação.

- Violação:Se os dados mudarem muito perto da borda do clock, o sistema não consegue capturar o valor corretamente.

3. Tempo de Manutenção (th)

O tempo de retenção é a duração mínima durante a qual os sinais de dados devem permanecer estáveisapósa chegada de uma borda do sinal de clock.

- Cenário:O flip-flop precisa “ver” os dados durante um curto período após o disparo para fixá-los com segurança.

- Violação:Se os dados mudarem imediatamente após a borda do clock, a entrada pode não ser fixada corretamente.

4. Desvio de clock

O desvio de clock ocorre quando o sinal de clock chega em componentes diferentes em tempos diferentes. Isso geralmente é devido às diferenças de comprimento de trilhas em uma placa de circuito impresso.

- Desvio Positivo:O clock chega mais tarde no destino.

- Desvio Negativo:O clock chega mais cedo no destino.

5. Jitter

O jitter é a variação de curto prazo dos instantes significativos de um sinal em relação às suas posições ideais no tempo. Ele adiciona incerteza à análise de tempo.

📊 Comparação: Projeto Síncrono vs. Assíncrono

Compreender a diferença entre essas duas filosofias de projeto é vital para interpretar corretamente os diagramas de tempo.

| Funcionalidade | Tempo Síncrono | Tempo Assíncrono |

|---|---|---|

| Sinal de Controle | Utiliza um clock global | Utiliza sinais de handshake |

| Previsibilidade | Altamente previsível | Variável com base na carga |

| Complexidade | Requer distribuição de clock | Requer lógica de handshake complexa |

| Consumo de Energia | Pode ser alto (toggling do clock) | Geralmente mais baixo (impulsionado pela atividade) |

| Diagrama de Temporização | Alinhado com as bordas do clock | Dependente da conclusão do estado anterior |

🧐 Como ler e analisar diagramas de temporização

Analisar uma onda exige uma abordagem sistemática. Siga estas etapas para garantir que você não perca detalhes críticos.

Passo 1: Identifique o Clock

Localize o sinal principal de clock. Este geralmente é a referência para todos os outros tempos. Em sistemas síncronos, cada transição de dados deveria idealmente ser referenciada a esta borda do clock.

Passo 2: Verifique falhas

Procure por pulsos curtos e indesejados (glitches) em linhas de sinal. Eles podem causar disparos falsos em portas lógicas. Em um diagrama limpo, as transições devem ser limpas, embora a captura no mundo real muitas vezes mostre ruídos.

Passo 3: Verifique as janelas de setup e hold

Desenhe linhas verticais imaginárias representando as janelas de setup e hold em torno da borda ativa do clock. Certifique-se de que o sinal de dados esteja estável dentro dessas zonas.

Passo 4: Verifique os sinais de controle

Garanta que sinais de controle como Chip Select (CS) ou Enable (EN) estejam ativos durante toda a duração da transferência de dados. Se um sinal de controle cair enquanto os dados ainda estão sendo enviados, ocorre corrupção.

Passo 5: Meça intervalos

Calcule o tempo entre eventos específicos. Por exemplo, meça a latência a partir do sinal “Request” até o sinal “Response”. Isso ajuda a validar o desempenho de acordo com as especificações.

🚀 Conceitos Avançados na Análise de Temporização

À medida que os sistemas ficam mais rápidos e complexos, diagramas de temporização básicos evoluem para requisitos sofisticados de análise.

1. Metastabilidade

A metastabilidade ocorre quando um flip-flop recebe uma entrada que viola os requisitos de tempo de setup ou hold. Em vez de se estabilizar em um valor claro de 0 ou 1, a saída entra em um estado indefinido por uma duração imprevisível.

- Causa:Muitas vezes acontece quando sinais assíncronos cruzam domínios de clock.

- Mitigação:Use cadeias de sincronização (vários flip-flops em série) para reduzir a probabilidade de metastabilidade.

- Visual:Em um diagrama de temporização, isso parece um sinal oscilando ou demorando um tempo anormalmente longo para se estabilizar.

2. Orçamentos de Tempo de Setup e Hold

Engenheiros calculam um orçamento de temporização para garantir que o sistema funcione na frequência máxima. Isso envolve subtrair todos os atrasos (fio, porta, skew de clock) do período do clock.

Se o atraso total exceder o tempo disponível, a frequência máxima de operação deve ser reduzida.

3. Temporização de Interface de Alta Velocidade

Interfaces como memória DDR ou PCIe exigem temporização extremamente precisa. Esses diagramas frequentemente incluem:

- Diagramas de Olho: Uma sobreposição de muitas transições de sinal para visualizar a qualidade do sinal.

- Distorção de Ciclo de Trabalho: Garantindo que os tempos alto e baixo estejam equilibrados.

- Alinhamento de Fase: Garantindo que dados e clock cheguem em sincronia em múltiplos bits.

4. Estados de Gerenciamento de Energia

Dispositivos modernos entram em modos de baixo consumo de energia. Os diagramas de temporização devem levar em conta a latência de ativação. Por exemplo, um sinal que habilita a alimentação a um periférico deve ocorrer antes que o dispositivo esteja pronto para receber dados.

📝 Melhores Práticas para Documentação

Documentação clara previne erros durante o desenvolvimento e depuração. Siga essas normas ao criar ou revisar diagramas de temporização.

- Escalas Consistentes: Use escalas de tempo consistentes em diagramas relacionados para permitir comparações fáceis.

- Rótulos Claros: Cada sinal deve ser rotulado com sua função e polaridade lógica (por exemplo,

RESET#para Ativo Baixo). - Níveis de Zoom: Forneça uma visão geral de alto nível e uma visualização ampliada das transições críticas (como janelas de setup/hold).

- Codificação por Cor: Use cores para distinguir entre diferentes domínios de tensão ou fontes de clock (por exemplo, Vermelho para Clock, Azul para Dados).

- Controle de Versão: Os requisitos de temporização mudam. Certifique-se de que os diagramas estejam versionados para corresponder à revisão do hardware.

🛠️ Armadilhas Comuns e Solução de Problemas

Mesmo engenheiros experientes enfrentam problemas de temporização. Aqui estão cenários comuns e como resolvê-los.

Armadilha 1: Ignorar o Atraso da Trilha

Trilhas de PCB têm comprimento físico, o que introduz atraso. Em frequências altas, alguns centímetros de fio podem equivaler a um ciclo de clock.

- Solução:Leve em conta o comprimento da trilha nos seus cálculos de orçamento de tempo.

Armadilha 2: Entradas Flutuantes

Entradas não conectadas podem flutuar para uma tensão intermediária, causando oscilação.

- Solução:Garanta que todas as entradas tenham resistores de pull-up ou pull-down definidos.

Armada 3: Condições de Corrida

Quando dois sinais mudam simultaneamente, a ordem de chegada determina o resultado.

- Solução:Use lógica de sincronização ou máquinas de estado para sequenciar eventos.

Armada 4: Sobretensão e Subtensão

Reflexões de sinal podem causar tensões que ultrapassam as linhas de alimentação (sobretensão) ou caírem abaixo do terra (subtensão).

- Solução:Implemente resistores de terminação adequados e correspondência de impedância.

🔗 Aplicações no Mundo Real

Diagramas de tempo são aplicados em diversas áreas da engenharia.

1. Interfaces de Memória

DRAM e SDRAM exigem sequências rigorosas de tempo para operações de leitura/escrita. A latência CAS e o atraso de RAS para CAS são parâmetros críticos visualizados nesses diagramas.

2. Comunicação com Microcontroladores

Protocolos como I2C, SPI e UART dependem de relações específicas de tempo entre as linhas de clock e dados. Por exemplo, no I2C, a linha de dados deve permanecer estável enquanto o clock está alto.

3. Sequenciamento de Fontes de Alimentação

Sistemas complexos exigem que as linhas de alimentação sejam ligadas em uma ordem específica. Diagramas de tempo garantem que a tensão do núcleo esteja estável antes que a tensão de I/O seja aplicada.

🎯 Resumo dos Pontos Principais

Dominar diagramas de tempo exige paciência e atenção aos detalhes. Os seguintes pontos resumem o conhecimento essencial para um projeto e análise eficazes.

- O Tempo é Crítico:A lógica digital depende de relações temporais precisas entre os sinais.

- Setup e Hold:São as duas restrições mais comuns que determinam a velocidade máxima de operação.

- Verificação Visual:Diagramas permitem que você veja conflitos potenciais antes da construção do hardware.

- O Contexto Importa: Sempre considere o ambiente físico (PCB, temperatura, tensão) que afeta o tempo de sinal.

- Padronização:Use símbolos e notação padrão para garantir clareza na comunicação entre equipes.

Ao aplicar esses princípios, você garante que seus sistemas digitais sejam robustos, confiáveis e eficientes. A capacidade de interpretar e criar esses diagramas é uma habilidade fundamental que diferencia projetos funcionais daqueles que falham no campo.

📈 Avançando

À medida que a tecnologia avança, as restrições de tempo tornam-se mais rigorosas. Sistemas modernos operam em velocidades de gigahertz, onde nanossegundos têm enorme importância. A aprendizagem contínua sobre integridade de sinal e fechamento de tempo é necessária para engenheiros que trabalham com hardware de ponta.

Comece analisando esquemas existentes e seus diagramas de tempo correspondentes. Pratique medir intervalos e identificar violações. Com o tempo, os padrões se tornarão intuitivos, permitindo que você antecipe problemas antes que se manifestem fisicamente.