В мире цифровой электроники и проектирования систем время — это не просто измерение; это критически важный параметр, определяющий, будет ли схема работать правильно или выйдет из строя катастрофически.Диаграммы временных интерваловслужат визуальным языком, который инженеры используют для передачи информации о поведении сигналов во времени. Независимо от того, разрабатываете ли вы интерфейс микроконтроллера, отлаживаете шину памяти или анализируете передачу данных высокой скорости, понимание этих диаграмм является обязательным.

В этом руководстве рассматриваются принципы работы диаграмм временных интервалов, сложное поведение сигналов разбивается на понятные компоненты. Мы пройдем от базовых определений до продвинутых методов анализа, обеспечивая вас инструментами для точной интерпретации форм сигналов.

🔍 Что такое диаграмма временных интервалов?

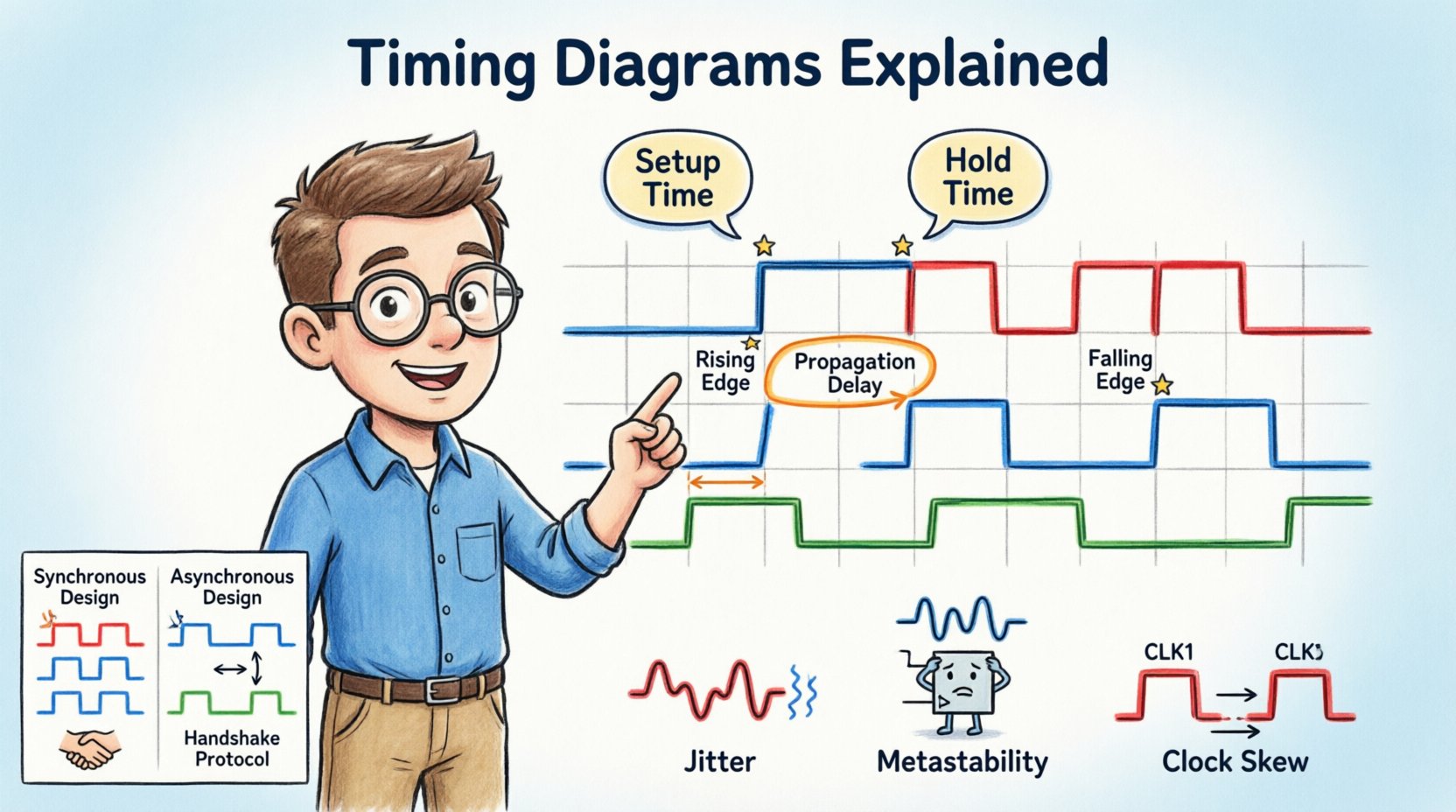

Диаграмма временных интервалов — это графическое представление последовательности изменений сигналов в цифровой системе. В отличие от схемы, которая показывает, как соединены компоненты, диаграмма временных интервалов иллюстрируеткогдасостояние этих соединений изменяется. Она отображает активность сигналов вдоль горизонтальной оси времени, позволяя разработчикам проверить, что данные стабильны до фронта тактового сигнала, или что управляющие сигналы активируются в нужный момент.

Эти диаграммы необходимы для:

- Проверки взаимодействия аппаратного и программного обеспечения.

- Отладки протоколов связи.

- Обеспечения выполнения требований по времени установки и удержания.

- Документирования поведения системы для последующего обслуживания.

Без четкого понимания временных параметров даже логически правильная схема может выйти из строя из-за гонок сигналов или метастабильности.

🛠️ Основные компоненты диаграммы временных интервалов

Чтобы эффективно читать диаграмму временных интервалов, необходимо определить её основные элементы. Каждый элемент несёт конкретную информацию о состоянии и потоке цифровой системы.

1. Ось времени

Горизонтальная линия представляет собой прогресс времени. Обычно она течёт слева направо. В подробных технических документах эта ось может быть обозначена конкретными единицами времени (наносекунды, пикосекунды) или циклами тактового сигнала.

2. Линии сигналов

Вертикальные линии представляют отдельные сигналы, такие как тактовые линии, шины данных или управляющие линии (например, выбор микросхемы или чтение/запись). Каждая линия соответствует определённой точке в схеме.

3. Уровни логики

Сигналы обычно находятся в одном из двух состояний:

- Высокий (логическая 1 / VCC):Часто обозначается линией в верхней части трека сигнала.

- Низкий (логический 0 / GND):Обозначается линией в нижней части трека сигнала.

Некоторые системы используютактивный низкийлогику, при которой сигнал выполняет свою функцию при низком напряжении. В диаграммах это часто обозначается кружком у названия сигнала или специальной маркировкой.

4. Переходы

Переходы — это моменты, когда сигнал изменяется с высокого на низкий или с низкого на высокий.

- Восходящий фронт: Переход от низкого к высокому. Критически важен для запуска событий.

- Нисходящий фронт: Переход от высокого к низкому. Используется для конкретных последовательностей управления.

- Срабатывание по фронту: Сигнал оценивается только во время перехода, а не в установившемся состоянии.

⚙️ Ключевые параметры временной задержки

Точное цифровое проектирование зависит от количественной оценки взаимосвязи между сигналами. Следующие параметры являются основой анализа временных характеристик.

1. Время распространения (tpd)

Это время, необходимое для прохождения сигнала от входа логического элемента или компонента до его выхода. Сигнал не может измениться мгновенно; физические ограничения вызывают задержку.

- Значение: Если задержка слишком велика, последующая логика может получить данные слишком поздно, что приведет к ошибкам.

- Измерение: Измеряется от точки 50% напряжения входного перехода до точки 50% напряжения выходного перехода.

2. Время установки (tsu)

Время установки — это минимальная продолжительность, в течение которой сигналы данных должны оставаться стабильнымидо прихода тактового фронта.

- Сценарий: Если триггер требует, чтобы данные были готовы за 5 наносекунд до срабатывания тактового сигнала, это и есть время установки.

- Нарушение: Если данные изменяются слишком близко к тактовому фронту, система не сможет корректно захватить значение.

3. Время удержания (th)

Время удержания — это минимальная продолжительность, в течение которой сигналы данных должны оставаться стабильнымипослеприхода фронта тактового сигнала.

- Сценарий:Триггер должен «увидеть» данные в течение короткого промежутка времени после срабатывания, чтобы надежно зафиксировать их.

- Нарушение:Если данные изменяются сразу после фронта тактового сигнала, вход может неправильно зафиксироваться.

4. Смещение тактового сигнала

Смещение тактового сигнала возникает, когда тактовый сигнал приходит в различные компоненты в разное время. Это часто связано с различиями в длине дорожек на печатной плате.

- Положительное смещение:Тактовый сигнал приходит позже в точке назначения.

- Отрицательное смещение:Тактовый сигнал приходит раньше в точке назначения.

5. Джиттер

Джиттер — это кратковременное отклонение значимых моментов сигнала от их идеального положения во времени. Он добавляет неопределенность в анализ временных параметров.

📊 Сравнение: Синхронный и асинхронный дизайн

Понимание различий между этими двумя философиями проектирования имеет решающее значение для правильной интерпретации временных диаграмм.

| Характеристика | Синхронное время | Асинхронное время |

|---|---|---|

| Управляющий сигнал | Использует глобальный тактовый сигнал | Использует сигналы согласования |

| Предсказуемость | Высокая предсказуемость | Переменная в зависимости от нагрузки |

| Сложность | Требует распределения тактового сигнала | Требует сложной логики согласования |

| Потребление энергии | Может быть высоким (переключение тактового сигнала) | Часто ниже (обусловлено активностью) |

| Схема временных диаграмм | Выровнено по краям тактового сигнала | Зависит от завершения предыдущего состояния |

🧐 Как читать и анализировать временные диаграммы

Анализ формы сигнала требует системного подхода. Следуйте этим шагам, чтобы убедиться, что вы не упустите важные детали.

Шаг 1: Определите тактовый сигнал

Найдите основной тактовый сигнал. Обычно он служит опорой для всех остальных временных параметров. В синхронных системах каждый переход данных должен быть идеально привязан к этому краю тактового сигнала.

Шаг 2: Проверьте наличие ложных импульсов

Ищите короткие, нежелательные импульсы (ложные импульсы) на линиях сигналов. Они могут вызвать ложные срабатывания в логических элементах. В чистой диаграмме переходы должны быть чистыми, хотя в реальных условиях захват часто показывает шум.

Шаг 3: Проверьте окна установки и удержания

Нарисуйте воображаемые вертикальные линии, представляющие окна установки и удержания вокруг активного края тактового сигнала. Убедитесь, что сигнал данных стабилен в этих зонах.

Шаг 4: Проверьте управляющие сигналы

Убедитесь, что управляющие сигналы, такие как выбор микросхемы (CS) или разрешение (EN), активны на протяжении всего времени передачи данных. Если управляющий сигнал падает, пока данные всё ещё передаются, происходит повреждение данных.

Шаг 5: Измерьте интервалы

Рассчитайте время между конкретными событиями. Например, измерьте задержку от сигнала «Запрос» до сигнала «Ответ». Это помогает проверить производительность по сравнению с техническими требованиями.

🚀 Расширенные концепции анализа временных параметров

По мере того как системы становятся быстрее и сложнее, базовые временные диаграммы трансформируются в сложные требования к анализу.

1. Метастабильность

Метастабильность возникает, когда триггер получает входной сигнал, нарушающий требования по времени установки или удержания. Вместо того чтобы перейти в четкое состояние 0 или 1, выход переходит в неопределенное состояние на непредсказуемое время.

- Причина:Часто происходит, когда асинхронные сигналы пересекают границы тактовых доменов.

- Снижение риска:Используйте цепочки синхронизаторов (несколько триггеров последовательно), чтобы снизить вероятность метастабильности.

- Визуально:На временной диаграмме это выглядит как колебание сигнала или чрезвычайно долгое время установления.

2. Бюджеты времени установки и удержания

Инженеры рассчитывают бюджет временных параметров, чтобы обеспечить работу системы на максимальной частоте. Это включает вычитание всех задержек (проводников, вентилей, дрейфа тактового сигнала) из периода тактового сигнала.

Если общее время задержки превышает доступное время, максимальная частота работы должна быть снижена.

3. Временные характеристики высокоскоростных интерфейсов

Интерфейсы, такие как память DDR или PCIe, требуют чрезвычайно точного временного управления. Эти диаграммы часто включают:

- Диаграммы глаза: Наложение многих переходов сигнала для визуализации качества сигнала.

- Искажение цикла управления: Обеспечение баланса между временем высокого и низкого уровней.

- Выравнивание фазы: Обеспечение синхронного поступления данных и тактового сигнала на нескольких битах.

4. Состояния управления питанием

Современные устройства переходят в режимы низкого энергопотребления. Диаграммы временных интервалов должны учитывать время пробуждения. Например, сигнал, подающий питание на периферийное устройство, должен быть активирован до того, как устройство будет готово принимать данные.

📝 Лучшие практики документирования

Четкая документация предотвращает ошибки во время разработки и отладки. Следуйте этим стандартам при создании или проверке диаграмм временных интервалов.

- Одинаковое масштабирование: Используйте одинаковые временные масштабы на связанных диаграммах для удобного сравнения.

- Четкие метки: Каждый сигнал должен быть помечен его функцией и логической полярностью (например,

RESET#для активного низкого уровня). - Уровни масштабирования: Предоставьте как общий обзор, так и увеличенное изображение критических переходов (например, окна установки/удержания).

- Цветовая маркировка: Используйте цвета для различения различных областей напряжения или источников тактового сигнала (например, красный — для тактового сигнала, синий — для данных).

- Контроль версий: Требования к временным интервалам изменяются. Убедитесь, что диаграммы версионированы в соответствии с версией аппаратного обеспечения.

🛠️ Распространенные ошибки и устранение неполадок

Даже опытные инженеры сталкиваются с проблемами временных интервалов. Вот распространенные сценарии и способы их решения.

Ошибка 1: Пренебрежение задержкой трассы

Трассы на печатной плате имеют физическую длину, что вызывает задержку. На высоких частотах несколько дюймов провода могут соответствовать одному тактовому циклу.

- Решение: Учитывайте длину следа при расчетах временного бюджета.

Опасность 2: Плавающие входы

Неподключенные входы могут плавать до промежуточного напряжения, вызывая колебания.

- Решение: Убедитесь, что все входы имеют определенные резисторы подтяжки к питанию или к земле.

Опасность 3: Гонки сигналов

Когда два сигнала изменяются одновременно, порядок поступления определяет результат.

- Решение: Используйте логику синхронизации или конечные автоматы для последовательного выполнения событий.

Опасность 4: Перегиб и недогиб

Отражения сигнала могут вызвать превышение напряжения выше питаний (перегиб) или падение ниже земли (недогиб).

- Решение: Реализуйте правильные резисторы окончания и согласование импеданса.

🔗 Реальные применения

Диаграммы временных отношений применяются в различных областях инженерии.

1. Интерфейсы памяти

DRAM и SDRAM требуют строгих временных последовательностей для операций чтения/записи. Задержка CAS и задержка от RAS до CAS являются критическими параметрами, визуализируемыми на этих диаграммах.

2. Коммуникация микроконтроллеров

Протоколы, такие как I2C, SPI и UART, зависят от конкретных временных отношений между линиями тактового сигнала и данных. Например, в I2C линия данных должна быть стабильной, когда тактовый сигнал находится в высоком состоянии.

3. Последовательность включения источников питания

Сложные системы требуют включения линий питания в определённой последовательности. Диаграммы временных отношений обеспечивают, что напряжение ядра стабильно до подачи напряжения I/O.

🎯 Основные выводы

Овладение диаграммами временных отношений требует терпения и внимания к деталям. Следующие пункты резюмируют основные знания для эффективного проектирования и анализа.

- Время имеет критическое значение:Цифровая логика зависит от точных временных отношений между сигналами.

- Подготовка и удержание: Это две наиболее распространённые ограничения, определяющие максимальную скорость работы.

- Визуальная проверка:Диаграммы позволяют увидеть потенциальные конфликты до сборки аппаратной части.

- Контекст имеет значение: Всегда учитывайте физическую среду (печатная плата, температура, напряжение), которая влияет на временные характеристики сигнала.

- Стандартизация:Используйте стандартные символы и обозначения, чтобы обеспечить ясность коммуникации между командами.

Применяя эти принципы, вы обеспечиваете надежность, стабильность и производительность своих цифровых систем. Способность интерпретировать и создавать такие диаграммы — фундаментальный навык, который отличает рабочие проекты от тех, которые выходят из строя на практике.

📈 Двигаясь вперед

По мере развития технологий временные ограничения становятся жестче. Современные системы работают на гигагерцевых частотах, где наносекунды имеют огромное значение. Инженерам, работающим над передовыми аппаратными решениями, необходимо непрерывно изучать вопросы целостности сигнала и завершения временных параметров.

Начните с анализа существующих схем и соответствующих им временных диаграмм. Упражняйтесь в измерении интервалов и выявлении нарушений. Со временем эти паттерны станут интуитивно понятными, позволяя вам предсказывать проблемы до их физического проявления.