在复杂的嵌入式工程世界中,精确性不仅仅是一种偏好;它是一种必需。时序图作为理解信号随时间交互的视觉蓝图。这些图形化表示将电压电平、时钟周期和数据转换映射到时间轴上。对于设计微控制器、传感器或通信接口的工程师而言,掌握时序图的阅读与绘制是确保系统可靠性的关键。

如果无法清晰地了解时间关系,硬件组件可能无法正常通信,从而导致数据损坏或系统崩溃。本指南探讨了时序图在嵌入式开发各个领域中的实际应用,深入分析了其用途,且不依赖于特定的软件工具。

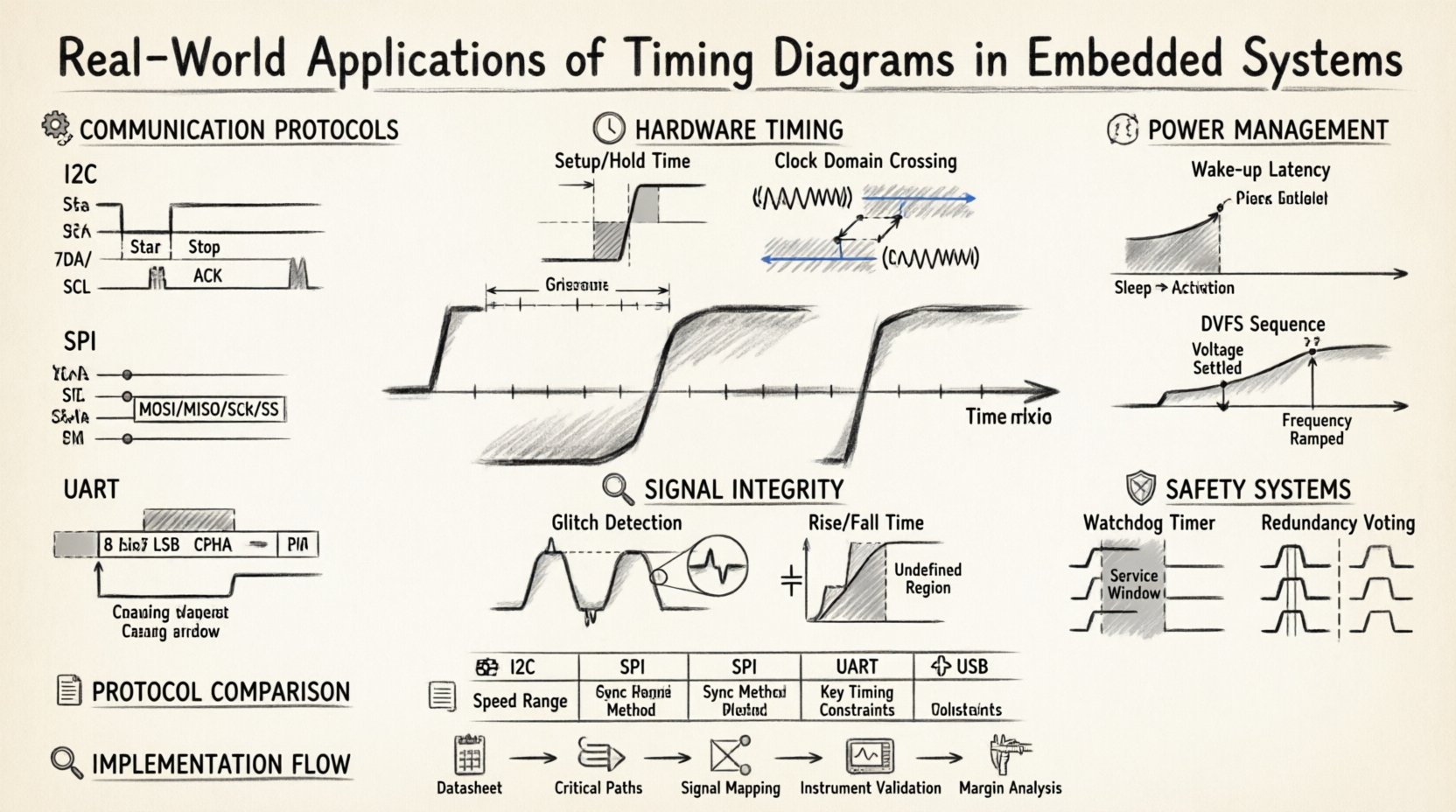

🔌 通信协议分析

串行通信是现代嵌入式系统的核心。数据很少停留在单个芯片内;它在处理器、内存和外设之间传输。时序图对于定义和验证这些交互至关重要。

集成电路总线(I2C)

I2C协议使用两线接口:串行数据(SDA)和串行时钟(SCL)。I2C的时序图揭示了数据传输所需的特定时序序列。

- 起始条件: 当SCL线保持高电平时,SDA线从高电平变为低电平。这表示总线开始一次传输。

- 地址帧: 发送的第一个字节包含目标设备的7位地址和一个读/写位。

- 应答: 接收方在第九个时钟脉冲期间将SDA线拉低,以确认接收。

- 停止条件: 当SCL线为高电平时,SDA线从低电平变为高电平,释放总线。

工程师利用这些图示来检测时钟拉伸等问题。如果从设备无法及时处理数据,它会将SCL线保持在低电平。时序图会显示这一延长,使设计者能够调整处理循环或缓冲区大小。

串行外设接口(SPI)

SPI是一种常用于高速通信的同步协议。它涉及四条线路:主出从入(MOSI)、主入从出(MISO)、串行时钟(SCK)和从设备选择(SS)。

- 时钟极性(CPOL): 决定时钟线的空闲状态。数据开始前,它是高电平还是低电平?

- 时钟相位(CPHA): 定义数据采样的时机。是在第一个还是第二个时钟边沿?

- 芯片选择时序: SS线在整个传输期间必须保持低电平。如果出现高电平跳变,传输将被中止。

理解这些时序阶段至关重要。主设备与从设备之间的CPOL或CPHA不匹配会导致垃圾数据。时序图能直观展示这些边沿,使硬件启动阶段更容易发现不匹配问题。

通用异步收发器(UART)

与SPI和I2C不同,UART不使用时钟线。同步依赖于双方约定的波特率。这里的时序图重点关注位持续时间和帧结构。

- 起始位: 一个低电平脉冲表示一个字节的开始。

- 数据位: 通常为8位,以最低有效位(LSB)优先的方式传输。

- 停止位: 高电平脉冲表示字节的结束。

时序图帮助工程师计算容差窗口。如果两个设备的时钟漂移过大,采样点会发生偏移,导致错误。该图展示了采样窗口,通常位于比特时间的中间位置。

⏱️ 硬件同步与建立时间

除了通信之外,时序图对于理解逻辑门和触发器之间的相互作用至关重要。数字逻辑依赖于精确的时序约束才能正确运行。

建立时间和保持时间

当数据进入寄存器或触发器时,必须满足相对于时钟边沿的特定时序要求。

- 建立时间: 数据必须保持稳定的最短时间在时钟边沿到达之后。

- 保持时间: 数据必须保持稳定的最短时间在时钟边沿到达之后。

如果信号违反了建立时间,寄存器可能会捕获错误的值。如果违反保持时间,可能发生亚稳态。时序图展示了数据信号相对于时钟边沿的时序关系,突出了数据变化被禁止的禁区。

时钟域交叉(CDC)

复杂系统通常以不同的时钟频率运行逻辑的不同部分。将数据从快速时钟域移动到慢速时钟域,或反之,会带来风险。

- 同步: 使用一串触发器,确保信号在使用前已稳定。

- 握手: 使用请求和应答信号来协调数据传输,而无需共享时钟。

CDC的时序图展示了握手过程。它确保接收域在确认之前数据已有效。这可以防止异步传输中的数据丢失。

🔍 调试与信号完整性

当嵌入式系统出现意外行为时,时序图通常是工程师首先查看的地方。它们提供了静态测试无法捕捉的信号行为历史记录。

识别毛刺

毛刺是信号线上短暂的、非预期的脉冲。它可能仅持续几纳秒,但足以触发触发器的状态变化。

- 竞争条件: 当事件顺序至关重要且时序过于紧凑时发生。

- 传播延迟: 信号通过逻辑门需要时间。时序图能清晰地展示这些延迟。

通过将预期的时序图与捕获的实际信号叠加,工程师可以精确地定位偏差发生的位置。这使得能够在固件或硬件设计中进行有针对性的修复。

噪声容限与上升/下降时间

实际信号并非理想的方波。由于走线中的电容和电感,信号具有上升和下降时间。

- 上升时间: 信号从低电平过渡到高电平所需的时间。

- 下降时间: 信号从高电平过渡到低电平所需的时间。

如果这些过渡过程过慢,信号可能在逻辑0和逻辑1之间的不确定电压区域停留过久。这可能导致触发多个时钟边沿或产生逻辑错误。时序图有助于测量这些斜率,以确保其符合接收芯片的规格要求。

💤 电源管理与低功耗状态

能效是电池供电嵌入式设备中的主要关注点。时序图在优化功耗方面发挥着作用。

唤醒延迟

当设备进入睡眠模式时,会停止时钟以节省电力。唤醒需要恢复时钟并稳定电压。

- 过渡时间: 从睡眠状态切换到激活状态所需的时间。

- 延迟: 唤醒事件发生与处理器开始执行代码之间的延迟。

电源启动时序图展示了触发信号与系统时钟稳定之间的延迟。对于延迟几毫秒就至关重要的实时应用而言,这一信息至关重要。

动态电压与频率调节(DVFS)

系统可根据负载调整电压和频率。时序图有助于验证不同性能状态之间的转换。

- 频率斜坡: 时钟是平滑变化还是突然变化?

- 电压稳定时间: 在应用新频率之前,电压是否已稳定?

DVFS 过程中若顺序错误,可能导致电压下降或逻辑错误。时序图提供了必要的序列验证,以确保转换过程安全。

🛡️ 安全关键系统

在汽车、医疗和工业应用中,安全至关重要。时序图用于验证安全机制是否在规定的时限内正常工作。

看门狗定时器

如果软件卡死,看门狗定时器将重启系统。时序图定义了超时周期。

- 超时周期: 两次复位之间允许的最大时间。

- 服务窗口: 软件重置计时器所需的时间。

如果服务窗口过长,看门狗可能会不必要的触发。如果过短,慢速中断可能导致误复位。该时序图确保时序符合安全标准要求。

冗余与投票

某些系统使用多个处理器对正确输出进行投票。时序图确保所有处理器同时到达投票阶段。

- 同步: 所有通道必须对其数据。

- 超时: 如果某个通道延迟,系统必须检测到差异。

在制动控制或转向系统中,这至关重要,因为延迟可能带来危险。时序图映射每个通道的延迟,以确保投票逻辑正确运行。

📋 协议对比概览

下表总结了常见嵌入式接口的关键时序特性,以协助选择和设计。

| 协议 | 速度范围 | 同步方法 | 典型应用场景 | 关键时序约束 |

|---|---|---|---|---|

| I2C | 100 kHz 至 3.4 MHz | 共享时钟 | 传感器、EEPROM | 时钟拉伸 |

| SPI | 1 MHz 至 50 MHz+ | 主时钟 | 闪存、显示器 | 芯片选择建立时间 |

| UART | 9600 至 921600 bps | 异步 | 调试、GPS、蓝牙 | 波特率容差 |

| USB | 1.5 Mbps 至 20 Gbps | 基于数据包 | 外设、存储 | 令牌/握手时序 |

🛠️ 实际实施步骤

创建时序图需要系统化的方法。它从理解规范开始,到验证结束。

- 查阅数据手册:每个组件都有时序部分。请查找交流特性表格。

- 识别关键路径:确定哪些信号决定了系统的最大速度。

- 绘制依赖关系:绘制信号之间的关系。哪一个触发另一个?

- 使用仪器进行验证:使用逻辑分析仪或示波器捕获实际波形。

- 分析余量:确保信号之间有足够的时序余量,以应对温度和电压的变化。

文档至关重要。一份标注清晰的时序图可作为未来维护的参考。它解释了为何添加了某些延迟,或为何选择了特定的上拉电阻。

🚀 高级考虑因素

随着系统变得越来越复杂,时序分析需要更深入的关注。

抖动和相位噪声

时钟并非完全稳定。抖动是指时钟边沿与其理想位置的偏差。时序图展示了多个周期内边沿位置的变化。

- 周期抖动:时钟周期的变化。

- 周期间抖动:从一个周期到下一个周期的变化。

高抖动会降低建立时间和保持时间的余量。在DDR内存等高速接口中,这可能导致读/写错误。时序图有助于量化这种抖动,以确保其保持在可接受范围内。

热效应

温度会影响晶体管的运行速度。当芯片发热时,信号传输速度会变慢。

- 最坏情况分析:针对最高工作温度进行设计。

- 热节流: 确保系统在高速运行期间不会超过安全的热极限。

在室温下绘制的时序图在85°C时可能不再适用。工程师必须考虑这些热漂移,以确保系统的鲁棒性。

📝 最后思考

时序图不仅仅是绘图;它们是同步的语言。它们架起了理论逻辑与物理现实之间的桥梁。在硬件与软件交织的嵌入式系统中,对信号时序的清晰理解可以避免昂贵的重新设计,并确保可靠性。

无论你是调试通信协议、优化功耗,还是确保关键系统中的安全性,这些图表都能提供做出明智决策所需的清晰度。通过关注建立时间、传播延迟和信号完整性,工程师可以构建在现实条件下表现一致的系统。

投入时间理解时序关系,将在稳定性和性能上获得回报。随着技术的进步,这些原理依然不变。时间是恒定的,掌握其测量方法是成功实现嵌入式设计的关键。