工程沟通高度依赖视觉精度。在讨论系统交互、信号传播或数据流时,一个结构良好的时序图就是通用语言。这些图捕捉了事件随时间变化的关系,使工程师能够有效诊断问题、验证逻辑并记录系统行为。然而,杂乱、模糊或比例不当的图表可能导致代价高昂的误解。本指南概述了创建清晰传达技术真实性的图表的基本标准。

📊 理解时序图的基本原理

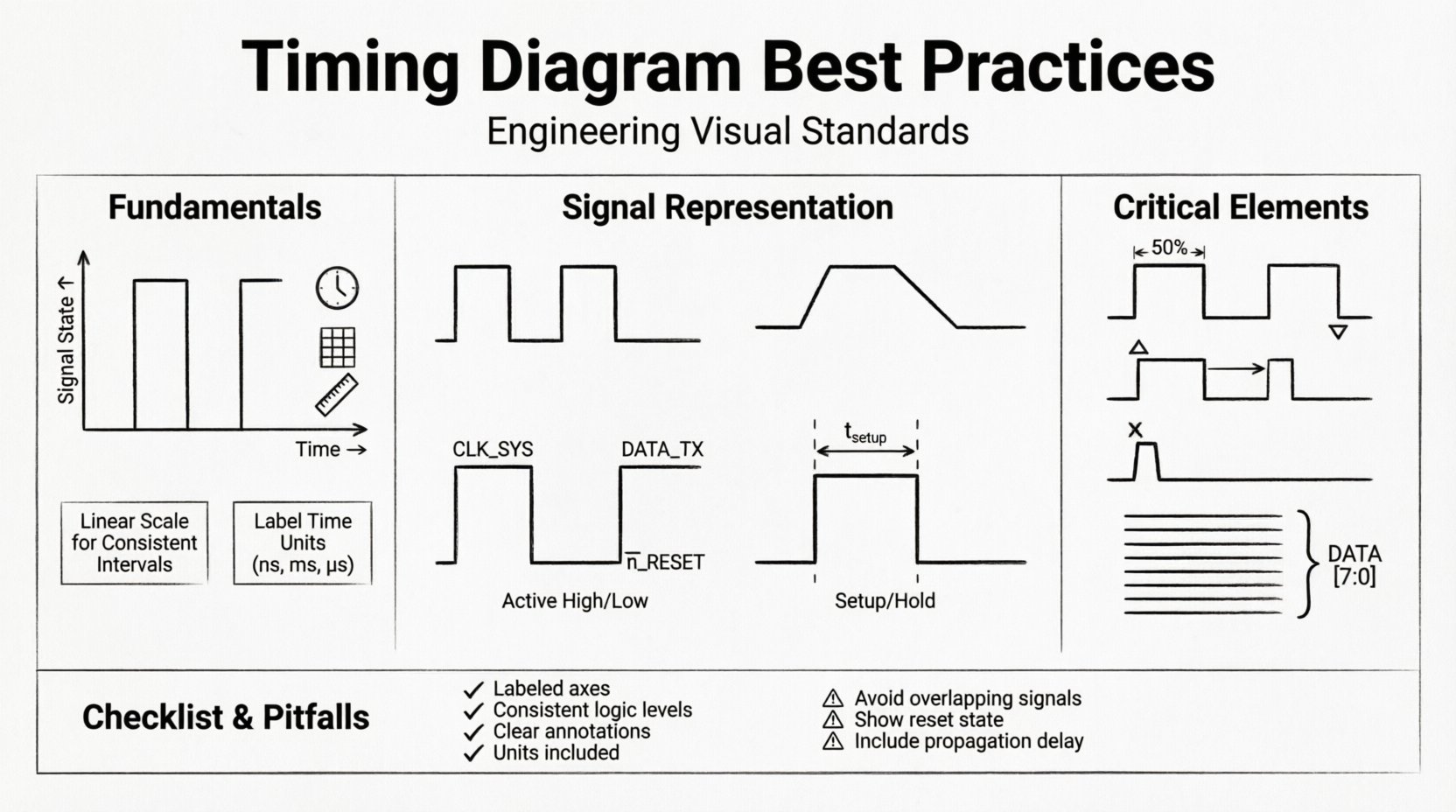

时序图是信号随时间变化状态的图形化表示。它不仅仅是一幅图,更是一种规范。无论你是在处理硬件接口、嵌入式系统还是软件协议,其基本原理始终一致:时间水平流动,信号状态垂直绘制。在此背景下,清晰性不是奢侈品,而是安全与可靠性的必要条件。

在制作这些视觉图表时,目标是减轻读者的认知负担。他们不应需要猜测时钟从何处开始、哪条线代表数据,或电压阈值是多少。每一个元素都必须有其明确用途。

- 时间轴: 水平方向表示时间的推进。根据所记录事件的不同,可以采用线性或对数刻度。

- 信号线: 垂直方向表示信号的状态,例如高/低、1/0或电压电平。

- 事件: 时间上的特定点,发生状态变化,例如边沿、脉冲或数据传输。

📏 设置你的画布与比例

清晰图表的基础是网格。如果没有一致的比例,事件之间的关系就会失真。在某一缩放级别下看起来正确的草图,在另一级别下可能暴露出关键的时序违规。

1. 定义时间比例

时间比例应根据系统中最快的事件来选择。如果你在记录微秒级的交互,用毫秒绘制时间轴会掩盖细节。相反,如果事件跨越数秒,使用微秒比例则会产生不必要的噪声。务必在轴上清晰标注时间单位。

- 线性比例: 用于一致的时间间隔。这是大多数协议文档的标准。

- 对数比例: 很少使用,但在事件跨越数量级时(例如启动延迟与处理时间)是必需的。

2. 网格线与参考点

网格线有助于眼睛追踪图表中的时间间隔。粗网格线应标记主要单位(例如10ms),细网格线标记次要单位(例如1ms)。这种视觉层次结构可防止读者迷失方向。

确保垂直网格线与关键事件对齐。如果时钟边沿恰好落在网格线上,它就为读取建立时间和保持时间提供了自然锚点。如果事件代表真实世界测量值,不要强行将其塞入网格;相反,应调整网格或使用注释来显示偏移量。

⚡ 准确表示信号

信号的绘制方式决定了其被如何解读。上升沿意味着从低到高的转换,但该转换的速度和形状可能承载关于信号完整性的信息。

1. 信号状态与电平

明确界定逻辑状态的定义。在数字逻辑中,通常是0(低)和1(高)。在模拟或混合信号环境中,需要使用电压电平(例如0V到5V)。使用不同的线型来区分:

- 高电平有效: 当信号线处于上电平状态时,信号为真。

- 低电平有效: 当信号线处于下电平状态时,信号为真(通常在信号名称上方加一横线表示)。

2. 边缘表示

边缘是图表中最重要的部分。它们表示状态发生变化的确切时刻。对于理想转换,使用锐利的实线。如果需要表示物理的上升速率或上升时间,请将其画成倾斜的线条,而不是垂直的尖峰。

除非专门用于记录噪声或毛刺,否则应避免使用锯齿状线条。干净的线条表示稳定;锯齿状线条表示干扰。绘制线条时应有意识地选择形状。

3. 信号命名规范

信号名称不仅仅是一个标签;它是一种定义。避免使用诸如Signal_A或Wire_1之类的通用名称。相反,应使用描述功能的名称,例如CLOCK_SYS或DATA_TX.

- 前缀: 使用标准前缀来表示信号类型(例如,

N表示负逻辑,CLK表示时钟)。 - 大小写:常量和信号使用大写字母,变量(如适用)使用大小写混合。

- 一致性: 确保图表中的名称与代码或数据手册中的名称完全一致。

⏱️ 时钟与同步

时钟驱动同步系统的时序。错误地表示时钟会使整个图表失效。时钟信号通常是读者首先检查的参考点。

1. 占空比与周期

除非系统明确要求可变时序,否则应以一致的占空比绘制时钟信号。如果占空比不是50%,请标注高电平和低电平的持续时间。周期(一个完整周期所需的时间)应明确标示。

对于可变频率系统,不要假设线段长度恒定就代表时间恒定。如果周期差异显著,请分别标注每个周期。

2. 边沿触发

标明系统是在上升沿(正)还是下降沿(负)触发。可以在边沿处使用箭头或小三角形。这对于理解数据何时被采样至关重要。

- 上升沿:用一个小三角形指向上方标记。

- 下降沿:用一个小三角形指向下方标记。

3. 抖动与相位

在高速系统中,抖动(时序变化)是一个已知因素。如果你绘制的是理论理想情况,直线即可。如果你在记录实测行为,则应使用阴影区域或多条轨迹来表示波动。多个时钟之间的相位关系应明确说明。

🔄 处理数据转换

数据信号通常比时钟信号更复杂。它们根据系统状态而变化。正确记录这些转换需要关注数据与时钟之间的关系。

1. 建立时间和保持时间

这些是可靠数据捕获的关键约束。建立时间是指时钟边沿前数据必须保持稳定的持续时间。保持时间是指时钟边沿后数据必须保持稳定的持续时间。可将它们可视化为相对于时钟边沿的时间窗口。

绘制垂直虚线以表示建立时间和保持时间窗口。用时间单位标注持续时间(例如,t_setup = 5ns)。这可以直观展示系统正常运行所具备的余量。

2. 亚稳态

当信号跨越时钟域时,可能发生亚稳态。这是一种信号既非完全高电平也非完全低电平的状态。可在时序窗口中用虚线或特定阴影来表示。记录这一点可提醒读者,该信号可能需要比平常更长的时间才能稳定下来。

3. 尖峰与噪声

意外脉冲,即尖峰,可能导致逻辑错误。如果尖峰是已知问题,应将其绘制为一个宽度未达到接收逻辑最小脉宽要求的窄脉冲。不要隐藏这些现象;它们往往是间歇性故障的根本原因。

🏷️ 注释与标注

图表中的文字具有重要性。文字过多会使图表难以阅读;标注不足则会导致含义模糊。应通过有策略的布局来找到平衡。

1. 文字位置

将文字放置在信号相关部分附近,但避免与信号线重叠。如果信号过于密集,无法直接在上方或下方放置文字,可使用引导线(连接文字与信号的细线)。

2. 单位与符号

始终包含单位。时间单位应为秒、毫秒或纳秒。电压单位应为伏特。不要依赖读者猜测。在展示逻辑方程的同时,应使用标准符号表示逻辑运算(例如,! 表示非,& 表示与)

3. 可读性

字体大小很重要。在打印文档或屏幕上,文字必须无需缩放即可清晰阅读。如果图表较为复杂,可考虑将其拆分为多个视图:一个高层次概览和一个特定事件的详细局部放大图。

🚫 应避免的常见错误

即使是经验丰富的工程师在绘制这些图表时也会出错。了解常见的错误可以节省数小时的调试时间。

- 忽略传播延迟:信号需要时间通过导线和逻辑门。如果信号在点A发生变化并到达点B,请画出延迟。点B处的垂直线意味着瞬时传输,这是物理上不可能的。

- 逻辑电平不一致:确保高电平和低电平的定义在整个图表中保持一致。这会令人困惑且危险。

- 信号重叠:如果两个信号必须交叉,请确保它们能够清晰区分。如果输出介质允许,可使用不同的线宽或颜色。

- 遗漏复位状态:系统通常从特定状态开始。在时钟启动前展示初始状态。这可以避免对零时刻信号行为产生混淆。

🧠 高级注意事项

随着系统变得越来越复杂,时序图必须随之演进,以应对多通道和异步场景。

1. 多通道时序

在处理总线(如数据总线)时,将相关信号分组。使用括号表示上方的线条代表总线宽度(例如“DATA[7:0])。展示整个组的转换,以表示并行传输。

2. 异步握手

并非所有系统都使用全局时钟。握手协议依赖于请求和应答信号。请用箭头清晰地表示握手方向。展示系统等待直到接收到信号的等待状态。

3. 电源管理状态

现代系统会进入低功耗模式。在时序图中标注这些转换。一个信号可能变低以表示睡眠模式,但时钟可能停止或变慢。应将电源状态与时间状态一并记录。

✅ 审查检查清单

在最终确定图表前,请逐一核对本检查清单,以确保符合最佳实践。

| 检查项目 | 标准 |

|---|---|

| 时间轴 | 刻度是否为线性并带有单位标注? |

| 信号名称 | 所有信号是否都功能明确且命名一致? |

| 时钟边沿 | 上升/下降沿是否清晰标记? |

| 转换 | 建立/保持时间是否可见并已标注? |

| 延迟 | 相关位置是否包含了传播延迟? |

| 注释 | 文字是否清晰可读且无重叠? |

| 单位 | 所有测量值是否都附带了单位(如ns、V等)? |

| 初始状态 | 开始时是否显示复位或空闲状态? |

| 清晰度 | 同行工程师能否在不提问的情况下理解此图? |

📝 关于文档的最终思考

时序图的质量反映了其背后工程的质量。清晰的图表有助于硬件与软件团队之间的协作,减少调试时间,并确保未来的维护人员能够理解系统的行为。它是一种揭示真相的工具,而不仅仅是图示。

注重精确性而非美观性。虽然美观的图表令人愉悦,但正确的图表才是必不可少的。花时间验证测量值,标注每一个约束条件,并确保你的视觉语言与技术规范保持一致。遵循这些实践,才能确保时序信息在整个产品生命周期中准确无误地保留。

请记住,图表是一种合同。它定义了系统的行为方式。当你画出一条线时,你就在对信号行为做出承诺。请确保这一承诺清晰、准确且无歧义。

采用这些标准能够提升你文档的专业性。它向你的团队和利益相关者表明,你重视可靠性与清晰度。在复杂的系统设计世界中,一张优秀的图表往往是成功发布与反复问题之间的关键区别。

🔧 结论

制作有效的时序图需要对布局、标注和表现方式采取严谨的方法。通过优先考虑清晰性、一致性和技术准确性,工程师可以生成可靠的视觉参考,用于开发和维护。遵循关于信号表示、时钟同步和注释的指南,以确保你的文档能够经受住时间和复杂性的考验。