数字系统依赖于精确的同步才能正常运行。当信号在错误的时刻到达时,就会发生逻辑故障,导致行为不可预测。理解如何分析和纠正这些问题,对学习数字逻辑、计算机工程或电子学的任何人来说都至关重要。本指南涵盖了识别和解决时序电路与数据传输中常见时序问题的核心概念和实际步骤。

理解时钟信号与边沿 ⏱️

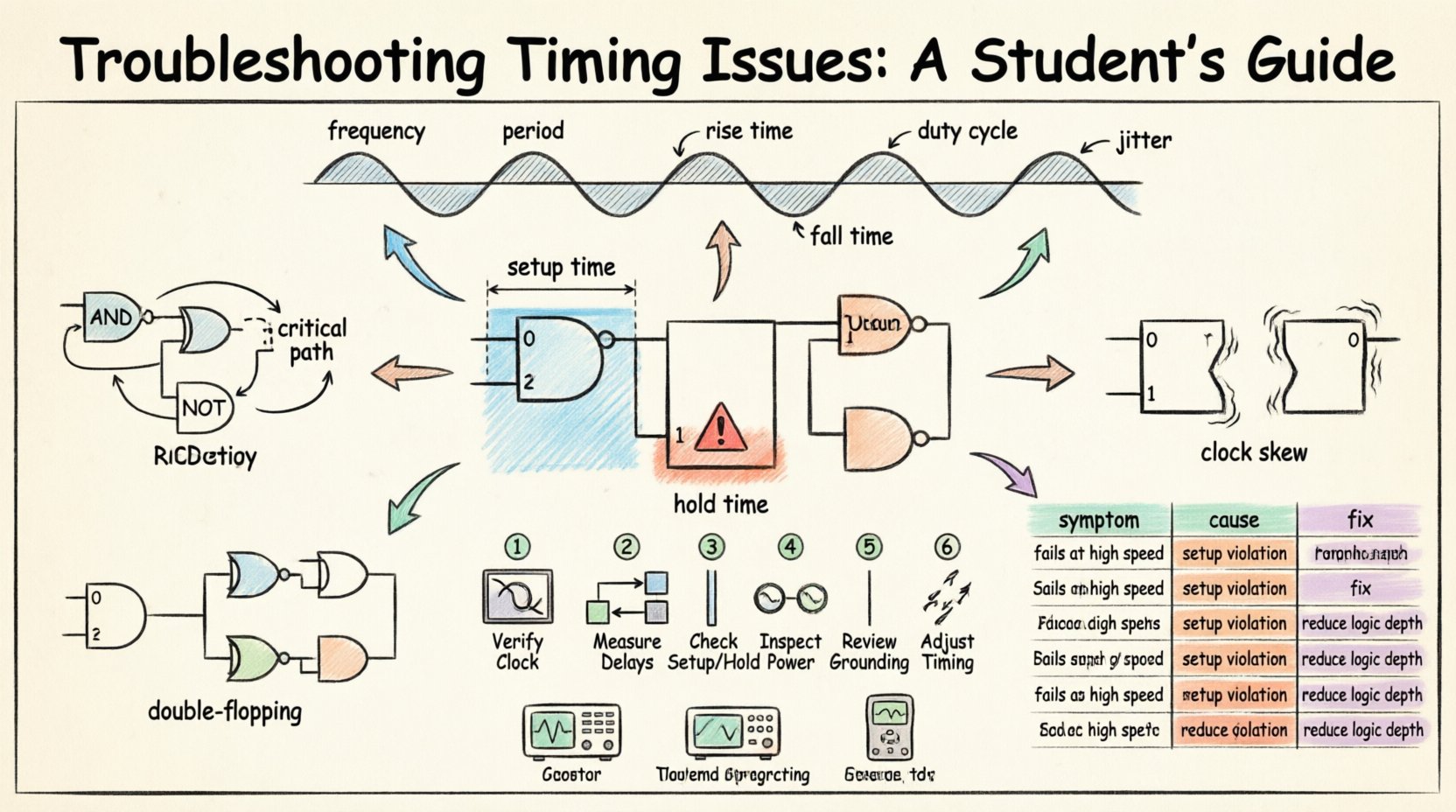

在大多数数字设计的核心,是时钟信号。这个周期性波形决定了数据采样的时刻以及状态变化的时刻。排查问题通常从验证这一基本信号的完整性开始。

- 频率与周期: 时钟频率决定了运行速度。周期是完整一个循环的时间长度。如果电路需要100 MHz的时钟,周期就是10纳秒。这里的任何偏差都会影响所有下游逻辑。

- 上升与下降时间: 理想的方波是理论上的。实际信号具有有限的上升和下降时间。如果转换过慢,信号可能在未定义电压区域停留过久,导致多次翻转或逻辑错误。

- 占空比: 这是信号处于高电平的时间与总周期的比值。50%的占空比是标准值,但某些设计需要非对称周期。偏差可能导致建立时间或保持时间要求的时序裕量失衡。

检查电路时,使用示波器或逻辑分析仪观察时钟波形。注意是否存在噪声尖峰、振铃或过大的抖动。抖动指的是时钟边沿相对于其理想时间位置的偏差。高抖动会减少数据稳定所需的可用有效时序裕量。

建立时间与保持时间违规 ⚠️

这是在时序逻辑设计中最常见的时序违规。触发器和锁存器对数据相对于时钟边沿必须保持稳定的时间有特定要求。

建立时间

建立时间是指在时钟边沿之前,数据必须保持稳定的最短时间。如果数据在时钟边沿附近变化过快,触发器可能无法捕获正确的值。

- 约束条件: 驱动触发器的组合逻辑的传播延迟必须小于时钟周期减去建立时间。

- 症状: 系统在低频下可能正常工作,但随着速度提升会失效。输出中常出现随机的位错误。

- 解决方法: 减少寄存器之间的逻辑深度,增加时钟周期,或使用更快的元器件。

保持时间

保持时间是指在时钟边沿之后,数据必须保持稳定的最短时间。如果数据在时钟边沿之后过快变化,触发器可能会丢失捕获的值。

- 约束条件: 组合逻辑的传播延迟必须大于目标触发器的保持时间。

- 症状: 保持违规通常与频率无关。这是因为延迟是绝对的,而非相对于周期而言。

- 解决方法: 在数据路径中添加延迟缓冲器以减慢信号速度,或重新设计逻辑以减少延迟。

区分这两者至关重要。建立时间违规与频率相关,而保持时间违规则与路径相关。一个常见错误是试图通过降低时钟频率来修复保持时间违规;这不仅无效,还可能使问题更严重。

传播延迟与路径分析 📉

信号不会瞬间传播。每根导线、门电路和组件都会引入延迟。分析这些延迟对于确保数据按时到达至关重要。

- 组合逻辑延迟: 这是指信号通过与门、或门和非门等逻辑门所需的时间。较长的门电路链会产生显著的延迟。

- 互连延迟: 在物理电路板上,导线具有电容和电阻。更长的走线会引入更大的延迟。这通常被建模为RC网络。

- 引脚到引脚延迟: 从组件的时钟输入到数据输出之间的时间。这通常在数据手册中给出。

在排查问题时,应绘制出关键路径。这是两个时序元件之间的最长延迟路径。如果关键路径超过时钟周期,设计将失败。为了找到它,计算所有可能路径的延迟总和,并确定最大值。

时钟偏移与抖动 📶

即使时钟源是完美的,信号也可能在不同时间到达各个组件。这种现象被称为偏移。

- 时钟偏移: 当时钟信号到达不同触发器的路径长度不同时,就会发生这种情况。正偏移会延迟捕获时钟,放宽建立时间但收紧保持时间;负偏移则收紧建立时间但放宽保持时间。

- 时钟抖动: 时钟边沿时间的短期波动。抖动会减少用于数据建立的可用时序预算。

- 漂移: 由于温度或电源波动,时钟频率随时间发生的缓慢变化。

在复杂设计中,偏移通常通过时钟树综合来管理。在学生项目中,通常通过均匀布线时钟走线并保持其较短来最小化偏移。如果怀疑存在偏移,应同时在电路的多个点测量时钟。

亚稳态与异步输入 🌀

当数据在时钟边沿同时发生变化时,触发器会进入亚稳态。它不会立即稳定到0或1,而是在中间电压电平上徘徊。

- 风险: 亚稳态可能在系统中传播,导致难以复现的逻辑错误。

- 异步信号: 来自外部开关或通信端口的输入通常与内部时钟不同步。这些信号必须进行同步。

- 双触发器法: 一种常见的解决亚稳态的技术是将信号依次通过两个触发器。第一个捕获亚稳态,第二个在下一个周期中将其解决。

始终将异步输入视为潜在的亚稳态源。不要将其直接连接到需要严格时序的逻辑电路。应使用同步器电路,以确保在不同时钟域之间安全传输数据。

逐步排查工作流程 🛠️

当出现时序问题时,应遵循结构化的方法来定位原因。随意更改通常不会取得成效。

- 验证时钟: 检查频率、占空比和幅度。确保信号稳定且干净。

- 测量延迟: 使用逻辑分析仪捕获输入和输出波形。测量该路径的实际传播延迟。

- 检查建立时间和保持时间: 根据测量的延迟计算该路径是否满足建立时间和保持时间约束。

- 检查电源: 电压下降会减慢门电路的速度。确保电源稳定并能提供足够的电流。

- 检查接地: 接地不良会引入类似时序错误的噪声。检查是否存在地环路和共用返回路径。

- 调整时序: 如果设计具有灵活性,可调整时钟频率或添加缓冲器以平衡路径。

在此过程中,文档记录至关重要。记录波形和测量数据。这些数据有助于将预期行为与实际性能进行对比。

常见错误参考表 📊

可使用此表作为诊断特定症状的快速参考。

| 观察到的症状 | 可能原因 | 建议操作 |

|---|---|---|

| 系统在高速下失效 | 建立时间违规 | 减少逻辑深度或增加时钟周期 |

| 系统在低速下失效 | 保持时间违规 | 在数据路径中添加延迟缓冲器 |

| 随机位翻转 | 信号噪声或抖动 | 检查屏蔽和电源稳定性 |

| 输出挂起或复位 | 亚稳态 | 实施同步链 |

| 行为不一致 | 时钟偏斜 | 平衡时钟走线长度 |

| 完全无输出 | 时钟未使能 | 验证时钟分配和使能信号 |

工具与仪器 📏

虽然仿真工具很有用,但物理验证通常需要特定的硬件。正确使用这些仪器是故障排查技能的一部分。

- 示波器:用于观察电压电平和信号波形。使用高阻抗探头以避免加载电路。

- 逻辑分析仪:更适合数字信号。它可以随时间捕获逻辑状态(0或1)。它能根据特定模式触发,以隔离错误。

- 频率计:当无法使用示波器时,用于验证时钟源的确切频率。

确保探头正确补偿。未补偿的探头会扭曲信号波形,导致对上升时间和延迟的错误判断。

信号完整性最后的考虑事项 🔒

时序问题通常是更广泛的信号完整性问题的表现。随着电路速度的提升,电路板的物理特性变得更为重要。

- 串扰:相邻导线上的信号可能会相互干扰。应将高速线路与敏感线路分开。

- 阻抗匹配:如果走线阻抗与驱动器或接收器不匹配,就会产生反射。这些反射可能看起来像时序延迟。

- 热效应:随着元器件发热,其电气特性会发生变化。这可能会改变传播延迟,并导致负载下的时序故障。

时序设计需要整体视角。这不仅仅是关于逻辑门,更关乎信号所经过的物理介质。遵循这些原则,学生可以构建出在各种条件下都能可靠运行的稳健系统。

定期使用实际硬件进行练习有助于内化这些概念。理论提供框架,但动手调试能培养解决复杂时序问题所需的直觉。