In der komplexen Landschaft der digitalen Hardware-Entwicklung ist Klarheit entscheidend. Ingenieure und Designer verlassen sich auf visuelle Darstellungen, um zu kommunizieren, wie Signale im Laufe der Zeit reagieren. Das Zeitdiagramm ist eines der wichtigsten Werkzeuge für diesen Zweck. Es wandelt abstrakte Logik in eine visuelle Zeitachse um und zeigt die Wechselwirkungen zwischen hohen und niedrigen Zuständen über verschiedene Komponenten hinweg auf. Sobald Systeme jedoch an Komplexität gewinnen, können diese Diagramme überwältigend werden. Dieser Leitfaden untersucht eine modulare Strategie, um Zeitdiagramme effektiv zu analysieren und zu entziffern, wodurch Präzision und Zuverlässigkeit bei der Hardware-Verifikation gewährleistet werden.

Das Verständnis des Daten- und Steuersignalflusses ist entscheidend, um funktionale Fehler zu vermeiden. Egal, ob Sie eine Mikrocontroller-Schnittstelle oder ein Hochgeschwindigkeitskommunikationsprotokoll entwerfen – die Fähigkeit, solche Diagramme zu lesen und zu erstellen, unterscheidet eine robuste von einer anfälligen Architektur. Durch die Anwendung einer strukturierten, modularen Perspektive können Teams die Komplexität bewältigen und das Risiko von Zeitverletzungen reduzieren.

Grundlagen der Zeitdiagramme verstehen ⏱️

Ein Zeitdiagramm ist eine grafische Darstellung, wie Signale im Laufe der Zeit ihren Zustand wechseln. Es stellt die Zeit auf der horizontalen Achse und die Signalzustände auf der vertikalen Achse dar. Diese visuelle Darstellung ermöglicht es Ingenieuren, die Beziehung zwischen verschiedenen Signalen innerhalb einer digitalen Schaltung zu überprüfen. Das primäre Ziel ist es, sicherzustellen, dass die Daten stabil und gültig sind, wenn sie von der empfangenden Komponente abgefragt werden.

Mehrere wesentliche Elemente bilden die Grundlage jedes Zeitdiagramms:

- Signallinien:Horizontale Linien stellen einzelne Leitungen oder Bussysteme dar, die spezifische Signale wie Takt, Daten oder Steuerung übertragen.

- Zeitachse:Die horizontale Fortschreitung zeigt den Ablauf der Zeit an, meist in Nanosekunden oder Taktzyklen markiert.

- Logische Zustände:Signale sind typischerweise binär und werden als Hoch (1) oder Niedrig (0) dargestellt. Manchmal werden auch undefinierte Zustände oder Hochwiderstandszustände angezeigt.

- Übergänge:Senkrechte Linien zeigen den Moment an, in dem ein Signal von einem Zustand in einen anderen wechselt, beispielsweise bei steigenden oder fallenden Flanken.

- Anmerkungen:Textmarkierungen definieren oft spezifische Einschränkungen, Verzögerungen oder funktionale Blöcke innerhalb des Diagramms.

Ohne ein klares Verständnis dieser Grundlagen wird die Interpretation komplexer Wechselwirkungen schwierig. Ein Zeitdiagramm ist nicht einfach nur eine Zeichnung; es ist ein Vertrag zwischen Sender und Empfänger. Es legt die Regeln fest, nach denen Daten übertragen werden müssen, um korrekt verarbeitet zu werden.

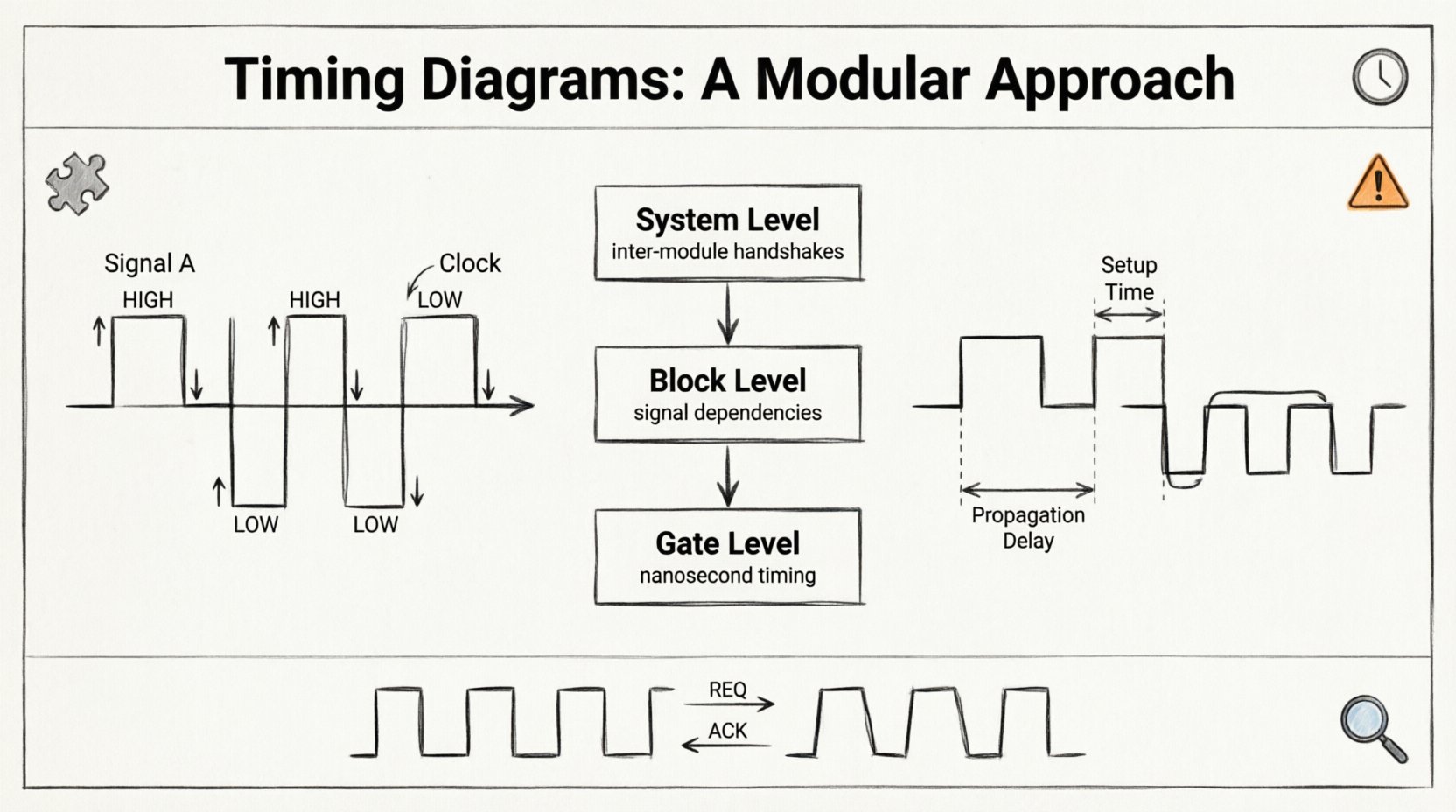

Das modulare Vorgehen für komplexe Designs 🧩

Moderne digitale Systeme sind selten einfach. Sie bestehen aus mehreren Untereinheiten, jeder mit eigenen Zeitbedingungen. Die Versuch, das gesamte System in einem einzigen Diagramm darzustellen, führt oft zu Unübersichtlichkeit und Verwirrung. Ein modulares Vorgehen zerlegt die Architektur in handhabbare Teile. Diese Methode verbessert die Lesbarkeit und vereinfacht den Debugging-Prozess.

Warum Modulargkeit wichtig ist

Die Aufteilung eines Systems in Module ermöglicht es Designern, sich auf spezifische Schnittstellen zu konzentrieren, ohne in der Komplexität der gesamten Architektur zu versinken. Wenn ein Zeitverstoß auftritt, erleichtert ein modulares Diagramm die Identifizierung der Ursache. Es verringert die kognitive Belastung und fördert die Zusammenarbeit zwischen verschiedenen Ingenieurteams, die an separaten Blöcken arbeiten.

Die Vorteile dieses Ansatzes sind:

- Isolierung von Problemen:Probleme können innerhalb eines bestimmten Blocks identifiziert werden, anstatt im gesamten System.

- Wiederverwendbarkeit:Standardisierte Zeitmuster für häufige Module können in verschiedenen Projekten wiederverwendet werden.

- Skalierbarkeit:Neue Funktionen können als neue Module hinzugefügt werden, ohne das gesamte Diagramm neu zeichnen zu müssen.

- Effizienz des Teams:Verschiedene Teams können gleichzeitig an ihren jeweiligen Zeitdiagrammen arbeiten.

Definition von Modulgrenzen

Um diese Strategie effektiv umzusetzen, müssen klare Grenzen festgelegt werden. Jedes Modul sollte definierte Eingänge und Ausgänge haben. Das Zeitdiagramm für ein einzelnes Modul sollte sich auf die Signale konzentrieren, die diese Grenze überschreiten. Interne Details können abstrahiert werden, es sei denn, sie beeinflussen direkt die Schnittstellenzeiten.

| Modul-Ebene | Schwerpunktgebiet | Detailgenauigkeit |

|---|---|---|

| Systemebene | Kommunikation zwischen Modulen | Hochlevel-Handshakes |

| Block-Ebene | Interne Datenpfade | Spezifische Signalabhängigkeiten |

| Gatter-Ebene | Ausbreitungsverzögerungen | Genau Timing in Nanosekunden |

Durch die Organisation der Diagramme nach diesen Ebenen können Ingenieure eine klare Hierarchie der Informationen aufrechterhalten. Diese Struktur stellt sicher, dass die richtige Detailgenauigkeit für die jeweilige Phase des Entwurfsprozesses zur Verfügung steht.

Signalzustände und -übergänge entschlüsseln 📊

Sobald die modulare Struktur vorliegt, ist der nächste Schritt die Analyse der spezifischen Signale. Nicht alle Signale verhalten sich gleich. Einige sind kontinuierlich, andere werden am Flankenübergang ausgelöst. Das Verständnis der Art jedes Signals ist entscheidend für die korrekte Erstellung der Diagramme.

Häufige Signalkategorien umfassen:

- Taktsignale: Das Herzschlag-Signal des Systems. Diese Signale sind periodisch und treiben Zustandsänderungen an. Sie haben in der Regel strenge Anforderungen an Frequenz und Tastverhältnis.

- Daten-Signale: Die tatsächlich übertragenen Informationen. Diese müssen während bestimmter Fenster im Verhältnis zum Takt stabil sein.

- Steuer-Signale: Signale, die Funktionen aktivieren oder deaktivieren, wie z. B. Chip Select oder Enable.

- Reset-Signale: Initialisierungssignale, die das System in einen bekannten Zustand zwingen.

Übergänge auf diesen Leitungen sind entscheidend. Ein steigender Flankentrigger löst oft eine Aktion aus, während ein fallender Flankentrigger diese möglicherweise abschließt. In asynchronen Systemen ist die Beziehung zwischen diesen Flanken weniger vorhersehbar und erfordert eine detailliertere Analyse.

Darstellung der Ausbreitungsverzögerung

Kein Signal ändert sich sofort. Physikalische Beschränkungen verursachen eine Ausbreitungsverzögerung. Wenn ein Signal ein Bauelement verlässt, benötigt es Zeit, um durch die Leitung zu reisen und beim nächsten Bauelement einzutreffen. Zeitdiagramme müssen diese Verzögerung berücksichtigen. Wenn ein Diagramm zeigt, dass ein Signal zur Zeit T wechselt, könnte der Empfänger es erst bis zur Zeit T + Δt sehen.

Das Ignorieren der Ausbreitungsverzögerung kann zu erheblichen Fehlern bei Simulation und Implementierung führen. Ingenieure müssen diese Verzögerungen modellieren, um sicherzustellen, dass Setup- und Hold-Zeiten entlang des gesamten Pfades eingehalten werden.

Kritische Zeitbedingungen erklärt ⚠️

Die häufigste Ursache für Ausfälle in der digitalen Schaltungstechnik ist eine Zeitverletzung. Diese Verletzungen treten auf, wenn Signale die erforderlichen Stabilitätsfenster nicht erfüllen. Zwei Hauptbedingungen steuern dieses Verhalten: Setup-Zeit und Hold-Zeit.

Setup-Zeit

Die Setup-Zeit ist die minimale Zeitspanne, in der Daten stabil sein müssen, bevor der aktive Taktflankenausgang eintritt. Wenn die Daten zu spät eintreffen, kann das Flip-Flop den korrekten Wert möglicherweise nicht erfassen. Diese Bedingung ist entscheidend für die Bestimmung der maximalen Betriebsfrequenz eines Systems. Wenn die Taktperiode kürzer ist als die Propagationsverzögerung plus die Setup-Zeit, wird das System versagen.

Wichtige Überlegungen zur Setup-Zeit umfassen:

- Eine Analyse der längsten Pfadstrecke ist erforderlich, um den ungünstigsten Fall zu ermitteln.

- Prozess-, Spannungs- und Temperaturvariationen beeinflussen die Verzögerung.

- Taktjitter kann in das verfügbare Setup-Fenster hineinwirken.

Hold-Zeit

Die Hold-Zeit ist die minimale Zeitspanne, in der Daten stabil bleiben müssen, nachdem der aktive Taktflankenausgang eingetreten ist. Wenn die Daten zu früh wechseln, könnte das Flip-Flop den falschen Wert erfassen oder in einen metastabilen Zustand geraten. Im Gegensatz zur Setup-Zeit ist die Hold-Zeit unabhängig von der Taktfrequenz. Sie hängt von der internen Verzögerung des Bauteils und dem externen Pfad ab.

Hold-Zeit-Verletzungen sind oft schwerer zu beheben, da sie nicht durch Verlangsamung des Taktes behoben werden können. Stattdessen erfordern sie eine Hinzufügung von Verzögerung in den Datenpfad oder eine Neugestaltung der Logik.

Zusammenfassung der Zeitbedingungen

| Bedingung | Definition | Einfluss auf die Frequenz | Lösungsmethode |

|---|---|---|---|

| Setup-Zeit | Stabil vor der Taktflanke | Begrenzt die maximale Frequenz | Optimiere den Logikpfad |

| Hold-Zeit | Stabil nach der Taktflanke | Unabhängig von der Frequenz | Füge Pufferverzögerung hinzu |

| Propagationsverzögerung | Zeit zum Durchlaufen der Logik | Beide beeinflusst | Schaltungs-Optimierung |

Häufige Fehlerquellen und Verletzungen 🚫

Selbst bei einem modularen Ansatz können Fehler auftreten. Die Erkennung häufiger Fehlerquellen hilft, sie in der Entwurfsphase zu vermeiden. Bei der Hardware-Verifikation treten mehrere Arten von Verletzungen häufig auf.

- Metastabilität: Tritt auf, wenn ein Signal genau am Taktrand wechselt. Die Ausgabe des Flip-Flops wird unvorhersehbar. Dies ist bei der Übergabe zwischen Taktdomänen üblich.

- Glitches: Kurze, unbeabsichtigte Pulse, verursacht durch Unterschiede in den Logikpfaden. Diese können falsche Zustandsänderungen auslösen.

- Taktschiefe: Wenn das Taktsignal zu verschiedenen Komponenten zu unterschiedlichen Zeiten eintrifft. Dies verringert das effektive Zeitfenster für die Timing-Analyse.

- Rennbedingungen: Wenn das Ergebnis von der Reihenfolge der Ereignisse abhängt, was in asynchronen Designs unvorhersehbar ist.

Die Behandlung dieser Probleme erfordert eine sorgfältige Analyse des Zeitdiagramms. Suchen Sie nach überlappenden Fenstern, in denen keine Stabilität garantiert ist. Stellen Sie sicher, dass Reset-Sequenzen korrekt befolgt werden, um undefinierte Zustände zu vermeiden.

Implementierung des modularen Workflows 🛠️

Um diese Methode effektiv anzuwenden, folgen Sie einem strukturierten Workflow. Dadurch wird sichergestellt, dass jeder Aspekt der Timing-Analyse abgedeckt wird, ohne Redundanz.

- Schnittstellen definieren: Listen Sie klar alle Eingaben und Ausgaben für jedes Modul auf.

- Taktdomänen identifizieren: Bestimmen Sie, zu welcher Taktdomäne welche Signale gehören.

- Datenpfade abbilden: Verfolgen Sie den Pfad von der Quelle zur Zielkomponente.

- Einschränkungen anwenden: Legen Sie Setup- und Hold-Anforderungen für jedes Flip-Flop fest.

- Übergänge validieren: Überprüfen Sie die Kanten-Ausrichtung und die Pulslängen.

- Integration überprüfen: Stellen Sie sicher, dass die Modul-Diagramme bei der Kombination ausgerichtet sind.

Jeder Schritt baut auf dem vorherigen auf. Das Überspringen eines Schritts kann zu Lücken in der Abdeckung führen. Zum Beispiel kann die Ignorierung von Taktdomänen zu Synchronisationsfehlern führen, die später schwer zu debuggen sind.

Umgang mit mehreren Taktdomänen 🌐

Wenn Designs wachsen, werden mehrere Taktfrequenzen notwendig. Einige Teile des Systems laufen schnell, andere langsam. Die Synchronisation dieser Domänen ist eine der anspruchsvollsten Aufgaben der Timing-Analyse.

Wenn Signale von einer Taktdomäne in eine andere wechseln, muss das Zeitdiagramm die Beziehung zwischen den beiden Takten widerspiegeln. Wenn die Takte asynchron sind, ist besondere Vorsicht erforderlich, um Metastabilität zu vermeiden. Techniken wie Synchronisiererketten oder Handshake-Protokolle werden verwendet, um diesen Übergang sicher zu managen.

Wichtige Strategien für Mehr-Takt-Designs umfassen:

- Gray-Codierung: Verwendung von Gray-Codes, um mehrbitige Zähler sicher zwischen Domänen zu übertragen.

- FIFO-Puffer: Verwendung von First-In-First-Out-Warteschlangen, um Lese- und Schreib-Takte zu entkoppeln.

- Handshake-Signale: Verwendung von Anfrage/Acknowledgement-Paaren, um die Gültigkeit der Daten zu gewährleisten.

Zeitdiagramme für diese Szenarien müssen die Taktränder beider Bereiche explizit anzeigen. Dadurch können Ingenieure sehen, ob die Daten lange genug stabil bleiben, damit der empfangende Takt sie erfassen kann.

Debuggen mit visuellen Daten 🔍

Wenn ein Entwurf fehlschlägt, ist das erste, was man prüfen sollte, das Zeitdiagramm. Debugging erfordert Geduld und einen systematischen Ansatz. Beginnen Sie damit, das fehlerhafte Modul zu isolieren. Vergleichen Sie das erwartete Diagramm mit dem tatsächlichen Wellenformverlauf.

Suchen Sie nach Abweichungen in:

- Signaltiming im Verhältnis zum Takt.

- Pulsbreite von Steuersignalen.

- Zustandsübergänge während des Resets.

- Glitches auf Datensignalen.

Werkzeuge bieten oft Zoom-Funktionen, um Details auf Nanosekunden-Ebene zu untersuchen. Nutzen Sie diese Funktionen, um den genauen Zeitpunkt eines Verstoßes zu überprüfen. Korrelieren Sie die visuellen Daten mit der Logik, um die Ursache zu verstehen.

Abschließende Gedanken zur Entwurfsganzheit 💡

Zeitdiagramme sind mehr als nur technische Zeichnungen; sie sind die Baupläne zu zuverlässigen digitalen Systemen. Durch die Anwendung eines modularen Ansatzes können Ingenieure die Komplexität beherrschen und Klarheit bewahren. Dieser Ansatz fördert Skalierbarkeit und verringert die Wahrscheinlichkeit kostspieliger Fehler.

Erfolg im Hardware-Entwurf beruht auf der Aufmerksamkeit für Details. Jede Nanosekunde zählt. Jeder Übergang ist wichtig. Durch strikte Anwendung dieser Prinzipien können Teams Systeme entwickeln, die unter realen Bedingungen vorhersehbar funktionieren. Die modulare Aufteilung der Zeitdiagrammanalyse stellt sicher, dass kein Detail übersehen wird, was zu robusten und effizienten Hardware-Lösungen führt.

Die kontinuierliche Verbesserung dieser Fähigkeiten ist notwendig, wenn sich die Technologie weiterentwickelt. Neue Standards und höhere Geschwindigkeiten erfordern aktualisierte Analysemethoden. Bleiben Sie über neu entstehende Best-Practices informiert, um einen Wettbewerbsvorteil im Bereich der digitalen Ingenieurwissenschaft zu bewahren.