In der digitalen Elektronik und Computer-Engineering ist das Verständnis der zeitlichen Beziehung zwischen Signalen grundlegend für die Systemzuverlässigkeit. Ein Zeitdiagramm dient als primäres visuelles Sprachmittel zur Beschreibung dieser Beziehungen. Es stellt Signalzustände entlang einer Zeitachse dar, wodurch Ingenieure den Datenfluss, die Taktsynchronisation und potenzielle Gefahren innerhalb einer Schaltung visualisieren können. Dieser Leitfaden untersucht die strukturellen Elemente, Betriebsmuster und kritischen Szenarien, die bei der Wellenformanalyse auftreten.

Unabhängig davon, ob integrierte Schaltkreise entworfen oder eingebettete Systeme debuggt werden, ist die Fähigkeit, genaue Zeitdarstellungen zu interpretieren und zu erstellen, eine zentrale Kompetenz. Dieses Dokument bietet einen technischen Überblick darüber, wie Signale interagieren, welche Einschränkungen sie erfüllen müssen, und welche häufigen Fallen bei der Verifikation auftreten.

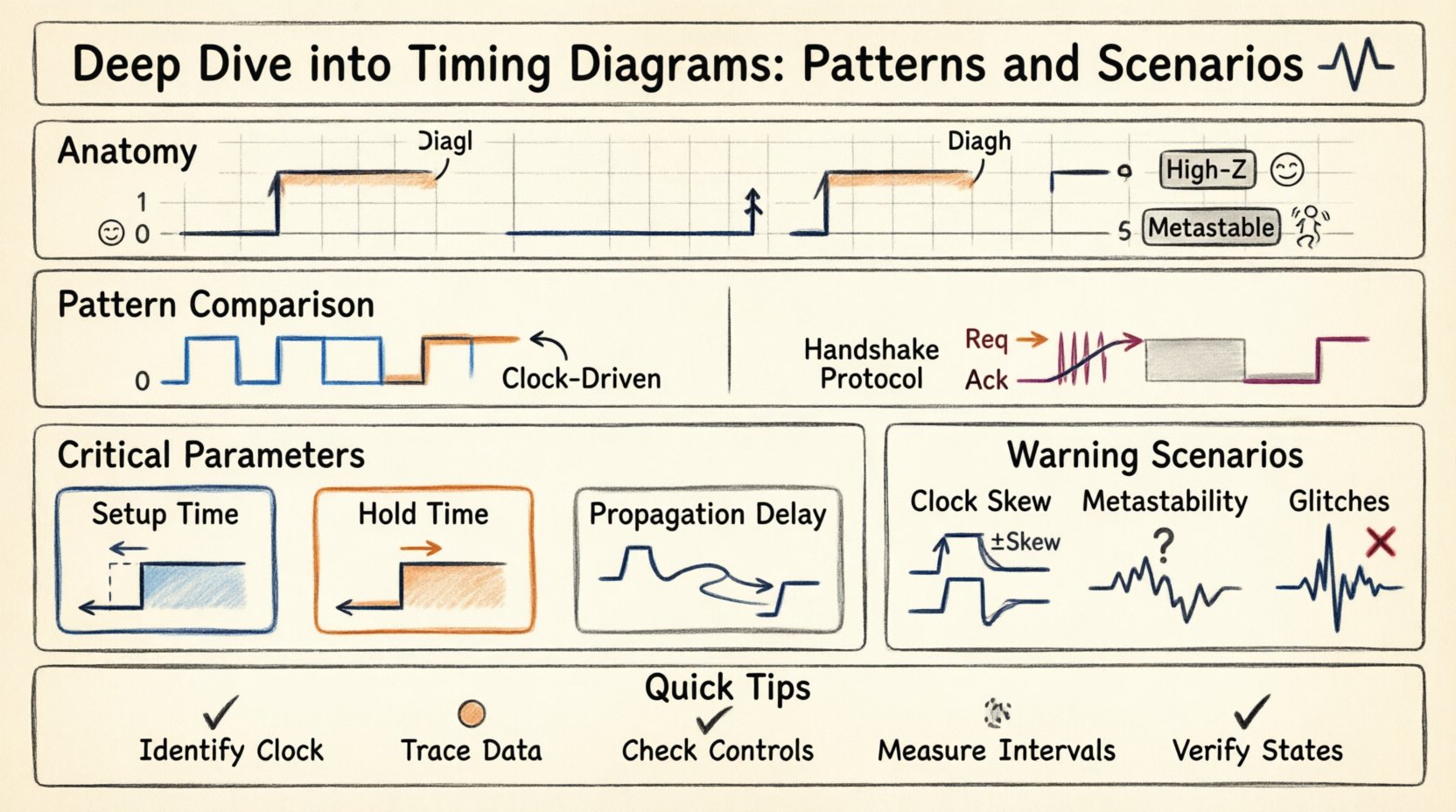

📐 Aufbau eines Zeitdiagramms

Ein Zeitdiagramm ist eine grafische Darstellung, bei der die horizontale Achse die Zeit und die vertikale Achse die Signalpegel darstellt. Jede horizontale Linie entspricht einem bestimmten Signal oder einer Netzeinheit innerhalb des Entwurfs. Das Verständnis der Komponenten ist der erste Schritt hin zu einer genauen Analyse.

- Zeitachse: Läuft normalerweise horizontal von links nach rechts. Sie kann linear oder logarithmisch sein, je nach Skala der beobachteten Ereignisse.

- Signalleitungen: Individuelle Spuren, die Spannungspegel darstellen. Hohe Spannung bezeichnet typischerweise Logik 1, während niedrige Spannung Logik 0 bedeutet.

- Übergänge: Vertikale Linien, die einen Zustandswechsel anzeigen, wie z. B. eine steigende Flanke (0 auf 1) oder eine fallende Flanke (1 auf 0).

- Beschriftungen:Textanmerkungen, die spezifische Signale, Pins oder Steuerleitungen identifizieren.

- Markierungen:Vertikale gestrichelte Linien, die häufig verwendet werden, um bestimmte Ereignisse zu kennzeichnen, wie z. B. einen Taktpuls oder einen Reset-Trigger.

🔢 Logische Pegel und Zustände

Digitale Signale existieren nicht immer streng bei 0 oder 1. In praktischen Szenarien können Signale in undefinierten Zuständen oder Hochwiderstandszuständen existieren. Ein vollständiges Diagramm sollte diese Variationen berücksichtigen.

- Logisch hoch (1): Das Signal wird auf einen Spannungspegel gebracht, der als logisch wahr erkannt wird.

- Logisch niedrig (0): Das Signal wird auf einen Spannungspegel gebracht, der als logisch falsch erkannt wird.

- High-Z: Das Signal ist vom Treiber getrennt und schwebt praktisch frei. Dies ist bei Dreizustands-Schaltern üblich.

- Metastabil: Ein Zustand, in dem das Signal weder hoch noch niedrig ist, der häufig während asynchroner Übergänge auftritt.

⚙️ Häufige Zeitmuster

Entwürfe folgen vorhersehbaren Mustern, um die Datenintegrität zu gewährleisten. Diese Muster definieren, wie Daten im Verhältnis zu Steuersignalen bewegt werden. Das Erkennen dieser Muster hilft dabei, zu verifizieren, ob ein Entwurf seinen Spezifikationen entspricht.

📌 Synchroner Datentransfer

Synchronisierte Entwürfe stützen sich auf ein globales Taktsignal, um Aktionen zu koordinieren. Daten werden nur zu bestimmten Zeitpunkten abgetastet, typischerweise an der steigenden oder fallenden Flanke des Taktsignals.

- Taktgetrieben: Alle Zustandsänderungen erfolgen im Verhältnis zur Taktränder.

- Daten Gültigkeit:Die Daten müssen vor der Taktränder stabil sein und danach stabil bleiben.

- Ausbreitung:Es besteht eine Verzögerung zwischen der Taktränder und dem Zeitpunkt, zu dem sich die Ausgabe ändert.

📌 Asynchrone Handshake

Asynchrone Kommunikation beruht nicht auf einem gemeinsamen Takt. Stattdessen verwendet sie Steuersignale, um anzugeben, wann Daten bereit sind und wann sie empfangen wurden.

- Anforderung (Req):Der Absender signalisiert, dass Daten verfügbar sind.

- Bestätigung (Ack):Der Empfänger signalisiert, dass die Daten akzeptiert wurden.

- Wartezyklen:Der Absender kann pausieren, bis der Empfänger bereit ist.

| Funktion | Synchrones Muster | Asynchrones Muster |

|---|---|---|

| Koordination | Globales Taktsignal | Steuer-Handshake-Signale |

| Geschwindigkeit | Allgemein höher | Variabel, abhängig von der Antwort |

| Komplexität | Taktausbreitungsnetzwerk | Protokolllogik |

| Verzögerung | Vorhersehbar | Variabel |

⏱️ Kritische Zeitparameter

Über die sichtbaren Linien hinaus definieren spezifische numerische Einschränkungen, ob eine Schaltung korrekt funktioniert. Diese Parameter sind entscheidend für die statische Zeitanalyse und müssen gegen physikalische Grenzen überprüft werden.

🛑 Haltezeit

Die Haltezeit ist die minimale Zeitspanne, während der das Datensignal vor dem Taktflankensignal stabil gehalten werden sollte. Wenn sich das Datensignal zu nahe an der Taktflanke ändert, kann der empfangende Flip-Flop den korrekten Wert möglicherweise nicht erfassen.

- Messung: Messung rückwärts in der Zeit vom aktiven Taktflankenpunkt aus.

- Risiko: Eine Verletzung führt zu falscher Datenerfassung.

- Anforderung: Die Datenpfadverzögerung muss lang genug sein, um das Haltefenster zu erfüllen.

🛑 Haltezeit

Die Haltezeit ist die minimale Zeitspanne, während der das Datensignal nach der Taktflanke stabil gehalten werden sollte. Dadurch wird sichergestellt, dass die Schaltung genug Zeit hat, den Eingangswert zu sichern.

- Messung: Messung vorwärts in der Zeit vom aktiven Taktflankenpunkt aus.

- Risiko: Eine Verletzung führt zu Metastabilität oder Erfassung falscher Daten.

- Anforderung: Die Datenpfadverzögerung muss kurz genug sein, um das Haltezeitfenster zu ermöglichen.

⚡ Propagationsverzögerung

Dies ist die Zeit, die ein Signal benötigt, um vom Eingang eines Logikgatters zum Ausgang zu gelangen. Sie variiert je nach Lastkapazität und dem internen Widerstand des Transistors.

- tpd (Hoch nach Niedrig): Zeit für den Übergang von 1 nach 0.

- tpd (Niedrig nach Hoch): Zeit für den Übergang von 0 nach 1.

- Verzögerungsunterschied: Unterschiede in der Verzögerung zwischen parallelen Pfaden.

🚨 Kritische Zeitverhaltensszenarien

Bestimmte Szenarien stellen erhebliche Herausforderungen dar, die eine sorgfältige Analyse erfordern. Diese Situationen betreffen oft Wechselwirkungen zwischen verschiedenen Taktbereichen oder physische Beschränkungen der Hardware.

🔄 Taktschiefe

Taktschiefe tritt auf, wenn das Taktsignal zu verschiedenen Komponenten zu unterschiedlichen Zeiten eintrifft. Dies kann aufgrund von Routing-Unterschieden oder physischen Distanzen auftreten.

- Positive Schiefe: Das Ziel-Taktsignal trifft später ein als das Quell-Taktsignal.

- Negative Schiefe: Das Ziel-Taktsignal trifft früher ein als das Quell-Taktsignal.

- Auswirkung: Kann die Setup-Zeit-Margen effektiv verringern oder Hold-Zeit-Verletzungen erhöhen.

🌊 Metastabilität

Metastabilität ist ein Zustand, bei dem die Ausgabe eines Flip-Flops weder hoch noch niedrig ist. Sie tritt gewöhnlich auf, wenn Setup- oder Hold-Zeiten verletzt werden, insbesondere bei asynchronen Übergängen.

- Auflösung: Der Schaltkreis löst sich letztendlich in einen stabilen Zustand auf, aber die dafür benötigte Zeit ist unvorhersehbar.

- Behebung: Verwenden Sie Synchronisierer (Mehrfach-Flip-Flops), um die Wahrscheinlichkeit von Fehlern zu verringern.

- MTBF: Die durchschnittliche Zeit zwischen Ausfällen wird auf Basis der Auflösungsraten für Metastabilität berechnet.

📉 Störungen

Störungen sind kurzlebige Spitzen im Signal, die fälschlicherweise als gültige Übergänge interpretiert werden können. Sie treten häufig aufgrund von Unterschieden in den Ausbreitungsverzögerungen entlang verschiedener Pfade auf.

- Ursachen: Ungleich lange Pfade oder Rennbedingungen.

- Wirkung: Kann unbeabsichtigte Zustandsänderungen in nachgeschalteten Logikschaltungen auslösen.

- Minderung: Verwenden Sie Filterlogik oder stellen Sie eine korrekte Zeitplanung sicher.

🔍 Analyse von Wellenformen

Beim Überprüfen eines Zeitdiagramms stellt ein systematischer Ansatz sicher, dass kein Detail übersehen wird. Ingenieure müssen den Fluss von Daten- und Steuersignalen verfolgen, um Abweichungen zu identifizieren.

🔍 Schritt-für-Schritt-Analyse

- Identifizieren Sie den Takt: Finden Sie das primäre Taktsignal. Bestimmen Sie, ob es auf steigender oder fallender Flanke ausgelöst wird.

- Verfolgen Sie die Datenpfade: Verfolgen Sie die Datenleitungen von der Quelle zum Ziel.

- Steuer-Signale prüfen:Stellen Sie sicher, dass Enables, Resets und Clears korrekt aktiviert sind.

- Intervalle messen:Berechnen Sie die Zeit zwischen bestimmten Ereignissen, um Setup- und Hold-Anforderungen zu überprüfen.

- Zustandsübergänge überprüfen:Stellen Sie sicher, dass der Ausgangszustand der erwarteten Logikfunktion entspricht.

🔍 Kanten-Trigger lesen

Das Verständnis dafür, wie ein Bauteil auf Signal-Kanten reagiert, ist entscheidend.

- Positiver Kanten-Trigger:Die Aktion erfolgt bei der Übergang von niedrig zu hoch.

- Negativer Kanten-Trigger:Die Aktion erfolgt bei der Übergang von hoch zu niedrig.

- Ebenen-Trigger:Die Aktion erfolgt solange, wie das Signal auf einem bestimmten Pegel bleibt.

🛠️ Dokumentationsstandards

Klare Dokumentation stellt sicher, dass Entwürfe von anderen Ingenieuren verstanden werden. Konsistenz in der Notation und Beschriftung verhindert Missverständnisse während der Fehlersuche oder Übergabe.

📝 Beschriftungskonventionen

- Signalnummern:Verwenden Sie konsistente Namenskonventionen (z. B.

clk,rst_n,data_in). - Polarität:Aktiv-niedrige Signale sollten klar gekennzeichnet werden, oft mit einem Strich oder Suffix.

- Einheiten:Geben Sie die Zeiteinheiten (ns, µs, ms) auf der Zeitachse eindeutig an.

- Skalierung: Stellen Sie sicher, dass das Zeitskalenverhältnis den dargestellten Ereignissen angemessen ist.

📝 Visuelle Klarheit

- Abstand: Vermeiden Sie überlappende Linien, wenn möglich.

- Kontrast: Verwenden Sie unterschiedliche Farben oder Linienstärken für verschiedene Signalarten.

- Anmerkungen: Fügen Sie Notizen hinzu, die komplexe Verhaltensweisen oder spezifische Einschränkungen erklären.

- Raster: Verwenden Sie ein Raster-Hintergrund, um die Messung von Zeitintervallen zu unterstützen.

🚧 Fehlerbehebungsablauf

Wenn ein Entwurf die Zeitvorgaben nicht erfüllt, hilft ein strukturierter Fehlerbehebungsprozess, die Ursache zu isolieren. Dies beinhaltet die Prüfung des Diagramms anhand der physikalischen Einschränkungen.

🚧 Identifizieren von Verstößen

- Setup-Zeit prüfen: Kommt die Datenübertragung relativ zum Takt zu spät an?

- Hold-Zeit prüfen: Ändert sich die Datenübertragung zu früh nach dem Takt?

- Taktfrequenz prüfen: Ist die Taktperiode kürzer als die erforderliche Mindestperiode?

🚧 Maßnahmen zur Minderung

- Pipelinen-Register: Fügen Sie zusätzliche Register hinzu, um lange kombinatorische Pfade zu unterbrechen.

- Taktgating: Verringern Sie die Aktivität, um den Stromverbrauch zu senken und die Zeitverhaltensweise möglicherweise zu verbessern.

- Puffer-Einfügung: Fügen Sie Puffer hinzu, um Verzögerungen über parallele Pfade auszugleichen.

- Zeitbedingungen: Definieren Sie falsche Pfade, um Logik auszuschließen, die den Datenfluss nicht beeinflusst.

📈 Best Practices für die Gestaltung

Die Einführung bewährter Praktiken in der Entwurfsphase verringert die Wahrscheinlichkeit von Zeitverzögerungsproblemen später im Entwicklungszyklus. Proaktive Planung ist effizienter als reaktives Beheben.

- Schnittstellen standardisieren:Verwenden Sie bekannte Protokolle für die Datenübertragung, um die Zeitverifizierung zu vereinfachen.

- Asynchrone Pfade minimieren:Halten Sie asynchrone Interaktionen auf ein Minimum, um die Risiken von Metastabilität zu verringern.

- Annahmen dokumentieren:Geben Sie in den Entwurfspezifikationen die Taktfrequenzen und Spannungsniveaus klar an.

- Regelmäßig überprüfen:Durchführen von Zeitverzögerungsüberprüfungen bei jedem wichtigen Meilenstein des Projekts.

🎯 Zusammenfassung der wichtigsten Konzepte

Zeitdiagramme sind essenzielle Werkzeuge zur Visualisierung des zeitlichen Verhaltens digitaler Systeme. Sie zeigen, wie Daten- und Steuersignale im Laufe der Zeit interagieren, und heben kritische Einschränkungen wie Ansprech- und Haltezeiten hervor. Durch das Verständnis der Struktur dieser Diagramme können Ingenieure Muster erkennen, Fehler vorhersagen und eine robuste Systemleistung sicherstellen.

Zu den zentralen Erkenntnissen gehören der Unterschied zwischen synchronen und asynchronen Mustern, die Bedeutung der Taktschiefe-Steuerung sowie die Notwendigkeit klarer Dokumentationsstandards. Die Einhaltung dieser Prinzipien erleichtert eine zuverlässige Gestaltung und vereinfacht den Verifizierungsprozess.

Die kontinuierliche Analyse von Wellenformdaten stellt sicher, dass Entwürfe innerhalb der Betriebsgrenzen bleiben. Mit dem Fortschritt der Technologie und steigenden Taktfrequenzen wird die Genauigkeit der Zeitverzögerungsanalyse noch kritischer. Die Beherrschung dieser Konzepte ermöglicht die Erstellung stabiler, leistungsstarker digitale Architekturen.