In der komplexen Welt der eingebetteten Technik ist Timing alles. Ein Mikrocontroller könnte in der Simulation perfekt funktionieren, aber auf der Hardware katastrophal versagen, verursacht durch wenige Nanosekunden Verzögerung. Hier wird das Timing-Diagramm zu einem unverzichtbaren Werkzeug. Diese visuellen Darstellungen zeigen das Verhalten von Signalen über die Zeit auf und liefern ein klares Bild davon, wie Komponenten innerhalb eines digitalen Systems miteinander interagieren. Ob Sie einen Kommunikationsfehler debuggen oder eine neue Peripherie-Schnittstelle entwerfen – das Verständnis dafür, wie man Timing-Diagramme liest und erstellt, ist grundlegend.

Dieser Leitfaden behandelt die wesentlichen Mechanismen der Signal-Timing, von den grundlegenden Definitionen bis hin zu komplexen Protokoll-Interaktionen. Wir werden untersuchen, wie man Wellenformen interpretiert, genaue Diagramme aus Messdaten erstellt und häufige Fehlerquellen identifiziert, die zu Systeminstabilität führen. Durch die Beherrschung dieser visuellen Werkzeuge erlangen Sie die Fähigkeit, das Systemverhalten vorherzusagen und Entwürfe zu validieren, bevor sie jemals die Arbeitstafel verlassen.

🔍 Verständnis der Grundlagen der Signal-Timing

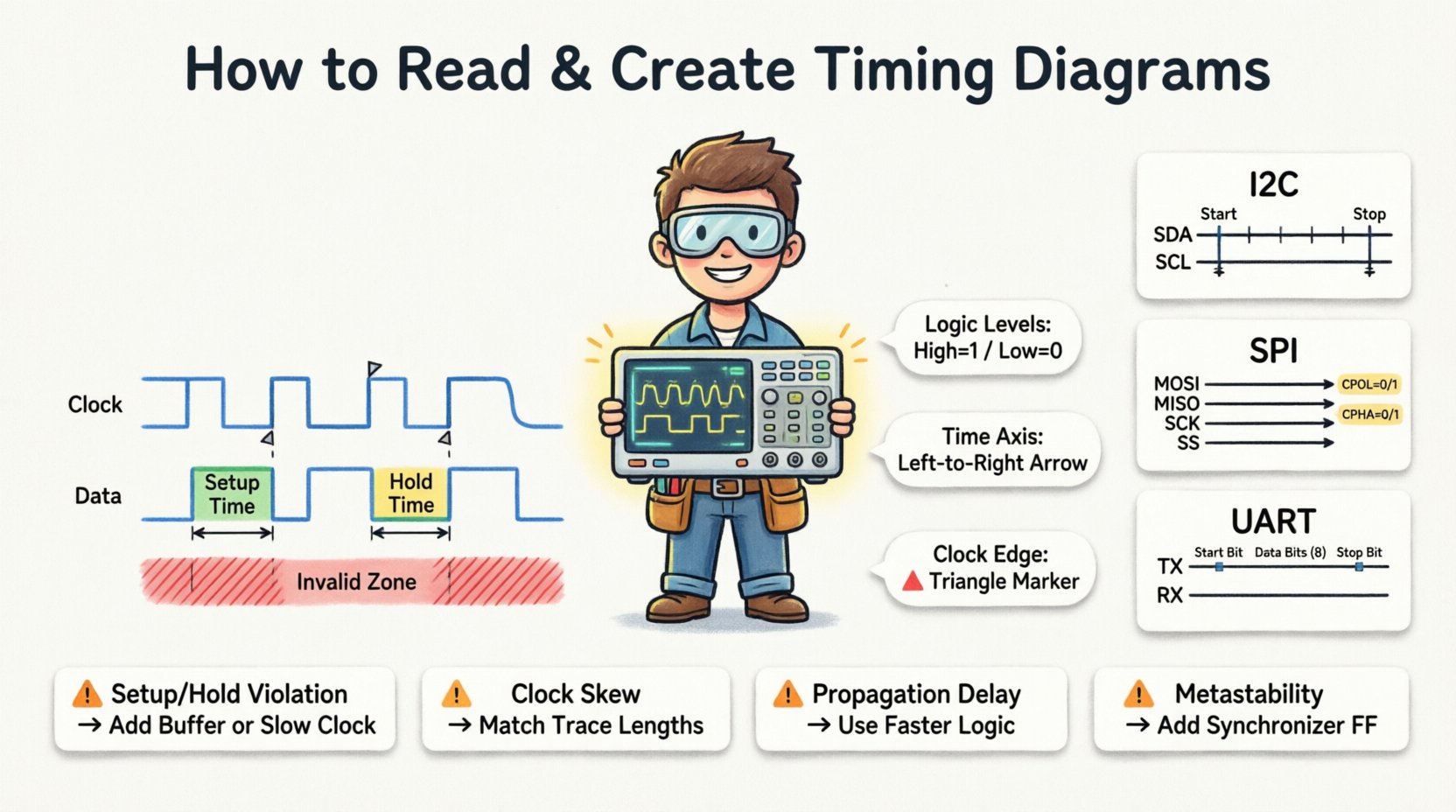

Ein Timing-Diagramm ist nicht einfach nur eine Zeichnung; es ist eine mathematische Darstellung logischer Zustände im Verhältnis zu einer Zeitachse. In eingebetteten Systemen beschäftigen wir uns vor allem mit digitalen Logikpegeln, die binär sind: Hoch (1) und Niedrig (0). Die Komplexität liegt jedoch in den Übergängen zwischen diesen Pegeln.

- Logische Pegel:Die meisten eingebetteten Systeme arbeiten mit spezifischen Spannungsschwellen. Zum Beispiel definiert ein 3,3-V-System Hoch als alles oberhalb von 2,0 V und Niedrig als alles unterhalb von 0,8 V.

- Zeitachse:Die Zeit fließt von links nach rechts. Der horizontale Abstand stellt die Dauer bestimmter Zustände oder die Verzögerung zwischen Ereignissen dar.

- Signalverläufe:Jede horizontale Linie stellt einen bestimmten Draht oder eine bestimmte Leitung dar. Mehrere Linien, die vertikal übereinander angeordnet sind, ermöglichen den Vergleich der Signalbeziehungen.

Beim Analysieren eines Systems suchen Sie nach Kausalität. Triggernt das Taktsignal die Datenänderung? Muss das Aktivierungs-Signal vorher aktiv sein, damit die Daten gültig sind? Timing-Diagramme beantworten diese Fragen visuell.

🛠️ Wichtige Bestandteile eines Timing-Diagramms

Um ein Diagramm korrekt zu interpretieren, müssen Sie die Standardelemente erkennen, die zur Darstellung des Signalverhaltens verwendet werden. Diese Komponenten definieren die Regeln für die Interaktion mit der Hardware.

| Komponente | Beschreibung | Visueller Indikator |

|---|---|---|

| Signalname | Identifiziert den spezifischen Draht oder die spezifische Leitung | Textlabel auf der linken Seite |

| Logischer Pegel | Hoch (1) oder Niedrig (0) Zustand | Flache horizontale Linie am oberen oder unteren Rand |

| Übergangskante | Wechsel von Hoch zu Niedrig oder umgekehrt | Senkrechte Linie, die die Pegel verbindet |

| Taktkante | Auslöspunkt für asynchrone Logik | Punktierte Linie oder Dreiecksmarkierung |

| Ungültiger Bereich | Bereich, in dem Daten nicht gelesen werden können | Schraffierter oder gestrichelter Bereich |

Das Verständnis dieser Komponenten ermöglicht es Ihnen, komplexe Wechselwirkungen zu analysieren. Ein schraffierter Bereich weist beispielsweise oft auf eine Setup- oder Hold-Zeitbedingung hin, bei der das empfangende Gerät die Daten nicht zuverlässig erfassen kann.

👁️ So lesen Sie ein Zeitdiagramm Schritt für Schritt

Das Lesen eines Zeitdiagramms erfordert einen systematischen Ansatz. Sie übersetzen im Grunde ein visuelles Muster in eine Abfolge von Ereignissen. Folgen Sie diesem Prozess, um Genauigkeit zu gewährleisten.

1. Identifizieren Sie die Taktsquelle

Die meisten eingebetteten Systeme sind synchron, was bedeutet, dass ein Taktsignal die Geschwindigkeit der Operationen bestimmt. Finden Sie die Taktspur. Sie zeigt normalerweise eine regelmäßige, periodische Rechteckwelle.

- Überprüfen Sie die Frequenz. Ist sie 1 MHz oder 100 MHz? Dies bestimmt die Geschwindigkeit des gesamten Systems.

- Identifizieren Sie die Flankentypen. Triggert das Gerät am steigenden Flanken (von Low nach High) oder am fallenden Flanken (von High nach Low)?

2. Markieren Sie die Gültigkeitsfenster für Daten

Daten sind nur während bestimmter Fenster im Verhältnis zum Takt gültig. Suchen Sie die Beziehung zwischen der Taktflanke und der Datenspur.

- Setup-Zeit: Die Daten müssen für eine bestimmte Zeit stabil sein vor der Taktflanke.

- Hold-Zeit: Die Daten müssen für eine bestimmte Zeit stabil bleiben nach der Taktflanke.

Wenn sich die Daten während dieser Fenster ändern, tritt ein Zeitverstoß auf, was zu Metastabilität oder falscher Datenerfassung führen kann.

3. Analysieren Sie Steuersignale

Steuersignale wie Chip Select (CS), Enable (EN) oder Reset (RST) bestimmen, wann eine Kommunikation stattfinden kann.

- Ist der Chip Select aktiv niedrig oder aktiv hoch?

- Muss das Enable-Signal vor Beginn der Taktflankenwechsel aktiviert werden?

- Gibt es asynchrone Ereignisse, die die Taktsynchronisation überschreiben?

4. Überprüfen Sie die Handshake-Mechanismen

Viele Protokolle verwenden Handshake-Mechanismen zur Steuerung des Datenflusses. Suchen Sie nach Bestätigungs- (ACK) oder Bereitschaftssignalen (RDY).

- Wartet der Sender auf ein Signal, bevor er das nächste Byte überträgt?

- Sind in dem Diagramm Timeout-Bedingungen dargestellt?

📐 So erstellen Sie genaue Zeitdiagramme

Die Erstellung eines Zeitdiagramms ist ebenso wichtig wie das Lesen eines solchen. Es dient als Spezifikation für Hardware-Ingenieure und als Überprüfungsleitfaden für Software-Entwickler. Sie können diese aus Anforderungen, Messwerkzeugen oder Simulationsdaten generieren.

Schritt 1: Definieren Sie die Protokollanforderungen

Bevor Sie zeichnen, sammeln Sie die Spezifikationen. Diese stammen meist aus dem Datenblatt des Komponenten, mit der Sie kommunizieren.

- Ermitteln Sie die minimalen und maximalen Taktfrequenzen.

- Notieren Sie die Spannungsniveaus für Logik-Hoch und Logik-Tief.

- Notieren Sie die Setup- und Hold-Zeit-Beschränkungen.

Schritt 2: Erfassen Sie die Signal-Daten

Verwenden Sie Hardware-Tools, um das Verhalten in der realen Welt zu erfassen. Dadurch stellen Sie sicher, dass Ihr Diagramm die Realität widerspiegelt und nicht theoretische Ideale.

- Oszilloskope:Am besten geeignet für die Integrität analoger Signale und Spannungsniveaus.

- Logik-Analysatoren:Am besten geeignet für digitale Zustandsübergänge und Mehrkanal-Timing.

- Simulationsmodelle:Gut geeignet, um die Logik zu überprüfen, bevor die Hardware verfügbar ist.

Schritt 3: Zeichnen Sie die Wellenformen

Zeichnen Sie die Signale chronologisch. Stellen Sie sicher, dass die Zeitskala bei allen Kanälen konsistent ist.

- Verwenden Sie gerade Linien für Logikpegel.

- Verwenden Sie diagonale Linien für Übergänge, um Anstiegs- und Abfallzeiten anzuzeigen.

- Kennzeichnen Sie kritische Punkte wie die Taktränder und Datenänderungen.

Schritt 4: Kennzeichnen Sie kritische Beschränkungen

Anmerkungen liefern Kontext, den visuelle Darstellungen allein nicht vermitteln können.

- Markieren Sie die Setup- und Hold-Zeitfenster explizit.

- Geben Sie die Dauer spezifischer Protokollzustände an (z. B. Start-Bit, Stop-Bit).

- Heben Sie bekannte Latenzen oder Verzögerungen im Signalpfad hervor.

🌐 Zeitdiagramme in gängigen eingebetteten Protokollen

Verschiedene Kommunikationsprotokolle weisen unterschiedliche Timing-Eigenschaften auf. Das Verständnis dieser Feinheiten ist für die Integration entscheidend.

1. Inter-Integrated Circuit (I2C)

I2C ist ein zweidrahtiger synchroner serieller Bus. Er verwendet SDA (Daten) und SCL (Takt).

- Startbedingung:SDA wechselt von Hoch auf Niedrig, während SCL Hoch ist.

- Stop-Bedingung: SDA wechselt von Low auf High, während SCL High ist.

- Datenübertragung: Daten sind gültig, wenn SCL High ist; Änderungen finden statt, wenn SCL Low ist.

- ACK/NACK: Der Empfänger zieht SDA während des neunten Taktpulses auf Low, um die Übernahme zu bestätigen.

2. Serieller Peripherieanschluss (SPI)

SPI ist ein vieradriger synchroner Bus, der höhere Geschwindigkeiten als I2C bietet.

- Leitungen: MOSI (Master Out), MISO (Master In), SCK (Takt), SS (Slave Select).

- CPOL: Die Taktpolarität bestimmt den Ruhezustand (High oder Low).

- CPHA: Die Taktfrequenz bestimmt, wann die Daten abgetastet werden (erste oder zweite Flanke).

- Chip Select: Muss vor Beginn des Taktschaltens aktiviert werden (aktiviert).

3. Universal-asynchroner Empfänger- und Sender (UART)

UART ist asynchron, was bedeutet, dass kein gemeinsamer Taktsignal vorhanden ist. Die Zeitsteuerung beruht auf Baudraten.

- Startbit: Zieht die Leitung auf Low, um den Beginn eines Frames zu signalisieren.

- Datenbits: Wird LSB zuerst übertragen, üblicherweise 8 Bits.

- Stopbit: Zieht die Leitung auf High, um das Ende eines Frames zu signalisieren.

- Parität: Optionales Bit zur Fehlerüberprüfung.

| Funktion | I2C | SPI | UART |

|---|---|---|---|

| Uhr | Synchron (geteilt) | Synchron (geteilt) | Asynchron (keine Uhr) |

| Leitungen | 2 (SDA, SCL) | 4+ (MOSI, MISO, SCK, SS) | 2 (TX, RX) |

| Adressierung | Ja (Byte-Adresse) | Nein (verdrahtungsabhängig) | Nein |

| Max. Geschwindigkeit | ~400 kHz | ~50 MHz | ~3 Mbps |

⚠️ Häufige Zeitverletzungen und Debugging

Selbst bei sorgfältiger Gestaltung können Zeitverletzungen auftreten. Diese sind oft die Ursache für sporadische Fehler, die schwer nachzustellen sind.

1. Setup- und Hold-Zeit-Verletzungen

Dies geschieht, wenn Daten zu früh oder zu spät im Verhältnis zur Taktränder auftreten.

- Symptom: Datenkorruption oder zufällige Fehler bei der Erfassung durch den Logikanalysator.

- Lösung: Verlangsamen Sie die Taktfrequenz oder optimieren Sie die Leiterbahnlängen auf der Leiterplatte.

2. Taktschiefe

Taktschiefe tritt auf, wenn das Taktsignal zu unterschiedlichen Zeiten bei verschiedenen Komponenten eintrifft.

- Symptom: Rennbedingungen, bei denen ein Flip-Flop Daten erfasst, bevor ein anderer bereit ist.

- Lösung: Passen Sie die Leiterbahnlängen an oder verwenden Sie ein spezielles Verteilungsnetzwerk für die Taktsignale.

3. Propagationsverzögerung

Signale benötigen Zeit, um durch Leitungen und Gatter zu reisen. Lange Spuren fügen erhebliche Verzögerung hinzu.

- Symptom: Signalintegritätsprobleme oder Reflexionen auf Hochgeschwindigkeitsleitungen.

- Behebung: Verwenden Sie Abschlusswiderstände und halten Sie die Spuren so kurz wie möglich.

4. Metastabilität

Wenn asynchrone Signale zwischen Taktbereichen wechseln, kann der empfangende Flip-Flop in einen metastabilen Zustand geraten.

- Symptom: Systemhängen oder zufällige Neustarts.

- Behebung: Verwenden Sie Synchronisierketten (zwei oder mehr Flip-Flops in Reihe), um das Signal zu stabilisieren.

📝 Best Practices für Dokumentation

Die Erstellung von Zeitdiagrammen für die Dokumentation stellt sicher, dass zukünftige Entwickler das System verstehen können, ohne die Hardware rückwärts zu analysieren.

- Konsistenz: Verwenden Sie standardisierte Symbole und Linienstile in allen Diagrammen des Projekts.

- Maßstab: Stellen Sie sicher, dass die Zeitachse linear ist und eindeutig mit Einheiten (ns, µs, ms) beschriftet ist.

- Referenz: Verknüpfen Sie das Diagramm immer mit der spezifischen Abschnittsnummer der Datenblätter oder dem Protokollstandard.

- Klarheit: Vermeiden Sie Überladung. Wenn ein Signal statisch ist, zeigen Sie es als waagerechte Linie an, anstatt Rauschen durch Umschalten darzustellen.

- Versionsverwaltung: Aktualisieren Sie die Diagramme, sobald sich die Hardware oder die Firmware erheblich ändern.

🔗 Abschließende Gedanken zur Signalintegrität

Zeitdiagramme schließen die Lücke zwischen abstraktem Logik und physischer Realität. Sie ermöglichen es Ingenieuren, die unsichtbaren Beschränkungen der digitalen Elektronik zu visualisieren. Indem Sie lernen, sie zu lesen, können Sie komplexe Hardwareprobleme diagnostizieren. Indem Sie lernen, sie zu erstellen, können Sie robuste Systeme entwerfen, die unter allen Bedingungen zuverlässig funktionieren.

Der Prozess erfordert Geduld und Aufmerksamkeit für Details. Jede Flanke, jede Verzögerung und jede Spannungsebene ist wichtig. Je schneller und komplexer eingebettete Systeme werden, desto stärker wird die Abhängigkeit von präzisen Zeitdiagrammen sein. Behandeln Sie sie als kritische Spezifikationen, nicht als optionale Dokumentation.

Beginnen Sie mit der Analyse der Datenblätter der Komponenten, die Sie verwenden. Suchen Sie nach Zeitangaben. Zeichnen Sie dann die Diagramme basierend auf diesen Werten. Vergleichen Sie Ihre Zeichnungen mit tatsächlichen Messwerten aus Ihren Werkzeugen. Dieser Zyklus aus Vorhersage und Überprüfung baut die Intuition auf, die für die hochwertige Entwicklung eingebetteter Systeme notwendig ist.

Denken Sie daran, dass ein Diagramm ein Kommunikationswerkzeug ist. Es sollte die notwendigen Informationen für einen anderen Ingenieur mit minimaler Mehrdeutigkeit vermitteln. Klare, genaue Zeitdiagramme reduzieren die Entwicklungszeit und verhindern kostspielige Hardware-Revisionen. Investieren Sie die Zeit, diese Fähigkeit zu meistern, und sie wird sich im Laufe Ihrer Ingenieurkarriere lohnen.