Digitale Systeme verlassen sich auf präzise Synchronisation, um korrekt zu funktionieren. Ohne genaue Zeitsteuerung werden Datenkorruption, Systemabstürze und Sicherheitsausfälle unvermeidlich. Ein Zeitdiagramm bietet eine visuelle Darstellung der Signaländerungen im Zeitverlauf und vermittelt ein klares Verständnis der Beziehungen zwischen Taktrunden, Datengültigkeit und Steuersignalen. Dieser Leitfaden untersucht die entscheidende Rolle von Zeitdiagrammen in verschiedenen Branchen und erläutert praktische Beispiele sowie technische Lösungen für häufige Herausforderungen.

🔍 Das Verständnis der Grundlagen

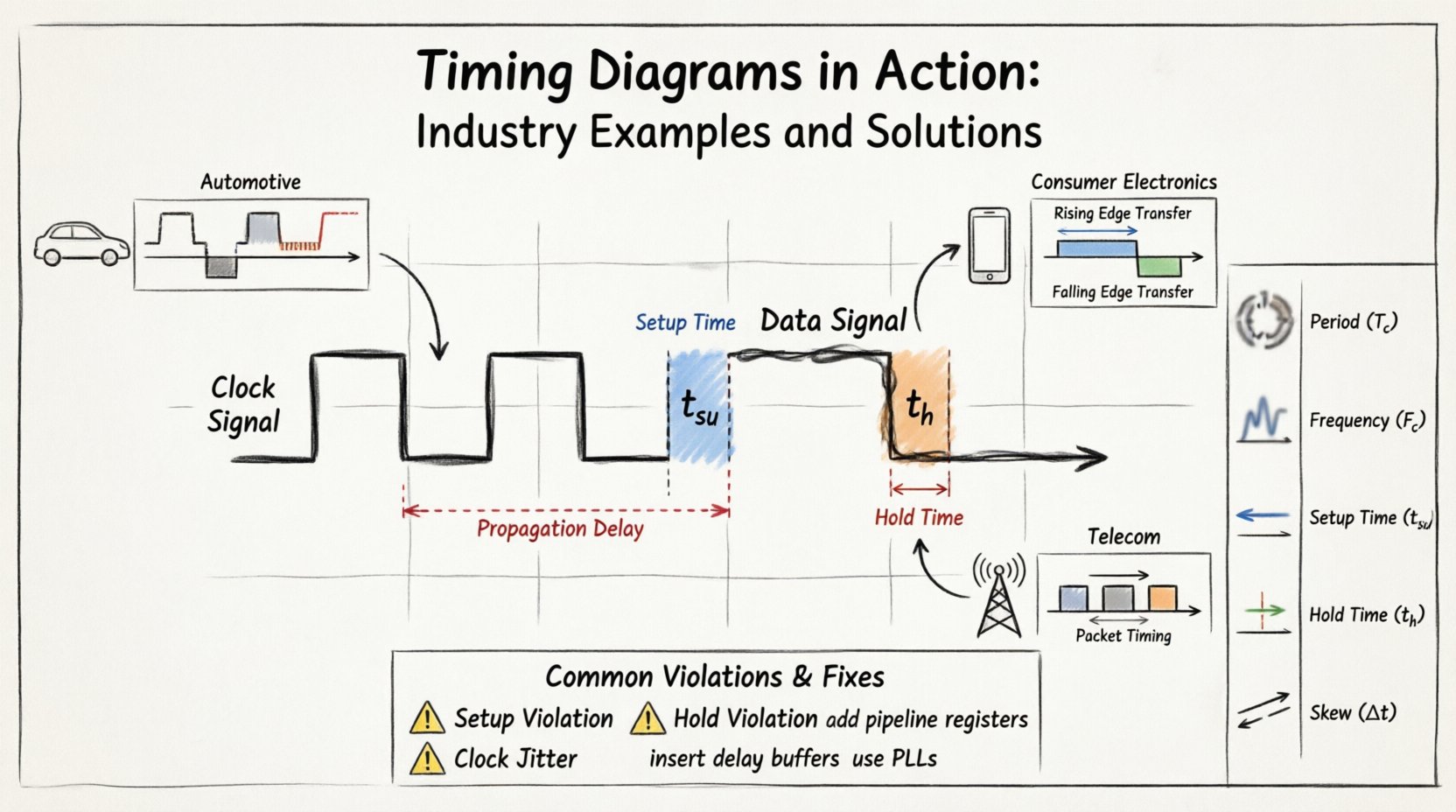

Bevor man sich spezifischen Anwendungen zuwendet, ist es unerlässlich, die zentralen Komponenten eines Zeitdiagramms zu verstehen. Diese Diagramme zeigen das Verhalten von Signalen im Verhältnis zu einem Referenztakt. Sie sind nicht einfach nur Zeichnungen, sondern mathematische Einschränkungen, die das Verhalten der Hardware bestimmen.

- Signalflanken: Der Übergang von niedrig zu hoch (steigende Flanke) oder von hoch zu niedrig (fallende Flanke) löst Zustandsänderungen in der sequenziellen Logik aus.

- Taktrate: Die Dauer zwischen zwei aufeinanderfolgenden Flanken desselben Polarity definiert die verfügbare Zeit, die benötigt wird, damit die Logik sich stabilisiert.

- Ausbreitungsverzögerung: Die Zeit, die ein Signal benötigt, um von einem Eingangspin zu einem Ausgangspin durch Logikgatter zu gelangen.

- Setup- und Haltezeiten: Kritische Einschränkungen, die sicherstellen, dass die Daten vor und nach der Taktränder stabil sind.

Wenn diese Parameter verletzt werden, kann die Schaltung in einen metastabilen Zustand geraten, was zu unvorhersehbarem Verhalten führt. Ingenieure verwenden Zeitdiagramme, um zu überprüfen, ob die physische Implementierung eines Entwurfs diesen logischen Anforderungen entspricht.

🚗 Automotive-Elektronik: Zeitgesteuerte Sicherheitskritik

Die Automobilindustrie verlangt das höchste Maß an Zuverlässigkeit. Fahrzeuge enthalten Dutzende von elektronischen Steuergeräten (ECUs), die über Busse wie CAN (Controller Area Network), LIN (Local Interconnect Network) und FlexRay kommunizieren. Die Zeitanalyse hier geht nicht nur um Geschwindigkeit, sondern um Determinismus und Sicherheit.

1. CAN-Bus-Arbitrierung

Der CAN-Bus ermöglicht es mehreren Knoten, über einen einzigen Draht zu kommunizieren. Das Zeitdiagramm der CAN-Arbitrierung zeigt auf, wie die Priorität bei Buskonflikten festgelegt wird.

- Dominant gegenüber Rezessiv: Logische Pegel werden durch Spannungszustände dargestellt. Ein dominanter Bit (0) überschreibt einen rezessiven Bit (1).

- Synchronisation: Knoten synchronisieren sich am Beginn des Frame-Bits mithilfe von Synchronisationssegmenten.

- Abtastpunkt:Die Daten werden zu einem bestimmten Prozentsatz der Bitzeit abgetastet, um Rauschen zu vermeiden.

Wenn der Abtastpunkt zu nahe an der Kante liegt, kann Rauschen zu Bitfehlern führen. Ist er zu spät, kann das Signal nicht stabil sein. Zeitdiagramme helfen Ingenieuren, den Abtastpunkt korrekt einzustellen, typischerweise bei etwa 80 % der Bitzeit.

2. ADC-Abtastung bei Sensorfusion

Moderne Fahrzeuge verwenden mehrere Sensoren (Radar, Lidar, Kameras), um eine Wahrnehmung der Umgebung zu ermöglichen. Analog-Digital-Wandler (ADCs) müssen Signale in präzisen Abständen abtasten, um Aliasing zu vermeiden.

- Taktrauschen:Schwankungen in der Taktranderzeit führen zu Rauschen im digitalisierten Signal.

- Verzögerung:Die Zeit von der Sensoreingabe bis zur verarbeiteten Datenausgabe muss für die Echtzeitsteuerung minimiert werden.

- Interleaving: Mehrere ADCs arbeiten oft parallel. Zeitdiagramme stellen sicher, dass ihre Phasen ausgerichtet sind, um Lücken in den Daten zu vermeiden.

📱 Verbraucherelektronik: Hochgeschwindigkeitsschnittstellen

Verbrauchsgeräte legen Wert auf Leistung und Energieeffizienz. Schnittstellen wie DDR-Speicher und Bildschirmlinken erfordern engmaschige Zeitfenster, um hohe Bandbreite zu erreichen, ohne den Energieverbrauch zu erhöhen.

1. DDR-Speicherschnittstellen

DDR-Speicher überträgt Daten sowohl am steigenden als auch am fallenden Flanken des Taktsignals. Dadurch verdoppelt sich die effektive Datenrate, jedoch halbiert sich das Zeitfenster für die Datenstabilität.

| Parameter | Definition | Auswirkung einer Verletzung |

|---|---|---|

| Setup-Zeit | Zeit, in der die Daten stabil sein müssen, bevor die Taktflanke eintritt | Verpasster Datenübertragung, Systemhängen |

| Hold-Zeit | Zeit, in der die Daten stabil bleiben müssen, nachdem die Taktflanke eingetreten ist | Beschädigte Daten, Bitumkehrungen |

| Taktschiefe | Unterschied in der Ankunftszeit des Taktsignals bei verschiedenen Chips | Verkleinertes Zeitfenster, Instabilität |

| Taktfrequenzverhältnis | Verhältnis der Hochzeit zur Gesamtperiode | Ungleichgewichtige Leistung, erhöhtes Jitter |

Bei DDR4 und DDR5 laufen der Befehls- und Adressbus oft mit einer niedrigeren Frequenz als der Datenbus. Zeitdiagramme müssen die quellensynchrone Strobe-Signale (DQS) berücksichtigen, die die Daten begleiten, um gültige Fenster anzugeben.

2. Bildschirmschnittstellen (MIPI DSI)

Mobile Geräte verwenden die MIPI Display Serial Interface (DSI), um den Prozessor mit dem Bildschirm zu verbinden. Diese Schnittstelle verwendet Hochgeschwindigkeits-Differenzialkanäle.

- LP-Befehlsmodus:Niedrigenergiemodus zum Senden von Befehlen, der auf strenge Zeitplanung für Wake-up-Sequenzen angewiesen ist.

- HS-Datenmodus:Hochgeschwindigkeitsübertragung, bei der die Taktrückgewinnung im Datenstrom erfolgt.

- Umschaltzeit:Die Zeit, die benötigt wird, um von der Sendemodus auf den Empfangsmodus auf demselben Kanal umzuschalten.

Eine Fehlausrichtung in diesen Zeitdiagrammen führt zu Bildschirmartefakten, Flimmern oder einem vollständigen Verlust des Videoausgangs.

📡 Telekommunikation: Latenz und Bandbreite

In der Telekommunikation ist Timing gleichbedeutend mit Latenz. Die Paketlieferzeiten und die Synchronisation über verteilte Netzwerke sind entscheidend für Dienste wie 5G und Hochfrequenzhandel.

1. PCIe-Signaling

Der Standard Peripheral Component Interconnect Express (PCIe) wird weit verbreitet zur Verbindung von Hochgeschwindigkeitskomponenten verwendet. Er nutzt serielle Kanäle mit eingebetteten Takten oder quellensynchronen Takten.

- Gleichung:Die Signalintegrität verschlechtert sich mit der Entfernung. Zeitdiagramme zeigen, wie Gleichungsfilter für Verluste ausgleichen.

- Link-Training: Eine Folge zeitlich abgestimmter Zustände, um die Linkgeschwindigkeit und die Kanalbreite festzulegen.

- Flusssteuerung: Zeitfenster für die kreditbasierte Flusssteuerung verhindern Pufferüberläufe.

2. Ethernet-PHYs

Standard-Ethernet basiert auf einem gemeinsamen Takt oder der Taktwiederherstellung. Gigabit-Ethernet und darüber hinaus verwenden die 8b/10b-Codierung, um ausreichend Übergänge für die Taktwiederherstellung zu gewährleisten.

- Ruhephasen: Definierte Zeitfenster, in denen keine Daten gesendet werden, um die Synchronisation aufrechtzuerhalten.

- Start des Rahmen-Trennzeichens: Ein spezifisches Bitmuster, das den Beginn eines Pakets markiert und eine präzise Erkennungszeit erfordert.

- Paketabstand: Eine obligatorische Verzögerung zwischen Paketen, um dem Hardware-Reset Zeit zu geben.

⚠️ Häufige Zeitverletzungen und Lösungen

Selbst bei sorgfältiger Gestaltung treten Zeitverletzungen auf. Die Identifizierung der Ursache erfordert die Analyse des Zeitdiagramms, um zu sehen, wo die Signale von den Erwartungen abweichen.

1. Setup-Zeit-Verletzungen

Tritt auf, wenn Daten zu spät eintreffen, um von der Taktflanke erfasst zu werden.

- Ursachen:Übermäßige Logiktiefe, lange Leiterbahnverzögerungen oder Taktschiefe.

- Lösungen:

- Pipeline-Register einfügen, um lange Pfade zu unterbrechen.

- Logik-Synthese optimieren, um die Gatteranzahl zu reduzieren.

- Die Taktfrequenz anpassen, um mehr Zeit zur Verfügung zu stellen.

2. Haltezeit-Verletzungen

Tritt auf, wenn die Daten zu schnell nach der Taktkante geändert werden, wodurch der erfasste Wert überschrieben wird.

- Ursachen:Kurze Pfadverzögerungen, Taktschiefe, bei der der Erfassungstakt zu spät eintrifft.

- Lösungen:

- Füge Verzögerungspuffer in den Datenpfad ein.

- Verwende Retiming-Techniken, um Pfade auszugleichen.

- Stelle sicher, dass das Taktausgabernetzwerk minimale Schiefe aufweist.

3. Taktschiefe und Jitter

Schiefe ist die Differenz in der Ankunftszeit des Taktsignals bei verschiedenen Registern. Jitter ist die kurzfristige Variation der Taktkante.

- Auswirkungen:Verringert die effektive Zeitreserve, die für die Daten zur Verfügung steht.

- Lösungen:

- Verwende Taktgeneratoren mit geringem Jitter.

- Entwerfe ausgewogene Taktbäume mit gleich langen Spuren.

- Implementiere Phasenregelkreise (PLLs), um Taktsignale zu bereinigen.

✅ Best Practices für die Implementierung

Ein robustes Timing erfordert einen systematischen Ansatz über den gesamten Entwicklungszyklus hinweg. Dokumentation und Verifikation sind genauso wichtig wie die Schaltung selbst.

1. Definiere Timing-Beschränkungen frühzeitig

Warte nicht bis zur Implementierungsphase, um die Timing-Anforderungen zu definieren. Dokumentiere die Taktfrequenzen, Eingangsverzögerungen und Ausgangsverzögerungen in der Entwurfsbeschreibung. Dadurch stellen alle Beteiligten sicher, dass sie die Grenzen des Systems verstehen.

2. Verwende die statische Zeitanalyse

Werkzeuge zur statischen Zeitanalyse (STA) berechnen die ungünstigsten Verzögerungspfade, ohne jede Eingabekombination zu simulieren. Diese Methode ist effizient und berücksichtigt alle möglichen Zustände, sodass keine Zeitverletzungen übersehen werden.

3. Validiere mit Simulation

Obwohl die STA leistungsstark ist, bietet die dynamische Simulation einen Einblick in das Signalverhalten unter bestimmten Bedingungen. Verwende die Simulation, um kritische Pfade zu überprüfen, insbesondere solche, die asynchrone Logik oder komplexe Zustandsautomaten betreffen.

4. Betrachtungen im physischen Entwurf

Die physische Anordnung des Chips oder der Platine beeinflusst das Timing direkt.

- Leiterbahnlänge:Längere Leiterbahnen führen zu höherer Kapazität und Widerstand, was die Verzögerung erhöht.

- Kreuzkoppelung:Nachbar-Signale können Rauschen erzeugen, was zu falschen Übergängen führt.

- Versorgungsnetzwerk-Rauschen: Spannungseinbrüche können die Schaltgeschwindigkeit von Gattern verlangsamen.

🛠️ Fehlerbehebung bei realen Szenarien

Wenn ein System die Zeitvorgaben nicht erfüllt, ist ein strukturierter Debugging-Prozess notwendig. Die folgenden Schritte skizzieren einen logischen Ansatz zur Behebung von Zeitverzögerungsproblemen.

- Schritt 1: Pfad identifizieren.Suchen Sie den spezifischen Register-zu-Register-Pfad, der den Ausfall verursacht. Sehen Sie sich die Zeitverzögerungsberichte auf den negativsten Slack an.

- Schritt 2: Wellenformen analysieren.Verwenden Sie einen Zeitdiagramm-Viewer, um die tatsächlichen Signalübergänge zu überprüfen. Vergleichen Sie diese mit den erwarteten Werten.

- Schritt 3: Uhrsignal prüfen.Stellen Sie die Qualität des Uhrsignals sicher. Suchen Sie nach Jitter, Verzerrung des Tastverhältnisses oder Störungen.

- Schritt 4: Einschränkungen überprüfen.Stellen Sie sicher, dass die Einschränkungen in der Entwurfsdatei der physischen Realität der Hardware entsprechen.

- Schritt 5: Iterieren.Nehmen Sie Änderungen an der Logik oder der Anordnung vor und führen Sie die Zeitverzögerungsanalyse erneut durch.

📊 Zusammenfassung der Zeitparameter

Zur schnellen Nachschlagemöglichkeit finden Sie hier eine Zusammenfassung der wichtigsten Zeitparameter, die in verschiedenen Branchen verwendet werden.

| Parameter | Symbol | Typische Einheit | Beschreibung |

|---|---|---|---|

| Periode | Tc | ns | Zeit zwischen aufeinanderfolgenden Taktkanten |

| Frequenz | Fc | Hz | Inverses der Periode |

| Setup-Zeit | tsu | ns | Datenstabilität erforderlich vor Taktkante |

| Haltezeit | th | ns | Datenstabilität erforderlich nach Taktkante |

| Ausbreitungsverzögerung | tpd | ns | Zeit, die ein Signal benötigt, um durch die Logik zu gelangen |

| Verzögerungsdifferenz | Δt | ps | Zeitunterschied beim Eintreffen des Taktsignals |

🔄 Verwaltung asynchroner Designs

Nicht alle Systeme laufen mit einem einzigen Takt. Asynchrone Designs beinhalten Datenübertragungen zwischen verschiedenen Taktbereichen. Dies birgt das Risiko von Metastabilität, bei der ein Flip-Flop in einen undefinierten Zustand gerät.

- Synchronisationsketten: Verwenden Sie einen mehrstufigen Synchronisierer (typischerweise zwei Flip-Flops), um dem Signal Zeit zum Stabilisieren zu geben, bevor es verwendet wird.

- Handshake-Protokolle: Implementieren Sie Anforderungs-Acknowledgement-Mechanismen, um sicherzustellen, dass der Empfänger bereit ist, bevor Daten gesendet werden.

- FIFO-Puffer: Verwenden Sie First-In-First-Out-Speicherstrukturen, um die Geschwindigkeiten von Produzent und Verbraucher zu entkoppeln.

Zeitdiagramme für asynchrone Designs zeigen die Beziehung zwischen den beiden unabhängigen Taktquellen. Entscheidend ist, sicherzustellen, dass der Datenpfad ausreichend Zeit hat, sich zu stabilisieren, bevor der empfangende Takt ihn abtastet.

🌟 Abschließende Gedanken

Zeitdiagramme sind die Grundlage der Verifikation digitaler Systeme. Sie schließen die Lücke zwischen abstrakter Logik und physischer Realität. Durch das Verständnis der Feinheiten von Ansprechzeit, Haltezeit, Taktskew und Jitter können Ingenieure Systeme entwerfen, die robust, effizient und zuverlässig sind.

Unabhängig davon, ob in Sicherheitssystemen für Fahrzeuge, Verbraucherelektronik oder Telekommunikationsinfrastruktur – die Prinzipien bleiben gleich. Präzision in der Zeitsteuerung führt zu Präzision in der Leistung. Kontinuierliche Überwachung und Einhaltung bewährter Praktiken stellen sicher, dass Designs während ihres gesamten Lebenszyklus funktionsfähig bleiben. Mit fortschreitender Technologie und steigenden Geschwindigkeiten wird die Bedeutung detaillierter Zeitanalyse nur zunehmen.

Für Teams, die die Qualität ihres Designs verbessern möchten, ist die Investition von Zeit in genaue Zeitdiagramme und Überprüfungsabläufe unerlässlich. Sie verringert das Risiko, senkt die Kosten für die Fehlersuche und stellt sicher, dass das Endprodukt seinen Spezifikationen entspricht. Mit den richtigen Werkzeugen und Methoden werden Zeitprobleme beherrschbare Einschränkungen statt Hindernisse.