Digitale Systeme verlassen sich auf präzise Synchronisation, um korrekt zu funktionieren. Wenn Signale zum falschen Zeitpunkt eintreffen, treten Logikfehler auf, was zu unvorhersehbarem Verhalten führt. Das Verständnis, wie man diese Probleme analysiert und behebt, ist für alle, die digitale Logik, Computertechnik oder Elektronik studieren, unerlässlich. Dieser Leitfaden behandelt die zentralen Konzepte und praktischen Schritte zur Identifizierung und Lösung von Zeitverzögerungsproblemen in sequenziellen Schaltungen und bei der Datenübertragung.

Verständnis von Taktsignalen und -kanten ⏱️

Im Herzen der meisten digitalen Schaltungen steht das Taktsignal. Dieses periodische Signal bestimmt, wann Daten abgetastet werden und wann Zustandsänderungen stattfinden. Die Fehlersuche beginnt oft damit, die Integrität dieses grundlegenden Signals zu überprüfen.

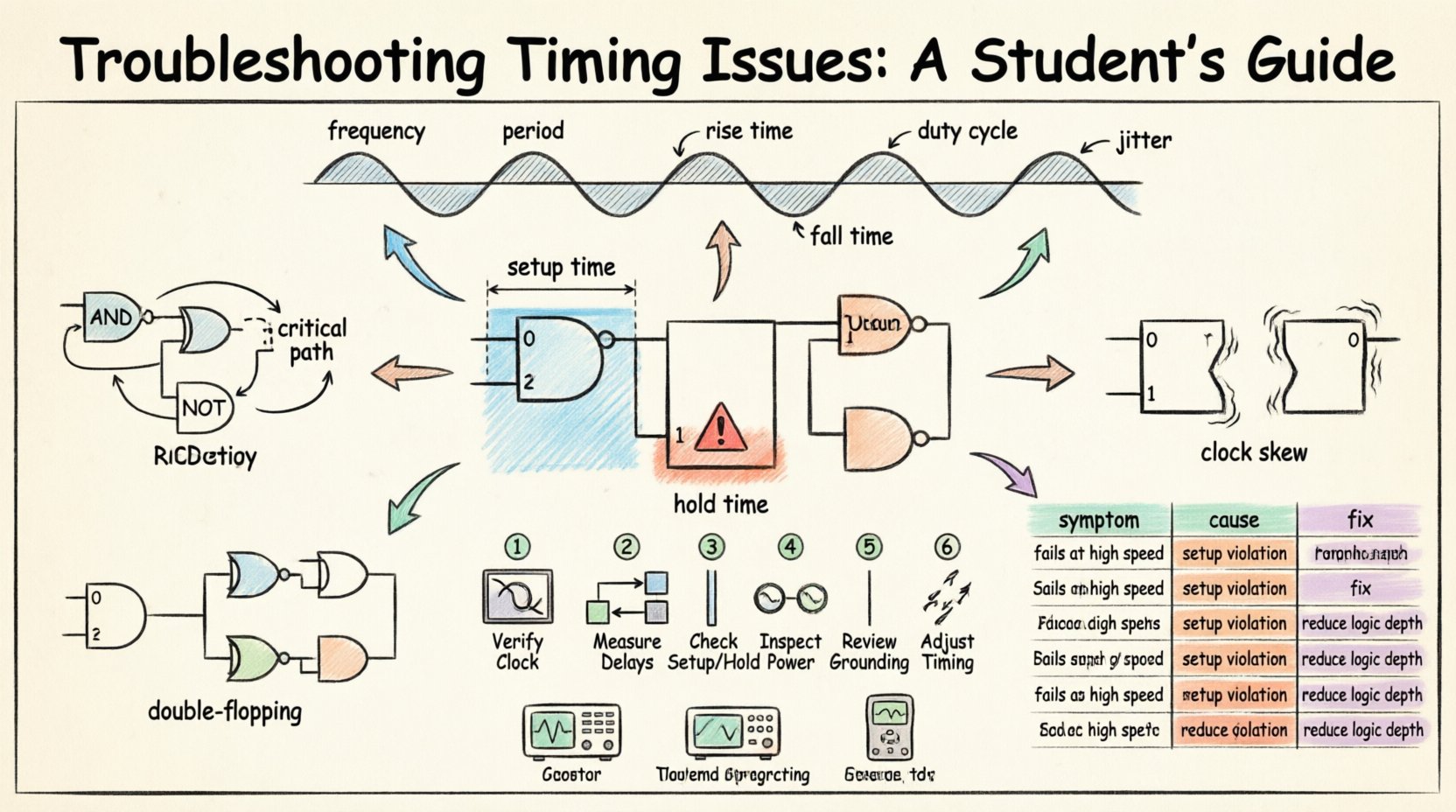

- Frequenz und Periode: Die Taktfrequenz bestimmt die Betriebsgeschwindigkeit. Die Periode ist die Dauer eines vollständigen Zyklus. Wenn die Schaltung einen 100-MHz-Takt erfordert, beträgt die Periode 10 Nanosekunden. Jede Abweichung wirkt sich auf die gesamte nachfolgende Logik aus.

- Anstiegs- und Abfallzeiten: Ein perfektes Rechtecksignal ist theoretisch. Reale Signale haben endliche Anstiegs- und Abfallzeiten. Wenn der Übergang zu langsam ist, kann das Signal zu lange im undefinierten Spannungsbereich verweilen, was zu mehrfachen Umschaltungen oder Logikfehlern führt.

- Tastverhältnis: Dies ist das Verhältnis der Zeit, in der das Signal hoch ist, zur Gesamtperiode. Ein Tastverhältnis von 50 % ist Standard, aber einige Schaltungen erfordern asymmetrische Zyklen. Abweichungen können die Zeitabstände für Setup- oder Hold-Anforderungen beeinflussen.

Beim Untersuchen einer Schaltung verwenden Sie ein Oszilloskop oder einen Logikanalysator, um das Taktsignal zu betrachten. Achten Sie auf Rauschspitzen, Ringen oder übermäßige Jitter. Jitter bezeichnet die Abweichung der Taktkante von ihrer idealen Position in der Zeit. Hoher Jitter verringert den effektiven Zeitabstand, der für das Ansprechen der Daten zur Verfügung steht.

Setup- und Hold-Zeit-Verletzungen ⚠️

Dies sind die häufigsten Zeitverzögerungsverletzungen, die bei der Entwicklung sequenzieller Logik auftreten. Flip-Flops und Latches haben spezifische Anforderungen an die Stabilität der Daten relativ zur Taktkante.

Setup-Zeit

Die Setup-Zeit ist die minimale Zeitspanne vor der Taktkante, in der die Daten stabil sein müssen. Wenn die Daten zu nahe an der Taktkante wechseln, kann das Flip-Flop den korrekten Wert möglicherweise nicht erfassen.

- Die Einschränkung:Die Propagationsverzögerung der kombinatorischen Logik, die das Flip-Flop versorgt, muss kleiner sein als die Taktpause abzüglich der Setup-Zeit.

- Das Symptom:Das System könnte bei niedrigeren Frequenzen funktionieren, versagt aber bei steigender Geschwindigkeit. Zufällige Bitfehler treten häufig am Ausgang auf.

- Die Lösung: Verringern Sie die Logiktiefe zwischen den Registern, erhöhen Sie die Taktpause oder verwenden Sie schnellere Komponenten.

Hold-Zeit

Die Hold-Zeit ist die minimale Zeitspanne nach der Taktkante, in der die Daten stabil bleiben müssen. Wenn die Daten zu früh nach der Taktkante wechseln, kann das Flip-Flop den erfassten Wert verlieren.

- Die Einschränkung: Die Propagationsverzögerung der kombinatorischen Logik muss größer sein als die Hold-Zeit des Ziel-Flip-Flops.

- Das Symptom: Hold-Verletzungen treten oft unabhängig von der Frequenz auf. Dies liegt daran, dass die Verzögerung absolut ist und nicht relativ zur Periode.

- Die Lösung: Fügen Sie Verzögerungspuffer in den Datenpfad ein, um das Signal zu verlangsamen, oder überarbeiten Sie die Logik, um die Verzögerung zu verringern.

Es ist entscheidend, zwischen diesen beiden zu unterscheiden. Setup-Verletzungen sind frequenzabhängig, während Hold-Verletzungen pfadabhängig sind. Ein häufiger Fehler besteht darin, eine Hold-Verletzung durch Verlangsamung des Taktes zu beheben; dies funktioniert nicht und kann die Situation sogar verschlimmern.

Propagationsverzögerungen und Pfananalyse 📉

Signale reisen nicht sofort. Jeder Draht, jede Schaltung und jedes Bauteil verursacht eine Verzögerung. Die Analyse dieser Verzögerungen ist entscheidend, um sicherzustellen, dass die Daten rechtzeitig eintreffen.

- Verzögerung der kombinatorischen Logik: Dies ist die Zeit, die ein Signal benötigt, um durch Gatter wie AND, OR und NOT zu gelangen. Lange Ketten von Gattern verursachen erhebliche Latenz.

- Verbindungsverzögerung: Auf einer physischen Platine haben Drähte Kapazität und Widerstand. Längere Spuren verursachen mehr Verzögerung. Dies wird oft als RC-Netzwerk modelliert.

- Pin-zu-Pin-Verzögerung: Die Zeit von einer Takteingabe bis zu einer Datenausgabe in einem Bauteil. Dies ist in Datenblättern meist angegeben.

Beim Beheben von Problemen sollte der kritische Pfad aufgezeichnet werden. Dies ist der längste Verzögerungspfad zwischen zwei sequenziellen Elementen. Wenn der kritische Pfad die Taktfrequenz überschreitet, wird die Schaltung fehlschlagen. Um ihn zu finden, berechnen Sie die Summe der Verzögerungen für alle möglichen Pfade und identifizieren Sie das Maximum.

Taktschiefe und Jitter 📶

Selbst wenn die Taktsquelle perfekt ist, kann das Signal zu verschiedenen Komponenten zu unterschiedlichen Zeiten eintreffen. Dieses Phänomen wird als Schiefe bezeichnet.

- Taktschiefe: Dies tritt auf, wenn das Taktsignal unterschiedliche Strecken zurücklegt, um verschiedene Flip-Flops zu erreichen. Positive Schiefe verzögert die Erfassung des Taktsignals, was die Setup-Zeit erleichtert, aber die Hold-Zeit verschärft. Negative Schiefe verschärft die Setup-Zeit, aber erleichtert die Hold-Zeit.

- Taktjitter: Kurzfristige Schwankungen in der Taktrandzeit. Jitter reduziert das verfügbare Zeitbudget für die Datensetzung.

- Drift: Langsame Änderungen der Taktfrequenz über die Zeit aufgrund von Temperatur- oder Stromversorgungsschwankungen.

Schiefe wird in komplexen Designs oft durch die Synthese von Takträdern verwaltet. In Studentenprojekten wird sie meist dadurch minimiert, dass die Taktspur gleichmäßig verlegt und kurz gehalten wird. Falls eine Schiefe vermutet wird, sollte der Takt an mehreren Stellen im Schaltkreis gleichzeitig gemessen werden.

Metastabilität und asynchrone Eingänge 🌀

Wenn die Daten gleichzeitig mit dem Taktrand wechseln, gerät ein Flip-Flop in einen metastabilen Zustand. Er stabilisiert sich nicht sofort auf 0 oder 1, sondern bleibt auf einem Zwischenspannungsniveau.

- Das Risiko:Metastabilität kann sich durch das System ausbreiten und logische Fehler verursachen, die schwer nachzustellen sind.

- Asynchrone Signale:Eingaben von externen Schaltern oder Kommunikationsports stimmen oft nicht mit dem internen Takt überein. Diese müssen synchronisiert werden.

- Doppeltes Flipping: Eine gängige Methode zur Behebung von Metastabilität besteht darin, das Signal durch zwei Flip-Flops in Serie zu leiten. Das erste erfasst den metastabilen Zustand, und das zweite löst ihn im nächsten Zyklus auf.

Behandeln Sie asynchrone Eingänge stets als potenzielle Quellen von Metastabilität. Verbinden Sie sie nicht direkt mit Logik, die strenge Zeitvorgaben erfordert. Verwenden Sie Synchronisierschaltungen, um einen sicheren Datenübertrag zwischen verschiedenen Taktdomänen zu gewährleisten.

Ein schrittweiser Fehlerbehebungsablauf 🛠️

Wenn ein Zeitproblem auftritt, verfolgen Sie einen strukturierten Ansatz, um die Ursache zu isolieren. Zufällige Änderungen werden wahrscheinlich keine Ergebnisse bringen.

- Überprüfen Sie den Takt: Überprüfen Sie Frequenz, Tastverhältnis und Amplitude. Stellen Sie sicher, dass das Signal stabil und sauber ist.

- Verzögerungen messen: Verwenden Sie einen Logikanalysator, um Eingangs- und Ausgangssignale zu erfassen. Messen Sie die tatsächliche Ausbreitungsverzögerung der Strecke.

- Setup- und Haltezeiten prüfen: Berechnen Sie, ob die Strecke die Setup- und Haltezeiten aufgrund der gemessenen Verzögerungen erfüllt.

- Stromversorgung überprüfen: Spannungsabfälle können Gatter verlangsamen. Stellen Sie sicher, dass die Stromversorgung stabil ist und ausreichend Strom liefert.

- Masseverbindung überprüfen: Eine schlechte Masseverbindung kann Rauschen verursachen, das Timing-Fehler nachahmt. Prüfen Sie auf Massekreise und geteilte Rückleitungen.

- Zeitverhalten anpassen: Wenn das Design flexibel ist, passen Sie die Taktfrequenz an oder fügen Sie Puffer hinzu, um die Strecke auszugleichen.

Dokumentation ist während dieses Prozesses entscheidend. Protokollieren Sie die Wellenformen und Messwerte. Diese Daten helfen dabei, das erwartete Verhalten mit der tatsächlichen Leistung zu vergleichen.

Referenztabelle häufiger Fehler 📊

Verwenden Sie diese Tabelle als schnellen Leitfaden zur Diagnose spezifischer Symptome.

| Beobachtetes Symptom | Wahrscheinliche Ursache | Empfohlene Maßnahme |

|---|---|---|

| System versagt bei hoher Geschwindigkeit | Setup-Zeit-Verletzung | Reduzieren Sie die Logiktiefe oder verlängern Sie die Taktperiode |

| System versagt bei niedriger Geschwindigkeit | Haltezeit-Verletzung | Fügen Sie Verzögerungspuffer zur Datenstrecke hinzu |

| Zufällige Bitumkehrungen | Signallärm oder Jitter | Prüfen Sie die Abschirmung und Stabilität der Stromversorgung |

| Ausgang hängt fest oder setzt zurück | Metastabilität | Implementieren Sie Synchronisierketten |

| Inkonsistentes Verhalten | Taktschiefe | Balancieren Sie die Längen der Taktspur |

| Keine Ausgabe überhaupt | Takt nicht aktiviert | Überprüfen Sie die Taktverteilung und die Aktivierungssignale |

Werkzeuge und Messgeräte 📏

Während Simulationswerkzeuge nützlich sind, erfordert die physische Überprüfung oft spezifische Hardware. Das Verständnis, wie man diese Geräte korrekt verwendet, ist Teil des Fähigkeitsprofils zur Fehlerbehebung.

- Oszilloskop:Unverzichtbar zum Anzeigen von Spannungsniveaus und Signalform. Verwenden Sie hochohmige Sonden, um eine Belastung der Schaltung zu vermeiden.

- Logikanalysator:Besser geeignet für digitale Signale. Es erfasst den Logikzustand (0 oder 1) über die Zeit. Es kann auf bestimmte Muster auslösen, um Fehler zu isolieren.

- Frequenzmesser:Wird verwendet, um die genaue Frequenz der Taktsquelle zu überprüfen, wenn kein Oszilloskop zur Verfügung steht.

Stellen Sie sicher, dass die Sonde korrekt kompensiert ist. Eine nicht kompensierte Sonde kann die Signalform verzerren und zu falschen Schlussfolgerungen über Anstiegszeiten und Verzögerungen führen.

Abschließende Überlegungen zur Signalintegrität 🔒

Zeitverzögerungsprobleme sind oft Symptome umfassender Signalintegritätsprobleme. Je schneller die Schaltungen werden, desto wichtiger werden die physikalischen Eigenschaften der Platine.

- Kreuzstörungen:Signale auf benachbarten Leitungen können sich gegenseitig stören. Halten Sie Hochgeschwindigkeitsleitungen von empfindlichen Leitungen getrennt.

- Impedanzanpassung: Wenn die Spurlänge nicht mit dem Treiber oder Empfänger übereinstimmt, treten Reflexionen auf. Diese Reflexionen können wie Zeitverzögerungen erscheinen.

- Wärmeeinflüsse: Wenn Bauteile erwärmen, ändern sich ihre elektrischen Eigenschaften. Dies kann die Ausbreitungsverzögerungen verändern und zu Zeitverzögerungsfehlern unter Last führen.

Das Entwerfen für die Zeitsteuerung erfordert einen ganzheitlichen Ansatz. Es geht nicht nur um Logikgatter, sondern um das physische Medium, durch das Signale reisen. Durch Einhaltung dieser Prinzipien können Studierende robuste Systeme entwickeln, die unter verschiedenen Bedingungen zuverlässig funktionieren.

Regelmäßige Übung mit echter Hardware hilft, diese Konzepte zu verinnerlichen. Die Theorie liefert das Fundament, aber das praktische Debugging baut das nötige Bauchgefühl auf, um komplexe Zeitverzögerungsprobleme effizient zu lösen.