Di dunia elektronika digital dan teknik komputer, sinyal tidak ada dalam ruang hampa. Mereka bergerak melalui jalur, melewati gerbang, dan masuk ke prosesor dengan batasan waktu tertentu. Untuk memahami bagaimana suatu sistem berfungsi, insinyur harus membayangkan bagaimana sinyal-sinyal ini berubah seiring waktu. Visualisasi ini dicapai melalui diagram waktu. Bagi pemula, grafik-grafik ini mungkin tampak seperti hieroglif yang rumit, tetapi sebenarnya merupakan alat paling dasar untuk mendiagnosis masalah dan merancang logika digital.

Panduan ini memberikan penjelasan menyeluruh mengenai diagram waktu. Kami akan mengeksplorasi anatomi suatu sinyal, parameter penting yang menentukan keandalan, serta kesalahan umum yang menyebabkan kegagalan sistem. Baik Anda sedang belajar untuk ujian atau merancang sirkuit mikrokontroler pertama Anda, memahami diagram-diagram ini sangat penting.

🧠 Apa Itu Diagram Waktu?

Diagram waktu adalah representasi grafis dari keadaan sinyal digital sepanjang waktu. Berbeda dengan skema sirkuit, yang menunjukkanapayang terhubung keapa, diagram waktu menunjukkankapankejadian terjadi. Diagram ini memplot tingkat tegangan terhadap sumbu waktu, memungkinkan insinyur melihat urutan kejadian.

Diagram-diagram ini sangat diperlukan karena beberapa alasan:

- Pemecahan Masalah:Mereka mengungkap kondisi persaingan di mana sinyal tiba secara tidak urut.

- Verifikasi:Mereka memastikan bahwa suatu sirkuit memenuhi spesifikasi kecepatan yang dibutuhkan.

- Dokumentasi:Mereka berfungsi sebagai referensi tentang bagaimana chip-chip yang berbeda berkomunikasi.

- Desain:Mereka membantu menentukan frekuensi jam maksimum yang dapat didukung suatu sistem.

Ketika Anda melihat diagram waktu, Anda sedang melihat gambaran singkat dari perilaku fisik elektron yang bergerak melalui suatu sistem. Diagram ini menangkap kenyataan tentang latensi, propagasi, dan sinkronisasi.

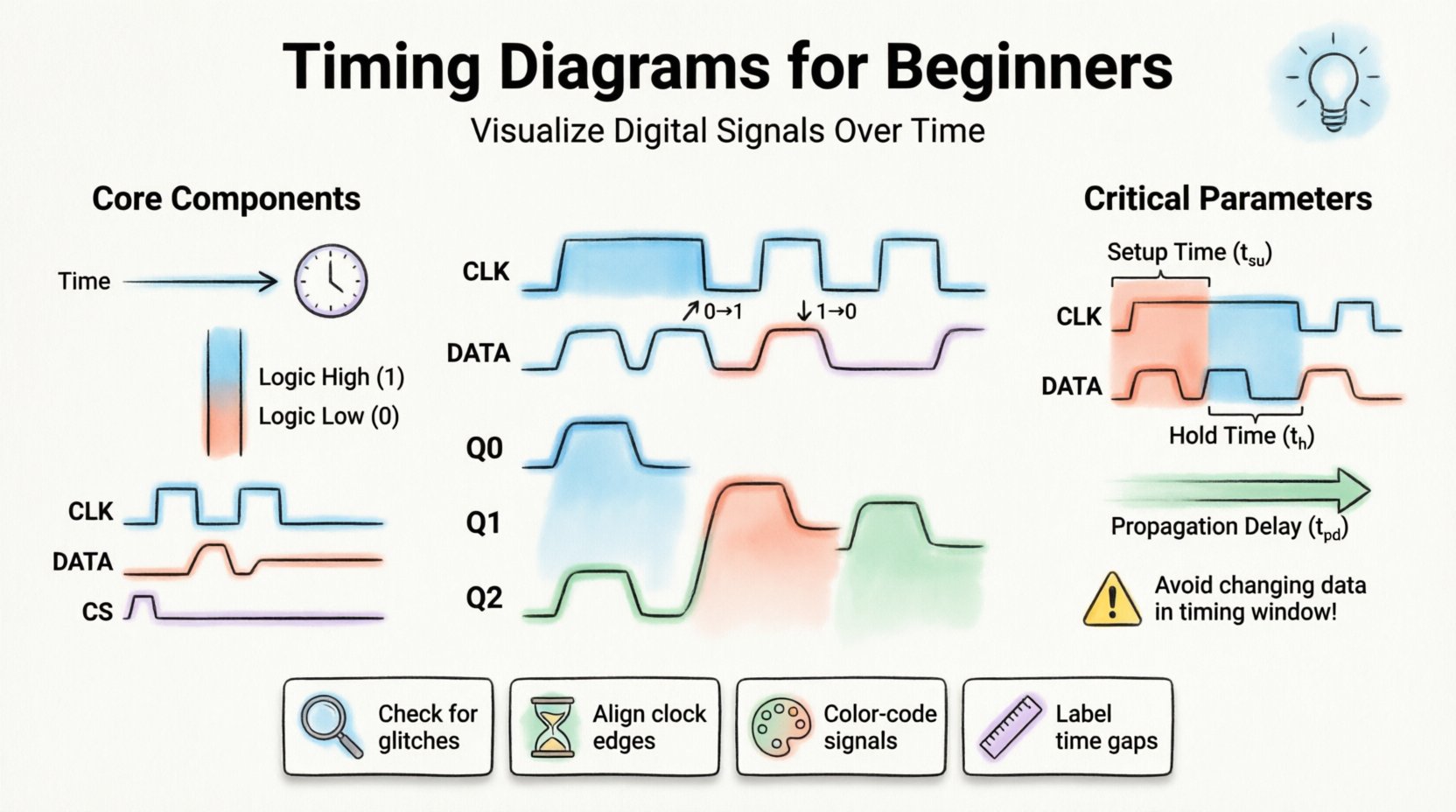

📊 Komponen Utama dari Diagram Waktu

Sebelum menganalisis gelombang yang kompleks, Anda harus memahami komponen dasarnya. Setiap diagram waktu terdiri dari beberapa elemen dasar.

1. Sumbu Waktu

Sumbu horizontal mewakili waktu. Ia mengalir dari kiri ke kanan. Dalam desain digital, sumbu ini sering dibagi menjadi siklus jam, ditandai dengan garis-garis grid vertikal. Skala dapat bervariasi dari nanosekon (ns) untuk prosesor berkecepatan tinggi hingga milisekon (ms) untuk logika kontrol yang lebih lambat.

2. Sumbu Tingkat Tegangan

Sumbu vertikal mewakili keadaan logis dari sinyal. Dalam keluarga logika standar, ini biasanya biner:

- Logika Tinggi (1):Sering direpresentasikan sebagai VCC atau 5V.

- Logika Rendah (0): Sering diwakili sebagai Ground atau 0V.

- High-Z (Impedansi Tinggi): Kondisi di mana pin secara efektif terputus, umum dalam sistem bus.

3. Jalur Sinyal

Setiap garis horizontal mewakili kabel atau nama sinyal tertentu. Garis-garis ini diberi label dengan jelas (misalnya, CLK, DATA_IN, CS) untuk mengidentifikasi bagian mana dari sirkuit yang sedang dipantau.

🔄 Membaca Transisi Sinyal

Gerakan garis sinyal naik dan turun adalah tempat data berada. Memahami arah gerakan ini sangat penting.

⬆️ Tepi Naik

Tepi naik terjadi ketika sinyal berpindah dari Rendah ke Tinggi. Dalam logika biner, ini sering menjadi titik pemicu untuk banyak operasi. Ini mewakili perubahan dari 0 ke 1.

⬇️ Tepi Turun

Tepi turun terjadi ketika sinyal berpindah dari Tinggi ke Rendah. Ini mewakili perubahan dari 1 ke 0.

⚡ Pemicu Tepi

Banyak komponen digital, seperti flip-flop, hanya merespons tepi-tepi ini daripada keadaan stabil. Flip-flop mungkin menangkap data hanya pada tepi naik dari sinyal jam. Jika Anda melewatkan tepi ini, data akan hilang.

| Transisi | Arah | Perubahan Biner | Jenis Pemicu Umum |

|---|---|---|---|

| Tepi Naik | Rendah ➔ Tinggi | 0 ➔ 1 | Dipicu oleh Tepi Positif |

| Tepi Turun | Tinggi ➔ Rendah | 1 ➔ 0 | Dipicu oleh Tepi Negatif |

| Tingkat Tinggi | Tinggi Stabil | Stabil 1 | Sensitif Tingkat |

| Tingkat Rendah | Rendah Tetap | Tetap 0 | Sensitif Tingkat |

⏳ Parameter Waktu Kritis

Diagram waktu bukan hanya gambar; mereka berisi pengukuran. Ruang antara perubahan sinyal adalah tempat ditentukannya keandalan. Tiga parameter khusus mendominasi analisis waktu digital.

1. Penundaan Propagasi (tpd)

Sinyal tidak bergerak secara instan. Ketika input berubah, diperlukan waktu tertentu bagi output untuk mencerminkan perubahan tersebut. Ini disebut penundaan propagasi. Penundaan ini disebabkan oleh resistansi fisik dan kapasitansi bahan-bahan.

- Definisi: Perbedaan waktu antara perubahan input dan perubahan output.

- Dampak: Dalam rangkaian gerbang logika, penundaan menumpuk. Jika penundaan terlalu lama, sinyal mungkin tiba setelah siklus jam berikutnya dimulai, menyebabkan kesalahan.

2. Waktu Siap (tsu)

Waktu siap adalah persyaratan agar sinyal data tetap stabil sebelum tepat sebelum tepi jam tiba. Jika data berubah terlalu dekat dengan tepi jam, sirkuit penerima tidak dapat menangkapnya dengan benar.

- Aturan: Data harus valid selama durasi tertentu sebelum jam berfungsi.

- Visual: Pada diagram, ini adalah jarak antara garis data yang stabil dan tepi jam.

3. Waktu Tahan (th)

Waktu tahan adalah persyaratan agar sinyal data tetap stabil setelah saat tepi jam tiba. Jika data berubah segera setelah tepi jam, sirkuit mungkin tidak menangkap nilai yang benar.

- Aturan:Data harus tetap tidak berubah selama durasi tertentu setelah jam berfungsi.

- Visual:Pada diagram, ini adalah celah antara tepi jam dan transisi data berikutnya.

⚠️ Jendela Waktu

Gabungan waktu setup dan hold menciptakan jendela yang valid untuk menangkap data. Jika diagram waktu Anda menunjukkan data berubah dalam jendela ini, sistem berisiko gagal.

⚡ Sistem Sinkron vs. Asinkron

Diagram waktu berbeda secara signifikan tergantung pada arsitektur sistem.

Sistem Sinkron

Dalam desain sinkron, semua operasi diatur oleh sinyal jam global. Setiap perubahan keadaan terjadi pada tepi jam ini. Diagram waktu untuk sistem ini tampak sangat teratur.

- Karakteristik:Dapat diprediksi, lebih mudah dirancang, terbatas oleh kecepatan jam.

- Tampilan Diagram:Garis-garis grid vertikal sejajar sempurna dengan semua perubahan sinyal.

Sistem Asinkron

Dalam desain asinkron, tidak ada jam global. Sinyal berubah kapan saja input berubah. Ini menawarkan potensi kecepatan lebih tinggi tetapi membuat analisis waktu jauh lebih sulit.

- Karakteristik:Respon lebih cepat terhadap input, analisis bahaya yang kompleks.

- Tampilan Diagram:Transisi sinyal terjadi pada interval yang tidak teratur. Anda harus mengukur jarak waktu tepat antar peristiwa.

📝 Cara Menggambar Diagram Waktu

Membuat diagram waktu adalah proses sistematis. Ikuti langkah-langkah ini untuk mendokumentasikan sirkuit atau memverifikasi desain.

- Identifikasi Sinyal:Daftar semua input, output, dan jalur kontrol internal. Beri label dengan jelas.

- Tentukan Basis Waktu:Tentukan skala waktu. Untuk rangkaian logika, siklus jam biasanya satuan standar.

- Gambarkan Jam:Selalu gambar sinyal jam terlebih dahulu. Ini menjadi acuan untuk semua peristiwa lainnya.

- Peta Input: Gambar gelombang masukan berdasarkan operasi logika atau urutan pengujian.

- Hitung Penundaan: Geser sinyal keluaran ke kanan berdasarkan penundaan propagasi gerbang yang terlibat.

- Periksa Kendala: Periksa bahwa waktu siap dan waktu tahan terpenuhi untuk setiap flip-flop.

- Ulas Transisi: Pastikan tidak ada gangguan. Gangguan adalah pulsa singkat yang tidak diinginkan yang dapat memicu logika secara salah.

🔄 Contoh Dunia Nyata: Sebuah Pencacah Sederhana

Untuk memvisualisasikan bagaimana konsep-konsep ini bekerja bersama, pertimbangkan sebuah pencacah biner 3-bit sederhana. Sirkuit ini menambah nilai setiap kali sinyal jam berdenyut.

Bayangkan tiga jalur keluaran: Q0, Q1, dan Q2. Q0 berubah setiap siklus jam. Q1 berubah setiap kali Q0 menyelesaikan satu siklus penuh. Q2 berubah setiap kali Q1 menyelesaikan satu siklus penuh.

Analisis Langkah demi Langkah

- Jam (CLK): Gelombang persegi dengan siklus kerja 50%.

- Q0 (LSB): Berubah keadaan pada setiap tepi naik jam. Frekuensi setengah dari jam.

- Q1: Berubah keadaan pada setiap tepi naik Q0. Frekuensi setengah dari Q0.

- Q2 (MSB): Berubah keadaan pada setiap tepi naik Q1. Frekuensi setengah dari Q1.

Ketika menggambar ini, Anda akan melihat efek riak. Q0 berubah terlebih dahulu. Q1 menunggu Q0 stabil sebelum berubah. Q2 menunggu Q1. Akumulasi penundaan ini adalah inti dari pencacah riak.

| Siklus Jam | Q2 | Q1 | Q0 | Nilai Desimal |

|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 1 |

| 3 | 0 | 1 | 0 | 2 |

| 4 | 0 | 1 | 1 | 3 |

| 5 | 1 | 0 | 0 | 4 |

⚠️ Kesalahan Umum yang Harus Dihindari

Bahkan insinyur berpengalaman bisa melakukan kesalahan saat membaca diagram waktu. Waspadai kesalahan umum ini.

- Mengabaikan Glitch:Pulsa singkat mungkin tidak terlihat jika skala waktu terlalu besar, tetapi bisa memicu latch. Selalu periksa adanya pulsa sempit.

- Menafsirkan Salah Duty Cycle:Menganggap clock 50% padahal sebenarnya miring. Ini memengaruhi jendela waktu.

- Mengabaikan Status High-Z:Pada sistem bus, jalur mengambang. Diagram waktu harus menunjukkan kapan jalur diaktifkan dan kapan mengambang.

- Bingung antara Setup dan Hold:Setup terjadi sebelum tepi; Hold terjadi setelahnya. Bingung antara keduanya menyebabkan desain sirkuit yang salah.

- Mengabaikan Referensi Tanah: Semua tingkat tegangan harus diukur relatif terhadap tanah yang sama. Jika tanah berbeda, tingkat logika menjadi tidak valid.

🛠 Praktik Terbaik untuk Dokumentasi

Ketika membuat diagram waktu untuk dokumentasi atau debugging, ikuti panduan ini untuk memastikan kejelasan.

- Gunakan Penskalaan yang Konsisten: Pastikan sumbu waktu bersifat linier. Jangan memampatkan satu bagian dan memperpanjang bagian lain kecuali secara eksplisit diberi tanda.

- Sesuaikan Sudut Kritis: Pastikan tepi clock tepat berimpit dengan titik pengambilan sampel data.

- Beri Label pada Ruang Kosong: Jika terdapat keterlambatan, beri label dengan nilai waktu tertentu (misalnya, tpd = 5ns).

- Kode Warna: Gunakan warna yang berbeda untuk jenis sinyal yang berbeda (misalnya, biru untuk clock, merah untuk data, hijau untuk kontrol).

- Tandai Status Aktif: Jelas menunjukkan apakah suatu sinyal aktif tinggi atau aktif rendah (misalnya, menggunakan garis di atas nama seperti /CS).

🧩 Metastabilitas dan Bahaya Waktu

Diagram waktu lanjutan sering mengungkap fenomena yang disebut metastabilitas. Ini terjadi ketika suatu sinyal berubah tepat pada jendela setup/hold flip-flop. Keluaran tidak segera menetap ke 0 atau 1; ia mengambang pada tingkat tegangan antara.

Meskipun langka, metastabilitas dapat menyebabkan kegagalan sistem. Diagram waktu membantu memprediksi hal ini dengan menunjukkan hubungan antara input asinkron dan clock sinkron. Jika sinyal eksternal berubah terlalu dekat dengan tepi clock, diagram akan menunjukkan data melintasi ambang pada waktu yang salah.

🔍 Menganalisis Data Nyata

Ketika Anda melihat diagram waktu yang dihasilkan oleh analis logika, garis-garisnya jarang berbentuk persegi sempurna. Sinyal dunia nyata memiliki:

- Waktu Naik: Waktu yang dibutuhkan untuk berpindah dari Rendah ke Tinggi. Jarang terjadi secara instan.

- Waktu Turun: Waktu yang dibutuhkan untuk berpindah dari Tinggi ke Rendah.

- Kelebihan/Kelemahan Puncak: Loncatan tegangan yang melebihi batas catu daya.

- Jitter: Variasi dalam waktu tepi sinyal.

Memahami ketidaksempurnaan ini sangat penting untuk desain berkecepatan tinggi. Gelombang persegi sempurna adalah ideal teoretis; sinyal nyata adalah gelombang analog yang mewakili logika digital.

📚 Ringkasan Poin-Poin Utama

Diagram timing adalah bahasa dari timing digital. Mereka menerjemahkan logika abstrak menjadi realitas fisik. Dengan menguasainya, Anda mendapatkan kemampuan untuk:

- Membayangkan aliran data melalui suatu sistem.

- Mengidentifikasi di mana sinyal mungkin bertentangan.

- Memastikan bahwa data ditangkap secara andal.

- Menghitung kecepatan operasi maksimum suatu rangkaian.

Mulailah dengan berlatih menggunakan gerbang logika sederhana. Gambar input, hitung delay, dan plot output. Seiring perkembangan, pindahlah ke bus yang kompleks dan domain clock. Dengan kesabaran dan latihan, membaca diagram ini akan menjadi hal yang alami.

🚀 Melangkah Maju

Teruslah mengeksplorasi nuansa integritas sinyal dan jaringan distribusi clock. Seiring sistem menjadi lebih cepat, margin timing menjadi lebih kecil. Kemampuan membaca diagram timing secara akurat akan tetap menjadi kompetensi utama bagi setiap insinyur yang bekerja dengan perangkat keras digital.