Dalam elektronika digital dan teknik komputer, memahami hubungan temporal antar sinyal merupakan dasar untuk keandalan sistem. Diagram waktu berfungsi sebagai bahasa visual utama untuk menggambarkan hubungan-hubungan tersebut. Diagram ini memetakan status sinyal terhadap sumbu waktu, memungkinkan insinyur untuk memvisualisasikan aliran data, sinkronisasi jam, dan kemungkinan bahaya dalam suatu rangkaian. Panduan ini mengeksplorasi elemen-elemen struktural, pola operasional, dan adegan kritis yang ditemukan dalam analisis gelombang sinyal.

Baik sedang merancang sirkuit terpadu maupun mendiagnosis sistem tertanam, kemampuan untuk menafsirkan dan membuat representasi waktu yang akurat merupakan kompetensi inti. Dokumen ini memberikan gambaran teknis tentang bagaimana sinyal berinteraksi, batasan-batasan yang harus dipenuhi, serta jebakan umum yang ditemui selama verifikasi.

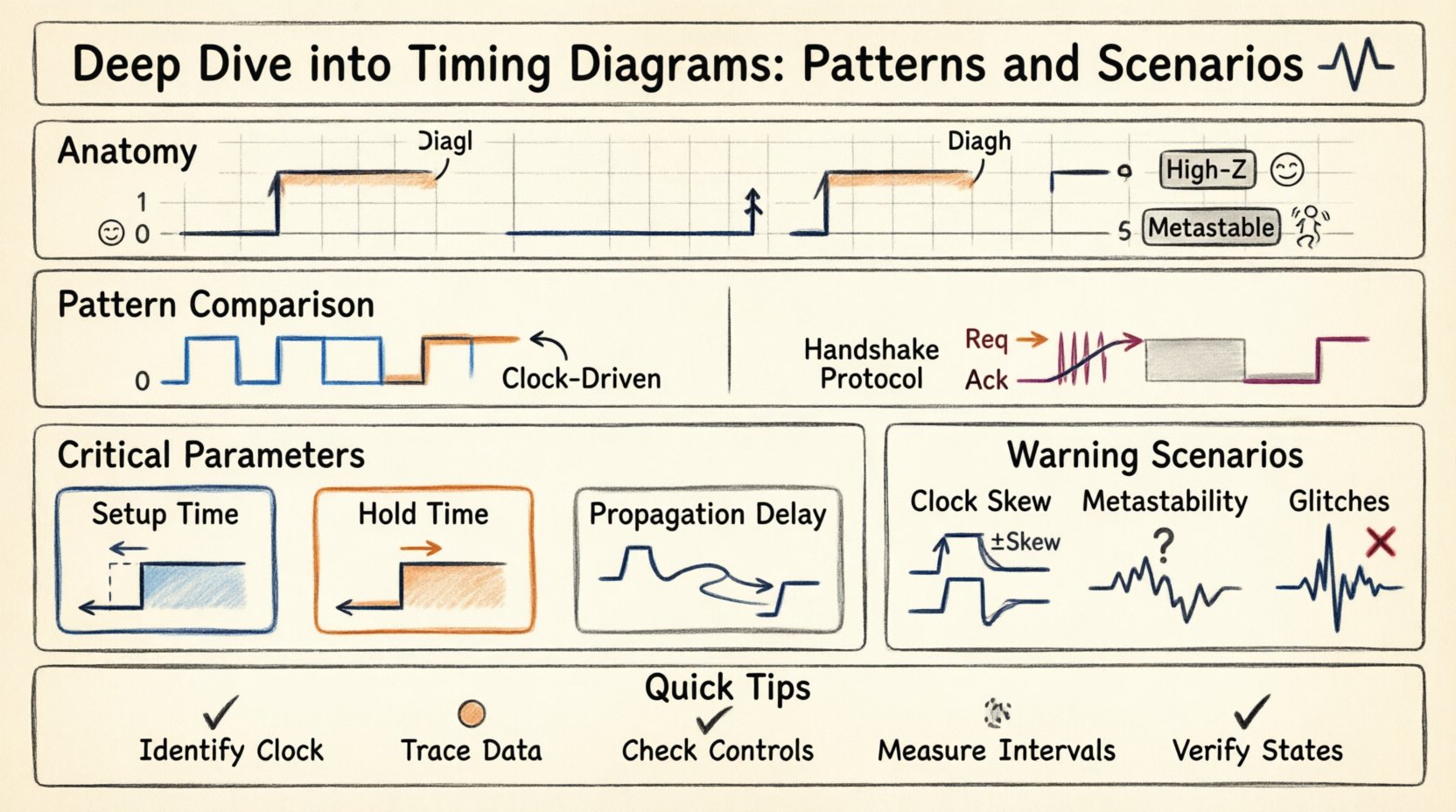

📐 Anatomi Diagram Waktu

Diagram waktu adalah representasi grafis di mana sumbu horizontal mewakili waktu, dan sumbu vertikal mewakili tingkat sinyal. Setiap garis horizontal sesuai dengan sinyal atau jaringan tertentu dalam desain. Memahami komponen-komponen ini merupakan langkah pertama menuju analisis yang akurat.

- Sumbu Waktu: Biasanya berjalan secara horizontal dari kiri ke kanan. Dapat berupa linier atau logaritmik, tergantung pada skala peristiwa yang diamati.

- Garis Sinyal: Jejak-jejak individu yang mewakili tingkat tegangan. Tegangan tinggi biasanya menunjukkan logika 1, sedangkan tegangan rendah menunjukkan logika 0.

- Transisi: Garis vertikal yang menunjukkan perubahan keadaan, seperti tepi naik (0 ke 1) atau tepi turun (1 ke 0).

- Label: Anotasi teks yang mengidentifikasi sinyal tertentu, pin, atau jalur kontrol.

- Penanda: Garis putus-putus vertikal yang sering digunakan untuk menandai peristiwa tertentu, seperti pulsa jam atau pemicu reset.

🔢 Tingkat dan Keadaan Logika

Sinyal digital tidak selalu ada secara ketat pada 0 atau 1. Dalam skenario praktis, sinyal dapat berada dalam keadaan tak terdefinisi atau keadaan impedansi tinggi. Diagram yang lengkap harus mempertimbangkan variasi-variasi ini.

- Logika Tinggi (1): Sinyal dipaksa ke tingkat tegangan yang diakui sebagai benar secara logika.

- Logika Rendah (0): Sinyal dipaksa ke tingkat tegangan yang diakui sebagai salah secara logika.

- High-Z: Sinyal terputus dari penggerak, secara efektif mengambang. Hal ini umum terjadi pada buffer tiga keadaan.

- Metastabil: Suatu keadaan di mana sinyal tidak tinggi maupun rendah, sering terjadi selama transisi asinkron.

⚙️ Pola Waktu Umum

Desain mengikuti pola-pola yang dapat diprediksi untuk menjamin integritas data. Pola-pola ini mendefinisikan bagaimana data bergerak relatif terhadap sinyal kontrol. Mengenali pola-pola ini membantu dalam memverifikasi bahwa desain memenuhi spesifikasinya.

📌 Transfer Data Sinkron

Desain sinkron bergantung pada sinyal jam global untuk mengoordinasikan tindakan. Data hanya diambil pada momen-momen tertentu, biasanya tepi naik atau tepi turun dari jam.

- Digerakkan Jam: Semua perubahan status terjadi sehubungan dengan tepi jam.

- Kesesuaian Data:Data harus stabil sebelum tepi jam dan tetap stabil setelahnya.

- Propagasi:Ada keterlambatan antara tepi jam dan saat keluaran berubah.

📌 Penyambungan Asinkron

Komunikasi asinkron tidak bergantung pada jam bersama. Sebaliknya, ia menggunakan sinyal kontrol untuk menunjukkan kapan data siap dan kapan telah diterima.

- Permintaan (Req):Pengirim memberi sinyal bahwa data tersedia.

- Konfirmasi (Ack):Penerima memberi sinyal bahwa data telah diterima.

- Status Tunggu:Pengirim dapat berhenti sejenak hingga penerima siap.

| Fitur | Pola Sinkron | Pola Asinkron |

|---|---|---|

| Koordinasi | Sinyal Jam Global | Sinyal Tanda Tangan Kontrol |

| Kecepatan | Umumnya Lebih Tinggi | Bervariasi, tergantung pada respons |

| Kompleksitas | Jaringan Distribusi Jam | Logika Protokol |

| Latensi | Dapat Diprediksi | Bervariasi |

⏱️ Parameter Waktu Kritis

Di luar garis visual, batasan numerik tertentu menentukan apakah sirkuit akan berfungsi dengan benar. Parameter-parameter ini krusial untuk analisis waktu statis dan harus diverifikasi terhadap batas fisik.

🛑 Waktu Siap

Waktu siap adalah jumlah waktu minimum yang harus dijaga agar sinyal data tetap stabil sebelum tepi clock. Jika data berubah terlalu dekat dengan tepi clock, flip-flop penerima mungkin tidak menangkap nilai yang benar.

- Pengukuran:Diukur dari tepi clock aktif ke belakang dalam waktu.

- Risiko:Pelanggaran menyebabkan penangkapan data yang salah.

- Persyaratan:Keterlambatan jalur data harus cukup panjang untuk memenuhi jendela waktu siap.

🛑 Waktu Tahan

Waktu tahan adalah jumlah waktu minimum yang harus dijaga agar sinyal data tetap stabil setelah tepi clock. Ini memastikan bahwa latch memiliki cukup waktu untuk mengunci nilai input.

- Pengukuran:Diukur dari tepi clock aktif ke depan dalam waktu.

- Risiko:Pelanggaran menyebabkan metastabilitas atau penangkapan data yang salah.

- Persyaratan:Keterlambatan jalur data harus cukup pendek untuk memungkinkan jendela waktu tahan.

⚡ Keterlambatan Propagasi

Ini adalah waktu yang dibutuhkan sinyal untuk menempuh perjalanan dari input gerbang logika ke outputnya. Nilainya bervariasi tergantung pada kapasitansi beban dan resistansi internal transistor.

- tpd (Tinggi ke Rendah):Waktu untuk transisi dari 1 ke 0.

- tpd (Rendah ke Tinggi):Waktu untuk transisi dari 0 ke 1.

- Skew:Perbedaan keterlambatan antara jalur paralel.

🚨 Adegan Waktu Kritis

Beberapa skenario menunjukkan tantangan besar yang memerlukan analisis cermat. Situasi ini sering melibatkan interaksi antara domain clock yang berbeda atau keterbatasan fisik perangkat keras.

🔄 Penyimpangan Jam

Penyimpangan jam terjadi ketika sinyal jam tiba di komponen yang berbeda pada waktu yang berbeda. Hal ini dapat terjadi karena perbedaan rute atau jarak fisik.

- Penyimpangan Positif: Sinyal jam tujuan tiba lebih lambat daripada sinyal jam sumber.

- Penyimpangan Negatif: Sinyal jam tujuan tiba lebih awal daripada sinyal jam sumber.

- Dampak: Dapat secara efektif mengurangi margin waktu pengaturan atau meningkatkan pelanggaran waktu penahanan.

🌊 Metastabilitas

Metastabilitas adalah keadaan di mana output flip-flop bukanlah tinggi maupun rendah. Hal ini biasanya terjadi ketika waktu pengaturan atau waktu penahanan dilanggar, terutama pada persilangan asinkron.

- Penyelesaian: Sirkuit akhirnya beresolusi ke keadaan stabil, tetapi waktu yang dibutuhkan tidak dapat diprediksi.

- Perbaikan: Gunakan sinkronisasi (flip-flop multi-tahap) untuk mengurangi kemungkinan kegagalan.

- MTBF: Rata-rata waktu antar kegagalan dihitung berdasarkan tingkat penyelesaian metastabilitas.

📉 Glitch

Glitch adalah loncatan singkat dalam sinyal yang dapat disalahartikan sebagai transisi yang sah. Mereka sering terjadi karena perbedaan waktu propagasi di sepanjang jalur yang berbeda.

- Penyebab: Panjang jalur yang tidak sama atau kondisi persaingan.

- Dampak: Dapat memicu perubahan keadaan yang tidak diinginkan pada logika hilir.

- Penanggulangan: Gunakan logika penyaringan atau pastikan penutupan waktu yang tepat.

🔍 Menganalisis Gelombang

Ketika meninjau diagram waktu, pendekatan sistematis memastikan tidak ada detail yang terlewat. Insinyur harus melacak aliran data dan sinyal kontrol untuk mengidentifikasi ketidaksesuaian.

🔍 Analisis Langkah demi Langkah

- Identifikasi Jam: Temukan sinyal jam utama. Tentukan apakah sinyal tersebut dipicu pada tepi naik atau tepi turun.

- Lacak Jalur Data: Ikuti jalur data dari sumber ke tujuan.

- Periksa Sinyal Kendali:Verifikasi bahwa enable, reset, dan clear dinyatakan dengan benar.

- Ukur Interval:Hitung waktu antara kejadian tertentu untuk memverifikasi persyaratan setup dan hold.

- Verifikasi Transisi Status:Pastikan status output sesuai dengan fungsi logika yang diharapkan.

🔍 Membaca Pemicu Edge

Memahami bagaimana komponen bereaksi terhadap tepi sinyal sangat penting.

- Dipicu oleh Tepi Positif:Tindakan terjadi pada transisi dari rendah ke tinggi.

- Dipicu oleh Tepi Negatif:Tindakan terjadi pada transisi dari tinggi ke rendah.

- Dipicu oleh Level:Tindakan terjadi selama sinyal tetap pada level tertentu.

🛠️ Standar Dokumentasi

Dokumentasi yang jelas memastikan desain dipahami oleh insinyur lain. Konsistensi dalam notasi dan penandaan mencegah salah tafsir saat debugging atau serah terima.

📝 Konvensi Penandaan

- Nama Sinyal:Gunakan konvensi penamaan yang konsisten (misalnya,

clk,rst_n,data_in). - Polaritas:Tunjukkan sinyal aktif rendah dengan jelas, sering menggunakan garis atas atau akhiran.

- Satuan:Jelaskan secara jelas satuan waktu (ns, µs, ms) pada sumbu waktu.

- Skala:Pastikan skala waktu sesuai dengan peristiwa yang ditampilkan.

📝 Kejelasan Visual

- Jarak:Hindari garis yang tumpang tindih jika memungkinkan.

- Kontras:Gunakan warna atau ketebalan garis yang berbeda untuk jenis sinyal yang berbeda.

- Anotasi:Tambahkan catatan yang menjelaskan perilaku kompleks atau batasan tertentu.

- Kisi:Gunakan latar belakang kisi untuk membantu mengukur interval waktu.

🚧 Alur Kerja Pemecahan Masalah

Ketika desain gagal memenuhi persyaratan waktu, proses pemecahan masalah yang terstruktur membantu mengidentifikasi akar penyebabnya. Ini melibatkan pemeriksaan diagram terhadap batasan fisik.

🚧 Mengidentifikasi Pelanggaran

- Periksa Waktu Siap:Apakah data tiba terlambat dibandingkan dengan jam?

- Periksa Waktu Tahan:Apakah data berubah terlalu cepat setelah jam?

- Periksa Frekuensi Jam:Apakah periode jam lebih pendek dari minimum yang dibutuhkan?

🚧 Strategi Pengurangan Dampak

- Register Pipa:Masukkan register tambahan untuk memutus jalur kombinasional yang panjang.

- Penghentian Jam:Kurangi aktivitas untuk menurunkan daya dan mungkin meningkatkan waktu.

- Penambahan Buffer:Tambahkan buffer untuk menyeimbangkan penundaan di sepanjang jalur paralel.

- Kendala Waktu:Tentukan jalur palsu untuk mengecualikan logika yang tidak memengaruhi aliran data.

📈 Praktik Terbaik untuk Desain

Menerapkan praktik terbaik selama tahap desain mengurangi kemungkinan masalah waktu di kemudian hari dalam siklus pengembangan. Perencanaan proaktif lebih efisien daripada perbaikan reaktif.

- Standarkan Antarmuka:Gunakan protokol yang dikenal untuk transfer data agar verifikasi waktu menjadi lebih sederhana.

- Minimalkan Jalur Asinkron:Pertahankan interaksi asinkron seminimal mungkin untuk mengurangi risiko metastabilitas.

- Dokumentasikan Asumsi:Jelaskan secara jelas frekuensi clock dan tingkat tegangan dalam spesifikasi desain.

- Ulas Secara Berkala:Lakukan ulasan waktu pada setiap tonggak utama proyek.

🎯 Ringkasan Konsep Kunci

Diagram waktu adalah alat penting untuk memvisualisasikan perilaku temporal sistem digital. Mereka mengungkap bagaimana sinyal data dan kontrol berinteraksi seiring waktu, menyoroti batasan kritis seperti waktu siap dan waktu tahan. Dengan memahami anatomi diagram ini, insinyur dapat mengidentifikasi pola, memprediksi kesalahan, dan memastikan kinerja sistem yang kuat.

Poin-poin utama mencakup perbedaan antara pola sinkron dan asinkron, pentingnya manajemen skew clock, serta kebutuhan akan standar dokumentasi yang jelas. Mematuhi prinsip-prinsip ini memudahkan desain yang handal dan menyederhanakan proses verifikasi.

Analisis berkelanjutan terhadap data gelombang memastikan desain tetap berada dalam batas operasional. Seiring kemajuan teknologi dan meningkatnya kecepatan clock, presisi yang dibutuhkan dalam analisis waktu menjadi semakin krusial. Menguasai konsep-konsep ini memungkinkan penciptaan arsitektur digital yang stabil dan berkinerja tinggi.