Sistem digital bergantung pada sinkronisasi yang tepat agar berfungsi dengan benar. Tanpa waktu yang akurat, korupsi data, kegagalan sistem, dan kegagalan keselamatan menjadi tak terhindarkan. Diagram waktu menyediakan representasi visual tentang bagaimana sinyal berubah seiring waktu, memberikan gambaran jelas mengenai hubungan antara siklus jam, validitas data, dan sinyal kontrol. Panduan ini mengeksplorasi peran penting diagram waktu di berbagai sektor, menjelaskan contoh praktis dan solusi teknis untuk tantangan umum.

🔍 Memahami Dasar-Dasar

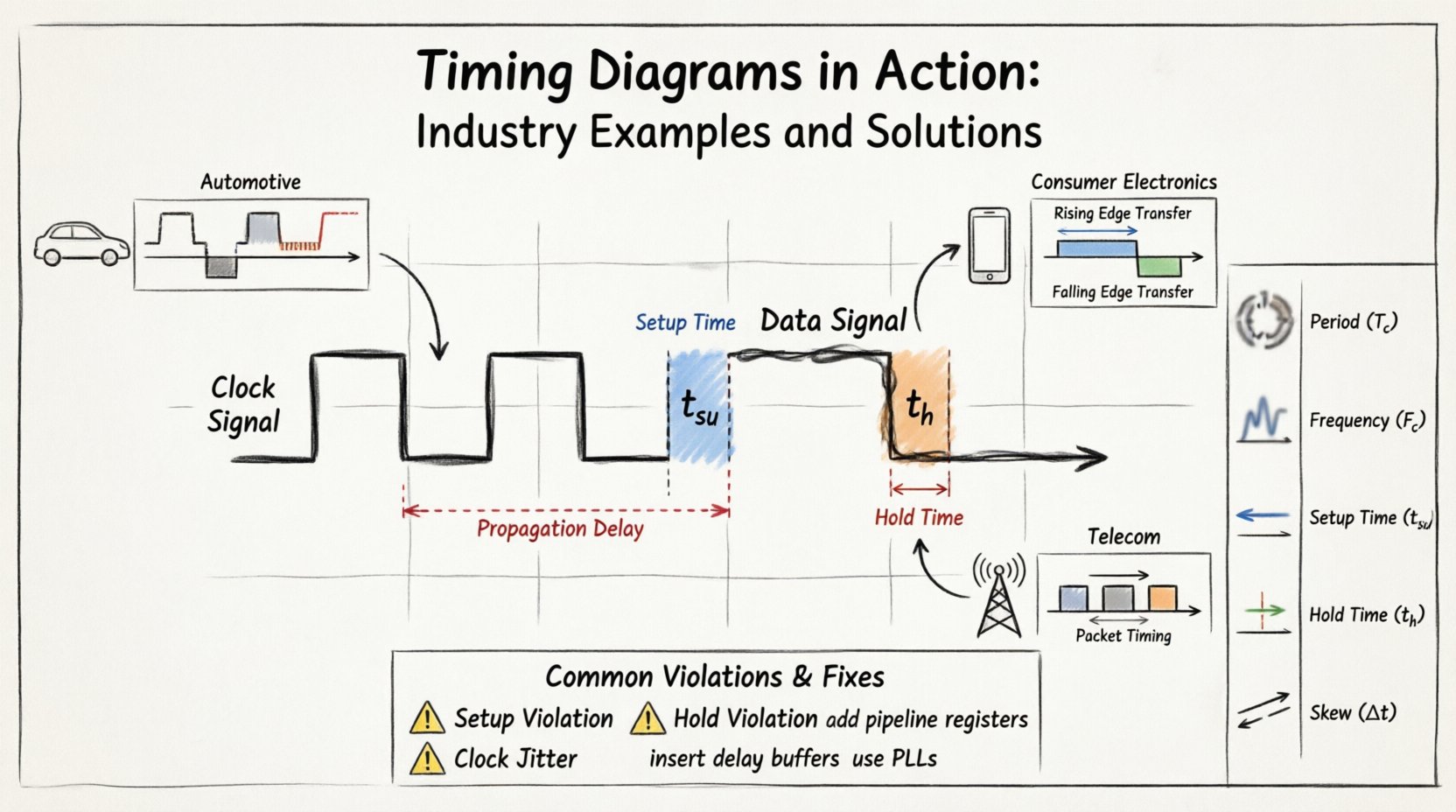

Sebelum masuk ke aplikasi tertentu, sangat penting untuk memahami komponen utama dari diagram waktu. Diagram ini memetakan perilaku sinyal relatif terhadap jam referensi. Mereka bukan sekadar gambar; mereka adalah batasan matematis yang menentukan perilaku perangkat keras.

- Sudut Sinyal:Transisi dari rendah ke tinggi (sudut naik) atau tinggi ke rendah (sudut turun) memicu perubahan keadaan dalam logika urutan.

- Periode Jam:Durasi antara dua sudut berurutan dengan polaritas yang sama menentukan waktu yang tersedia agar logika dapat stabil.

- Keterlambatan Propagasi:Waktu yang dibutuhkan sinyal untuk menempuh perjalanan dari pin input ke pin output melalui gerbang logika.

- Waktu Siap dan Waktu Tahan:Batasan kritis yang memastikan data tetap stabil sebelum dan sesudah sudut jam.

Ketika parameter-parameter ini dilanggar, rangkaian dapat memasuki keadaan metastabil, yang menyebabkan perilaku yang tidak dapat diprediksi. Insinyur menggunakan diagram waktu untuk memverifikasi bahwa implementasi fisik suatu desain sesuai dengan persyaratan logis ini.

🚗 Elektronik Otomotif: Waktu yang Kritis bagi Keselamatan

Industri otomotif menuntut tingkat keandalan tertinggi. Kendaraan berisi puluhan Unit Kendali Elektronik (ECU) yang berkomunikasi melalui bus seperti CAN (Jaringan Area Kendali), LIN (Jaringan Interkoneksi Lokal), dan FlexRay. Analisis waktu di sini bukan hanya tentang kecepatan; tetapi tentang determinisme dan keselamatan.

1. Arbitrasi Bus CAN

Bus CAN memungkinkan beberapa node berkomunikasi melalui satu kabel. Diagram waktu untuk arbitrasi CAN mengungkapkan bagaimana prioritas ditentukan saat terjadi persaingan bus.

- Dominan vs. Reksesif:Tingkat logika direpresentasikan oleh keadaan tegangan. Bit dominan (0) mengesampingkan bit reksesif (1).

- Sinkronisasi:Node menyinkronkan dengan bit awal frame menggunakan segmen sinkronisasi.

- Titik Pengambilan Sampel:Data diambil pada persentase tertentu dari waktu bit untuk menghindari gangguan.

Jika titik pengambilan sampel terlalu dekat dengan tepi, gangguan dapat menyebabkan kesalahan bit. Jika terlalu terlambat, data mungkin tidak stabil. Diagram waktu membantu insinyur menetapkan titik pengambilan sampel dengan benar, biasanya sekitar 80% dari waktu bit.

2. Pengambilan Sampel ADC dalam Fusi Sensor

Kendaraan modern menggunakan beberapa sensor (radar, lidar, kamera) untuk menciptakan persepsi terhadap lingkungan. Konverter Analog ke Digital (ADC) harus mengambil sampel sinyal pada interval yang tepat untuk menghindari aliasing.

- Getaran Jam:Perubahan dalam waktu sudut jam menyebabkan gangguan masuk ke dalam sinyal digital.

- Latensi:Waktu dari input sensor hingga output data yang telah diproses harus diminimalkan untuk kontrol waktu nyata.

- Interleaving:Banyak ADC sering bekerja secara paralel. Diagram waktu memastikan fase-fasenya sejalan untuk mencegah celah dalam data.

📱 Elektronik Konsumen: Antarmuka Kecepatan Tinggi

Perangkat konsumen mengutamakan kinerja dan efisiensi daya. Antarmuka seperti memori DDR dan tautan tampilan membutuhkan jendela waktu yang ketat untuk mencapai bandwidth tinggi tanpa meningkatkan konsumsi daya.

1. Antarmuka Memori DDR

Memori Double Data Rate (DDR) mentransfer data pada tepi naik dan turun dari clock. Ini menggandakan laju data efektif tetapi mengurangi waktu jendela stabilitas data menjadi separuhnya.

| Parameter | Definisi | Dampak Pelanggaran |

|---|---|---|

| Waktu Siap | Waktu data harus stabil sebelum tepi clock | Transfer data terlewat, sistem macet |

| Waktu Tahan | Waktu data harus tetap stabil setelah tepi clock | Data rusak, bit terbalik |

| Skew Clock | Perbedaan waktu kedatangan clock ke chip yang berbeda | Margin waktu berkurang, ketidakstabilan |

| Duty Cycle | Rasio waktu tinggi terhadap periode total | Kinerja tidak seimbang, jitter meningkat |

Pada DDR4 dan DDR5, bus perintah dan alamat sering berjalan pada frekuensi yang lebih rendah dibandingkan bus data. Diagram waktu harus mempertimbangkan sinyal strobe sinkron sumber (DQS) yang menyertai data untuk menunjukkan jendela yang valid.

2. Antarmuka Tampilan (MIPI DSI)

Perangkat mobile menggunakan Antarmuka Serial Tampilan MIPI (DSI) untuk menghubungkan prosesor ke layar. Antarmuka ini menggunakan jalur diferensial kecepatan tinggi.

- Mode Perintah LP:Mode hemat daya untuk mengirim perintah, mengandalkan waktu yang ketat untuk urutan bangun.

- Mode Data HS:Transmisi kecepatan tinggi di mana pemulihan clock dilakukan pada aliran data.

- Waktu Putar Balik:Waktu yang dibutuhkan untuk beralih dari mode transmisi ke mode penerimaan pada jalur yang sama.

Ketidaksesuaian dalam diagram waktu ini menghasilkan artefak layar, berkedip, atau kehilangan total output video.

📡 Telekomunikasi: Latensi dan Bandwidth

Dalam telekomunikasi, waktu berkaitan erat dengan latensi. Waktu pengiriman paket dan sinkronisasi di seluruh jaringan terdistribusi sangat penting untuk layanan seperti 5G dan perdagangan frekuensi tinggi.

1. Sinyal PCIe

Standar Peripheral Component Interconnect Express (PCIe) banyak digunakan untuk menghubungkan komponen berkecepatan tinggi. Standar ini menggunakan jalur serial dengan jam tertanam atau jam sinkron sumber.

- Equalisasi:Integritas sinyal menurun seiring jarak. Diagram waktu menunjukkan bagaimana filter equalisasi mengkompensasi kehilangan sinyal.

- Pelatihan Tautan:Urutan status yang diatur waktu untuk menetapkan kecepatan tautan dan lebar jalur.

- Kontrol Aliran:Jendela waktu untuk kontrol aliran berbasis kredit mencegah buffer overflow.

2. PHY Ethernet

Ethernet standar bergantung pada jam bersama atau pemulihan jam. Ethernet Gigabit dan seterusnya menggunakan pengkodean 8b/10b untuk memastikan transisi yang cukup untuk pemulihan jam.

- Periode Idle:Jendela waktu yang ditentukan di mana tidak ada data yang dikirim untuk menjaga sinkronisasi.

- Pembatas Awal Bingkai:Pola bit tertentu yang menandai awal paket, memerlukan waktu deteksi yang tepat.

- Jeda Antar-Paket:Penundaan wajib antar paket untuk memungkinkan perangkat keras melakukan reset.

⚠️ Pelanggaran Waktu Umum dan Solusinya

Bahkan dengan desain yang hati-hati, pelanggaran waktu tetap terjadi. Mengidentifikasi akar penyebabnya memerlukan analisis diagram waktu untuk melihat di mana sinyal menyimpang dari ekspektasi.

1. Pelanggaran Waktu Setup

Terjadi ketika data tiba terlambat untuk ditangkap oleh tepi jam.

- Penyebab:Kedalaman logika berlebihan, keterlambatan kabel panjang, atau skew jam.

- Solusi:

- Sisipkan register pipeline untuk memutus jalur panjang.

- Optimalkan sintesis logika untuk mengurangi jumlah gerbang.

- Sesuaikan frekuensi jam untuk memberikan lebih banyak waktu.

2. Pelanggaran Waktu Hold

Terjadi ketika data berubah terlalu cepat setelah tepi clock, menggantikan nilai yang ditangkap.

- Penyebab:Keterlambatan jalur pendek, skew clock di mana clock penangkap tiba terlambat.

- Solusi:

- Sisipkan buffer penundaan di jalur data.

- Gunakan teknik retiming untuk menyeimbangkan jalur.

- Pastikan jaringan distribusi clock memiliki skew minimal.

3. Skew dan Jitter Clock

Skew adalah perbedaan waktu kedatangan sinyal clock di register yang berbeda. Jitter adalah variasi jangka pendek dari tepi clock.

- Dampak:Mengurangi margin waktu efektif yang tersedia untuk data.

- Solusi:

- Gunakan pembangkit clock dengan jitter rendah.

- Desain pohon clock seimbang dengan jalur berpanjang sama.

- Implementasikan Phase-Locked Loops (PLLs) untuk membersihkan sinyal clock.

✅ Praktik Terbaik untuk Implementasi

Mencapai timing yang kuat membutuhkan pendekatan sistematis sepanjang siklus hidup desain. Dokumentasi dan verifikasi sebanding pentingnya dengan sirkuit itu sendiri.

1. Tentukan Batasan Timing Sejak Awal

Jangan menunggu hingga fase implementasi untuk menentukan persyaratan timing. Dokumentasikan frekuensi clock, keterlambatan input, dan keterlambatan output dalam spesifikasi desain. Ini memastikan semua pemangku kepentingan memahami batas-batas sistem.

2. Gunakan Analisis Timing Statis

Alat Analisis Timing Statis (STA) menghitung jalur keterlambatan terburuk tanpa mensimulasikan setiap kombinasi input. Metode ini efisien dan mencakup semua keadaan yang mungkin, memastikan tidak ada pelanggaran timing yang terlewat.

3. Validasi dengan Simulasi

Meskipun STA sangat kuat, simulasi dinamis memberikan gambaran perilaku sinyal dalam kondisi tertentu. Gunakan simulasi untuk memverifikasi jalur kritis, terutama yang melibatkan logika asinkron atau mesin keadaan yang kompleks.

4. Pertimbangan Desain Fisik

Tata letak fisik chip atau papan secara langsung memengaruhi timing.

- Panjang Kabel:Kabel yang lebih panjang menimbulkan kapasitansi dan resistansi yang lebih besar, meningkatkan keterlambatan.

- Interferensi Silang:Sinyal yang berdekatan dapat menimbulkan gangguan, menyebabkan transisi palsu.

- Gangguan Sumber Daya: Penurunan tegangan dapat memperlambat kecepatan switching gerbang.

🛠️ Mendiagnosis Skenario Dunia Nyata

Ketika suatu sistem gagal memenuhi batas waktu, proses debugging yang terstruktur diperlukan. Langkah-langkah berikut menjelaskan pendekatan logis untuk menyelesaikan masalah waktu.

- Langkah 1: Identifikasi Jalur.Temukan jalur register ke register tertentu yang menyebabkan kegagalan. Periksa laporan waktu untuk slack paling negatif.

- Langkah 2: Analisis Gelombang Sinyal.Gunakan penampil diagram waktu untuk memeriksa transisi sinyal yang sebenarnya. Bandingkan dengan nilai yang diharapkan.

- Langkah 3: Periksa Sinyal Jam.Verifikasi kualitas sinyal jam. Periksa adanya jitter, distorsi duty cycle, atau glitch.

- Langkah 4: Tinjau Keterbatasan.Pastikan keterbatasan dalam file desain sesuai dengan kenyataan fisik perangkat keras.

- Langkah 5: Ulangi.Lakukan perubahan pada logika atau tata letak, lalu jalankan kembali analisis waktu.

📊 Ringkasan Parameter Waktu

Untuk memudahkan referensi cepat, berikut ini adalah ringkasan parameter waktu kunci yang digunakan di berbagai industri.

| Parameter | Simbol | Satuan Khas | Deskripsi |

|---|---|---|---|

| Periode | Tc | ns | Waktu antara tepi jam yang berurutan |

| Frekuensi | Fc | Hz | Kebalikan dari periode |

| Waktu Siap | tsu | ns | Stabilitas data yang diperlukan sebelum tepi clock |

| Waktu Tahan | th | ns | Stabilitas data yang diperlukan setelah tepi clock |

| Keterlambatan Propagasi | tpd | ns | Waktu yang dibutuhkan sinyal untuk melewati logika |

| Skew | Δt | ps | Perbedaan waktu kedatangan clock |

🔄 Mengelola Desain Asinkron

Tidak semua sistem berjalan pada satu clock. Desain asinkron melibatkan data yang melintasi antara domain clock yang berbeda. Ini menimbulkan risiko metastabilitas, di mana flip-flop memasuki keadaan yang tidak terdefinisi.

- Rantai Sinkronisasi: Gunakan sinkronisasi multi-tahap (biasanya dua flip-flop) untuk memungkinkan sinyal stabil sebelum digunakan.

- Protokol Handshake: Implementasikan mekanisme permintaan-akun untuk memastikan penerima siap sebelum data dikirim.

- Buffer FIFO: Gunakan struktur memori First-In-First-Out untuk memisahkan kecepatan produsen dan konsumen.

Diagram waktu untuk desain asinkron menunjukkan hubungan antara dua clock yang independen. Kuncinya adalah memastikan jalur data memiliki cukup waktu untuk stabil sebelum clock penerima mengambil sampel.

🌟 Pikiran Akhir

Diagram waktu adalah tulang punggung verifikasi sistem digital. Mereka menghubungkan kesenjangan antara logika abstrak dan kenyataan fisik. Dengan memahami nuansa waktu setup, waktu tahan, skew clock, dan jitter, insinyur dapat merancang sistem yang tangguh, efisien, dan handal.

Baik dalam sistem keselamatan otomotif, perangkat konsumen, atau infrastruktur telekomunikasi, prinsip-prinsipnya tetap sama. Ketepatan dalam waktu mengarah pada ketepatan dalam kinerja. Pemantauan terus-menerus dan kepatuhan terhadap praktik terbaik memastikan desain tetap berfungsi sepanjang masa hidupnya. Seiring kemajuan teknologi dan peningkatan kecepatan, pentingnya analisis waktu yang mendetail akan terus meningkat.

Untuk tim yang ingin meningkatkan kualitas desain mereka, menginvestasikan waktu pada diagram waktu yang akurat dan alur verifikasi sangat penting. Ini mengurangi risiko, menurunkan biaya debugging, dan memastikan produk akhir memenuhi spesifikasinya. Dengan alat dan metodologi yang tepat, tantangan waktu menjadi kendala yang dapat dikelola, bukan hambatan.