Waktu adalah dimensi dasar dalam setiap sistem komputasi. Baik Anda sedang membangun platform perdagangan frekuensi tinggi, kontroler tertanam waktu nyata, atau layanan awan terdistribusi, urutan dan durasi kejadian menentukan keberhasilan atau kegagalan. Meskipun banyak yang fokus pada aliran data dan fungsionalitas, aspek temporal sering diabaikan hingga masalah kinerja muncul. Panduan ini mengeksplorasi peran penting diagram waktu dalam desain dan pengujian sistem, memberikan wawasan mendalam tentang bagaimana memvisualisasikan waktu meningkatkan arsitektur dan keandalan. 📊

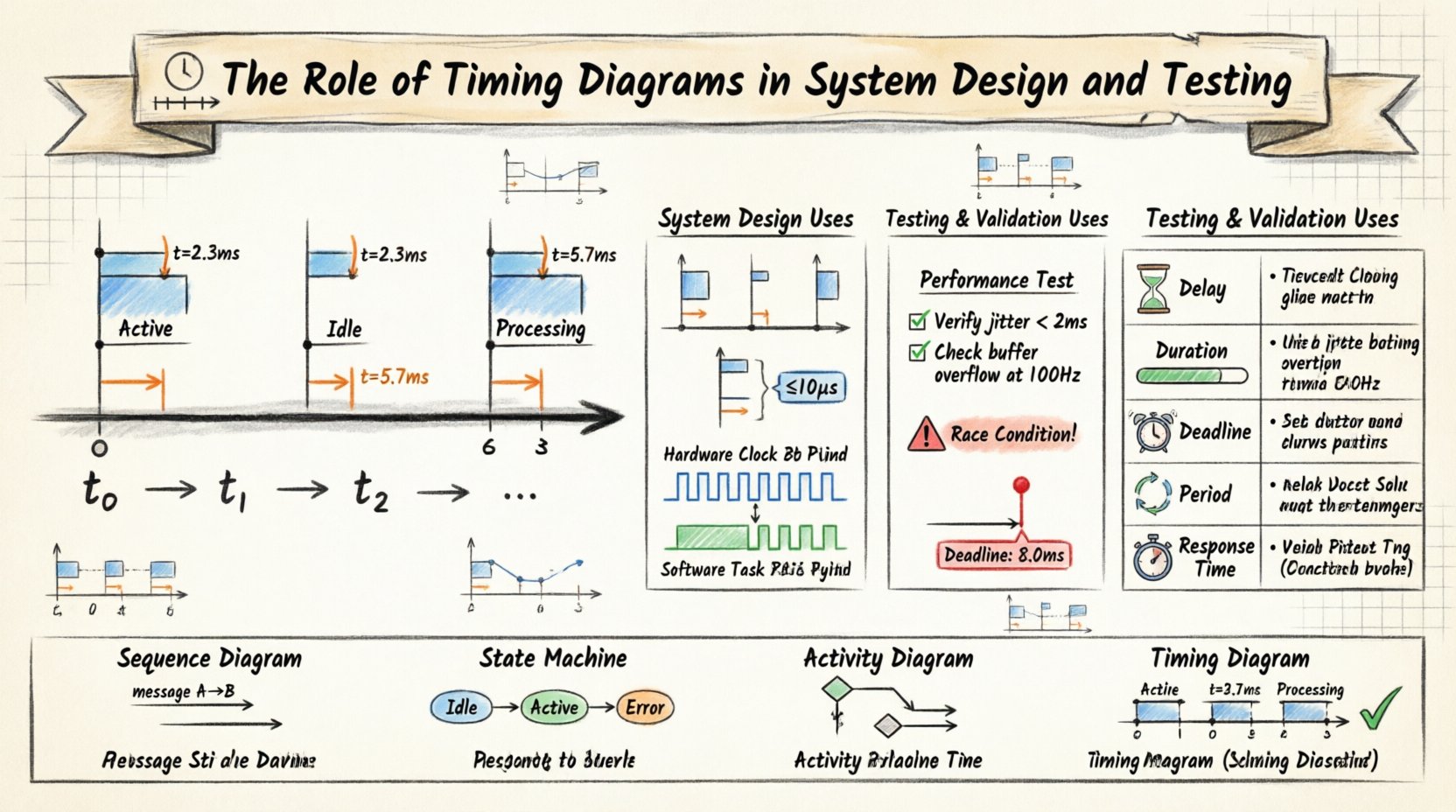

Diagram waktu menawarkan pandangan khusus tentang perilaku sistem. Mereka berfokus pada kapandaripada hanya apa. Dengan memetakan perubahan status dan transisi sinyal terhadap sumbu waktu, arsitek dan penguji dapat mengidentifikasi kondisi persaingan, kemacetan, dan pelanggaran latensi sebelum kode ditulis atau diimplementasikan. Pendekatan ini menggeser jaminan kualitas ke awal, menangkap cacat temporal sedini mungkin dalam siklus pengembangan. ⏱️

🔍 Memahami Konsep Inti Diagram Waktu

Diagram waktu adalah jenis khusus dari diagram interaksi UML (Unified Modeling Language). Diagram ini menekankan urutan waktu pesan dan perubahan status. Berbeda dengan diagram urutan yang berfokus pada urutan pesan antar objek, diagram waktu menekankan durasi kejadian dan momen tepat saat kejadian terjadi. Perbedaan ini sangat penting untuk sistem di mana milidetik menjadi penentu. 🛑

Ciri kunci meliputi:

- Sumbu Waktu:Sumbu horizontal mewakili perjalanan waktu, mengalir dari kiri ke kanan. Ini memungkinkan visualisasi penundaan dan konkurensi.

- Lifeline:Garis vertikal mewakili objek, komponen, atau sinyal. Garis-garis ini tidak hanya menunjukkan eksistensi; mereka menunjukkan status entitas sepanjang waktu.

- Perubahan Status:Diagram ini menunjukkan kapan suatu objek memasuki status tertentu, seperti “Aktif,” “Menganggur,” atau “Sedang Diproses.”

- Transisi Sinyal:Panah menunjukkan pengiriman dan penerimaan sinyal, dilengkapi keterangan waktu atau durasi.

Saat mendesain sistem yang kompleks, memahami elemen-elemen ini mencegah asumsi yang keliru. Misalnya, seorang pengembang mungkin mengasumsikan respons bersifat instan. Diagram waktu memaksa tim untuk menentukan secara tepat berapa lama respons tersebut membutuhkan waktu dan apa yang terjadi jika melebihi batas waktu tersebut. 🧠

⚙️ Diagram Waktu dalam Desain Sistem

Selama tahap desain, diagram waktu berfungsi sebagai gambaran rancangan untuk batasan temporal. Diagram ini menutup celah antara arsitektur abstrak dan rincian implementasi yang konkret. Berikut adalah bagaimana diagram ini memengaruhi keputusan desain.

1. Mengidentifikasi Konkurensi dan Paralelisme

Sistem modern jarang berjalan secara linier. Banyak thread atau proses sering berjalan secara bersamaan. Diagram waktu membuat konkurensi menjadi terlihat.

- Lifeline Paralel:Ketika lifeline tumpang tindih secara horizontal, itu menunjukkan eksekusi paralel. Ini membantu desainer mengidentifikasi kemungkinan kondisi persaingan di mana dua proses mengakses sumber daya yang sama.

- Persaingan Sumber Daya:Dengan memvisualisasikan kapan sumber daya dikunci atau dilepaskan, arsitek dapat mengoptimalkan strategi alokasi.

- Operasi Asinkron:Diagram ini menjelaskan bagaimana callback asinkron berinteraksi dengan periode tunggu sinkron.

2. Menentukan Persyaratan Latensi

Latensi adalah waktu yang dibutuhkan oleh suatu sistem untuk merespons. Diagram waktu memungkinkan tim untuk menetapkan batasan yang jelas.

- Keterlambatan Maksimum:Anda dapat memberi anotasi pada jalur sinyal dengan durasi maksimum yang diizinkan. Jika desain mengimplikasikan keterlambatan yang lebih lama, arsitektur harus berubah.

- Keterlambatan Minimum:Beberapa protokol perangkat keras memerlukan waktu tunggu minimum sebelum sinyal dikirim. Diagram ini menangkap keterbatasan fisik ini.

- Ambang Batas Waktu Habis:Desainer dapat menentukan kapan sistem harus menghentikan suatu operasi jika respons tidak diterima dalam kerangka waktu yang ditentukan.

3. Antarmuka Perangkat Keras-Perangkat Lunak

Dalam sistem tertanam, interaksi antara kode dan perangkat keras bersifat ketat. Diagram waktu sering menjadi satu-satunya cara untuk mendokumentasikan interaksi ini secara akurat.

- Siklus Jam:Desainer dapat memetakan sinyal ke dalam siklus jam, memastikan gerbang logika berfungsi pada saat yang tepat.

- Penanganan Interupsi:Diagram menunjukkan bagaimana interupsi menghentikan pemrosesan normal dan melanjutkannya nanti, dengan mempertimbangkan waktu peralihan konteks.

- Status Daya:Transisi dari mode tidur ke mode aktif membutuhkan waktu. Diagram waktu merencanakan latensi ini untuk mencegah kehilangan data.

🧪 Diagram Waktu dalam Pengujian dan Validasi

Setelah sistem dibangun, pengujian memverifikasi bahwa perilaku temporal sesuai dengan desain. Diagram waktu menjadi standar acuan untuk validasi. 📏

1. Pengujian Kinerja

Uji beban dan uji tekanan sering mengukur throughput, tetapi diagram waktu mengukur presisi. Pengujinya dapat membandingkan log aktual dengan diagram yang dirancang.

- Verifikasi Latensi:Konfirmasikan bahwa waktu antara permintaan dan respons berada dalam rentang yang ditentukan.

- Analisis Throughput:Meskipun throughput adalah laju, diagram waktu membantu memvisualisasikan celah antar transaksi untuk memastikan konsistensi.

- Pengukuran Jitter:Variabilitas dalam waktu disebut jitter. Diagram ini membantu mengidentifikasi apakah jitter berada dalam batas yang dapat diterima untuk aplikasi tersebut.

2. Deteksi Kondisi Persaingan

Kondisi persaingan terjadi ketika hasil tergantung pada urutan kejadian. Diagram waktu mengungkap kerentanan ini.

- Eksekusi yang Tumpang Tindih:Jika dua operasi kritis tumpang tindih dengan cara yang menyebabkan kerusakan data, diagram ini menyoroti risikonya.

- Pelanggaran Urutan:Jika proses yang berada di hilir dimulai sebelum proses yang berada di hulu selesai, diagram ini menunjukkan pelanggaran ini dengan jelas.

- Skenario Kebuntuan:Ketergantungan siklik dengan batasan waktu dapat menyebabkan kebuntuan. Memvisualisasikan waktu tunggu membantu mencegah hal ini.

3. Validasi Sistem Real-Time

Untuk sistem real-time, melewatkan batas waktu merupakan kegagalan. Diagram waktu sangat penting untuk kepatuhan.

- Batas Waktu Keras:Kejadian harus terjadi pada waktu tertentu. Diagram ini menentukan batas yang ketat.

- Batas Waktu Lunak:Kejadian seharusnya terjadi pada waktu tertentu, tetapi kegagalan yang sesekali diperbolehkan. Diagram ini membantu mengukur toleransi ini.

- Periodisitas:Pada sistem periodik, diagram memastikan kejadian berulang pada interval teratur tanpa geseran waktu.

📏 Komponen Utama dan Notasi

Untuk menggunakan diagram waktu secara efektif, seseorang harus memahami notasi standar. Kejelasan dalam notasi mencegah salah tafsir selama tinjauan kode dan pengujian. 📝

1. Garis Kehidupan

- Garis vertikal yang mewakili peserta.

- Dapat mewakili instans kelas, thread, atau pin perangkat keras.

2. Batang Status

- Blok persegi panjang pada garis kehidupan yang menunjukkan status saat ini dari objek.

- Transisi terjadi ketika batang status berubah.

3. Pesan

- Panah horizontal yang menunjukkan sinyal.

- Dapat bersifat sinkron (menghambat) atau asinkron (tidak menghambat).

- Sering dilengkapi dengan waktu atau durasi.

4. Kendala Waktu

- Anotasi yang menentukan batasan waktu.

- Dapat menentukan nilai pasti atau rentang.

⏱️ Penjelasan Kendala Waktu

Kendala waktu adalah nilai inti dari diagram ini. Mereka menentukan aturan berinteraksi terhadap waktu. Di bawah ini adalah tabel yang menjelaskan jenis-jenis kendala umum yang digunakan dalam pemodelan sistem. 📊

| Jenis Kendala | Deskripsi | Skenario Contoh |

|---|---|---|

| Kendala Penundaan | Menentukan waktu minimum atau maksimum antara dua kejadian. | Sebuah sensor harus menunggu 10ms sebelum mengirim data untuk menghindari gangguan. |

| Kendala Durasi | Menentukan berapa lama suatu keadaan harus dipertahankan. | Tekanan tombol harus dipegang selama 2 detik untuk diaktifkan. |

| Kendala Batas Waktu | Menunjukkan waktu absolut saat suatu kejadian harus selesai. | Sinyal pengereman harus mencapai kontroler dalam waktu 50ms. |

| Kendala Periode | Menentukan interval antara kejadian yang berulang. | Sinyal heartbeat dikirim setiap 1 detik. |

| Kendala Waktu Tanggap | Waktu yang berlalu antara pemicu dan reaksi. | Sistem harus merespons login pengguna dalam waktu 200ms. |

Menggunakan kendala-kendala ini secara eksplisit menghilangkan ambiguitas. Ini memungkinkan tim pengujian untuk menulis tes otomatis yang menegaskan batas waktu khusus ini. 🤖

🛑 Kesalahan Umum dan Solusinya

Bahkan dengan alat yang kuat, kesalahan tetap terjadi. Mengenali kesalahan umum memastikan diagram tetap menjadi aset yang bermanfaat, bukan sekadar kekacauan dokumentasi. 🧐

- Terlalu Kompleks: Mencoba memodelkan setiap milidetik dapat membuat diagram tidak dapat dibaca. Fokus pada jalur kritis dan interaksi yang sensitif terhadap waktu.

- Kurangnya Konteks: Diagram waktu tanpa konteks menjadi membingungkan. Selalu beri label pada garis hidup dan tentukan satuan waktu (misalnya, ms, μs, siklus jam).

- Mengabaikan Variabilitas Jaringan: Pada sistem terdistribusi, latensi jaringan tidak konstan. Diagram desain harus mempertimbangkan skenario jitter dan kehilangan paket.

- Statis vs. Dinamis: Diagram waktu sering merupakan representasi statis dari perilaku dinamis. Pastikan tim memahami bahwa perilaku runtime sebenarnya dapat berbeda karena pengumpulan sampah atau penjadwalan OS.

- Diagram yang Ketinggalan Zaman: Perubahan kode sering kali membuat diagram menjadi tidak valid. Tangani mereka sebagai dokumen hidup yang memerlukan pembaruan bersamaan dengan kode sumber.

🔄 Perbandingan dengan Teknik Pemodelan Lainnya

Diagram waktu bukan pengganti diagram lainnya; mereka adalah pelengkap. Memahami kapan menggunakan alat mana yang tepat merupakan kunci dalam pemodelan sistem yang efektif. 🧩

| Jenis Diagram | Fokus Utama | Paling Cocok Digunakan Untuk |

|---|---|---|

| Diagram Urutan | Urutan pesan | Alur interaksi tingkat tinggi, langkah-langkah logis. |

| Diagram Mesin Status | Transisi status | Alur logika, manajemen status internal. |

| Diagram Aktivitas | Logika alur kerja | Proses bisnis, alur algoritma. |

| Diagram Waktu | Waktu dan durasi | Kendala waktu nyata, latensi, konkurensi. |

Sebagai contoh, diagram urutan mungkin menunjukkan bahwa “Layanan A memanggil Layanan B.” Diagram waktu menambahkan detail: “Layanan A memanggil Layanan B, dan Layanan B harus merespons dalam waktu 100ms, atau Layanan A akan timeout.” Menggabungkan pandangan ini memberikan gambaran lengkap mengenai perilaku sistem. 🌐

🚀 Langkah-Langkah Implementasi Strategis

Mengintegrasikan diagram waktu ke dalam alur kerja Anda memerlukan pendekatan yang terstruktur. Berikut adalah proses yang direkomendasikan untuk menerapkan metodologi ini secara efektif. 🛠️

- Identifikasi Jalur Kritis: Tentukan interaksi mana yang memiliki persyaratan waktu yang ketat. Tidak setiap pemanggilan API memerlukan diagram waktu.

- Tentukan Satuan Waktu: Sepakati satuan pengukuran standar di seluruh tim (milidetik, mikrodetik, atau siklus jam).

- Berkolaborasi pada Kendala: Libatkan arsitek dan penguji saat menentukan kendala waktu. Arsitek menentukan target; penguji menentukan kemampuan pengukuran.

- Validasi dengan Log: Pastikan pencatatan log saat runtime menangkap cukup detail untuk merekonstruksi diagram waktu guna verifikasi.

- Iterasi: Seiring sistem berkembang, tinjau kembali diagram-diagram tersebut. Perbarui mereka untuk mencerminkan karakteristik latensi baru atau perubahan arsitektur.

Proses ini memastikan bahwa diagram waktu tetap relevan dan dapat diandalkan sepanjang siklus hidup proyek. Ini mengubahnya dari dokumentasi statis menjadi aset pengujian dinamis. 📈

🔗 Terintegrasi dengan Pipeline CI/CD

Pengembangan modern bergantung pada otomatisasi. Diagram waktu dapat diintegrasikan ke dalam pipeline Integrasi Berkelanjutan dan Deploi Berkelanjutan (CI/CD) untuk menerapkan gate kualitas. 🔄

- Pemeriksaan Otomatis:Skrip dapat menganalisis log dan memverifikasi bahwa batasan waktu yang ditentukan dalam diagram terpenuhi selama pengujian otomatis.

- Gate Kinerja:Jika suatu build melampaui ambang batas waktu yang ditentukan dalam diagram, penyebaran dapat diblokir secara otomatis.

- Pengujian Regresi:Perubahan yang secara tidak sengaja meningkatkan latensi dapat segera terdeteksi jika diagram waktu berfungsi sebagai dasar untuk pengujian regresi.

Integrasi ini menggeser validasi waktu dari aktivitas tinjauan manual menjadi mekanisme penegakan otomatis. Ini menjamin bahwa kinerja bukan sekadar pertimbangan akhir, tetapi merupakan persyaratan inti dari setiap rilis. 🏁

Presisi yang ditawarkan oleh diagram waktu sangat diperlukan untuk sistem di mana waktu merupakan sumber daya kritis. Dengan secara eksplisit memodelkan perilaku temporal, tim dapat membangun sistem yang lebih kuat, andal, dan dapat diprediksi. Baik dalam mengelola interupsi perangkat keras maupun mengoordinasikan mikroservis, disiplin analisis waktu memberikan manfaat besar terhadap stabilitas sistem. 🕒