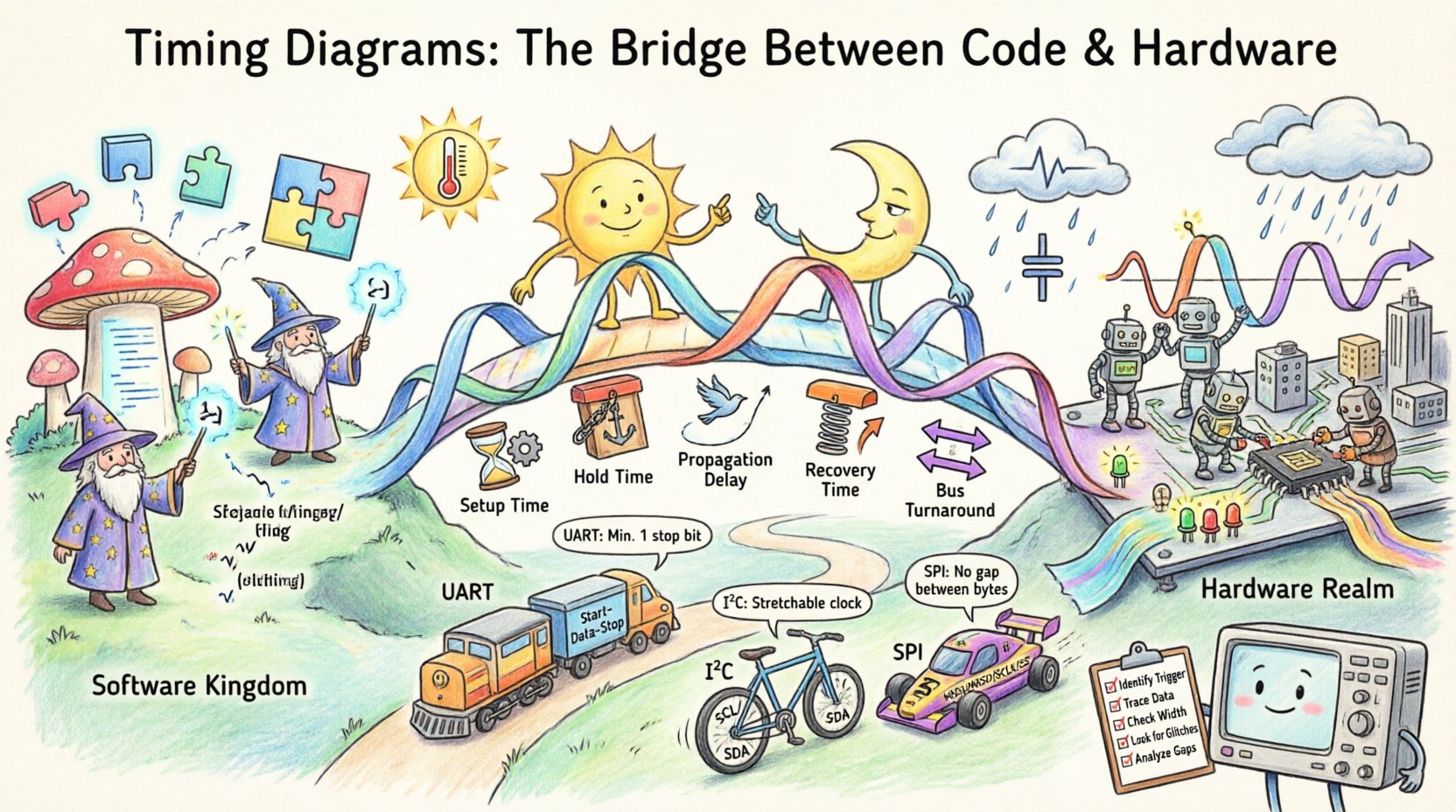

Ketika insinyur perangkat lunak menulis kode, mereka berpikir dalam instruksi, variabel, dan alur logika. Ketika insinyur perangkat keras merancang sirkuit, mereka berpikir dalam tingkat tegangan, keterlambatan propagasi, dan siklus jam. Dua dunia ini sering berada dalam keadaan gesekan. Kode mengharapkan sinyal tiba pada saat logika tertentu, tetapi perangkat keras beroperasi berdasarkan waktu fisik yang rentan terhadap gangguan, suhu, dan resistensi listrik. Jembatan antara kedua domain ini adalah diagram waktu.

Diagram waktu bukan sekadar gambar; ia adalah kontrak. Diagram ini mendefinisikan hubungan tepat antara peristiwa dalam waktu. Ia memberi tahu firmware kapan aman untuk membaca pin dan memberi tahu silikon kapan aman untuk menggerakkan jalur. Tanpa pemahaman yang jelas terhadap diagram ini, sistem tertanam gagal secara tak terduga. Kerusakan data, kondisi persaingan, dan kegagalan sistem menjadi masalah umum. Panduan ini mengeksplorasi mekanisme diagram waktu, fisika di baliknya, serta cara membaca dan membuatnya secara efektif.

📊 Anatomi Suatu Sinyal

Pada intinya, logika digital bergantung pada keadaan biner. Di dunia fisik, namun, keadaan ini diwakili oleh tingkat tegangan. ‘Tinggi’ bisa bernilai 3,3 volt, dan ‘Rendah’ bisa bernilai 0 volt. Namun sinyal tidak berpindah secara instan. Mereka naik dan turun dalam periode tertentu. Diagram waktu menggambarkan transisi ini.

Memahami bahasa visual dari diagram ini adalah langkah pertama menuju penguasaan. Elemen-elemen kunci meliputi:

- Sumbu Waktu:Biasanya horizontal, bergerak dari kiri ke kanan. Dapat berupa linier atau logaritmik, meskipun linier adalah standar untuk sebagian besar analisis logika.

- Garis Sinyal:Garis vertikal yang mewakili kabel tertentu, pin, atau node internal.

- Transisi:Perpindahan dari Rendah ke Tinggi (sisi naik) atau Tinggi ke Rendah (sisi turun). Sisi-sisi ini sering memicu perubahan keadaan dalam logika urutan.

- Tingkat:Keadaan stabil suatu sinyal sebelum atau sesudah transisi.

- Label:Anotasi teks yang menjelaskan makna dari pulsa atau interval tertentu.

Pertimbangkan sinyal jam sederhana. Ia bergetar antara Tinggi dan Rendah. Waktu yang dibutuhkan untuk menyelesaikan satu siklus penuh disebut periode. Invers dari periode adalah frekuensi. Dalam diagram waktu, jam berfungsi sebagai detak jantung sistem. Setiap sinyal lainnya sering disinkronkan terhadap sisi-sisi ini.

🕰️ Domain Jam

Sebagian besar sistem digital beroperasi dalam domain jam. Ini adalah kelompok rangkaian yang berbagi referensi waktu yang sama. Namun, sinyal sering kali melintasi domain yang berbeda. Hal ini menimbulkan kompleksitas. Sinyal yang dihasilkan dalam domain cepat mungkin tiba terlambat bagi domain lambat, atau terlalu awal, menyebabkan pelanggaran hold.

Ketika menganalisis waktu, Anda harus mempertimbangkan:

- Skew Jam:Perbedaan waktu kedatangan sinyal jam pada komponen yang berbeda. Jika jam tiba di pengirim sebelum penerima, margin waktu menyempit.

- Perpindahan Fasa:Pada beberapa sistem, sinyal tidak sejajar dengan sisi jam tetapi terjadi di tengah siklus.

- Jitter:Perubahan dalam waktu suatu sinyal. Jitter bisa acak atau deterministik. Ia mengurangi margin gangguan dan membuat diagram menjadi kurang dapat diprediksi.

Kode yang ditulis untuk berinteraksi dengan perangkat keras mengasumsikan jam yang stabil. Jika jam fisik bergeser karena fluktuasi suhu atau tegangan, diagram waktu tidak lagi sesuai dengan kenyataan. Inilah sebabnya diagram waktu harus mencakup batas toleransi atau skenario terburuk.

⚙️ Parameter Waktu Kritis

Parameter-parameter tertentu mendefinisikan batas integritas sinyal. Nilai-nilai ini sering ditemukan dalam datasheet tetapi paling baik dipahami dalam konteks diagram waktu. Tabel berikut ini menjelaskan parameter-parameter paling kritis yang harus dievaluasi insinyur.

| Parameter | Definisi | Dampak terhadap Sistem |

|---|---|---|

| Waktu Siap | Waktu minimum yang harus dijaga agar data tetap stabilsebelum tepi clock. | Jika dilanggar, flip-flop penerima tidak dapat menangkap nilai yang benar. |

| Waktu Tahan | Waktu minimum yang harus dijaga agar data tetap stabilsetelah tepi clock. | Jika dilanggar, flip-flop dapat memasuki keadaan metastabil. |

| Keterlambatan Propagasi | Waktu yang dibutuhkan sinyal untuk menempuh perjalanan dari input ke output. | Keterlambatan menumpuk melalui gerbang logika, berpotensi melewatkan siklus clock. |

| Waktu Pemulihan | Waktu yang dibutuhkan sinyal kontrol untuk kembali normal setelah kejadian asinkron. | Mempengaruhi seberapa cepat sistem pulih dari reset atau interupsi. |

| Waktu Putar Balik Bus | Waktu yang dibutuhkan untuk mengganti mode bus dari output ke input. | Sangat penting untuk bus dua arah seperti I2C atau 1-Wire. |

Melanggar parameter-parameter ini tidak selalu menyebabkan kegagalan langsung. Terkadang sistem bekerja 99% waktu dan hanya gagal dalam kondisi tertentu. Karena itulah analisis waktu merupakan proses iteratif. Anda harus memverifikasi bahwa diagram tetap benar dalam kondisi tegangan dan suhu paling buruk.

👀 Membaca Gelombang Sinyal

Membaca diagram waktu membutuhkan pendekatan sistematis. Saat mendiagnosis masalah perangkat keras, jangan hanya melihat tingkat sinyal. Perhatikan hubungan antar sinyal.

Ikuti langkah-langkah berikut untuk menganalisis gelombang sinyal:

- Identifikasi Pemicu:Temukan kejadian yang memulai urutan. Biasanya merupakan tepi clock atau interupsi eksternal.

- Lacak Data:Ikuti jalur data relatif terhadap pemicu. Apakah data muncul sebelum atau sesudah tepi clock?

- Periksa Lebar: Ukur durasi pulsa. Apakah sinyal “Tinggi” cukup lama agar dapat diakui oleh logika penerima?

- Cari kejadian Glitch:Pulsa palsu yang terjadi di antara keadaan stabil. Ini dapat disebabkan oleh silang sinyal atau bahaya logika.

- Analisis Jarak Kosong:Perhatikan waktu antara akhir satu transaksi dan awal transaksi berikutnya. Apakah cukup waktu bagi perangkat keras untuk reset?

Seringkali, masalah terletak pada jarak kosong. Jika mikrokontroler selesai menulis data ke perangkat peripheral, mungkin perlu jeda tertentu sebelum mengirim byte berikutnya. Jika diagram menunjukkan byte-byte ini berurutan tanpa jarak kosong, kode kemungkinan terlalu agresif untuk perangkat keras.

🔌 Protokol Umum dan Waktu

Protokol komunikasi yang berbeda memberlakukan batasan waktu yang berbeda. Memahami batasan ini sangat penting untuk menulis firmware yang dapat berkomunikasi secara andal.

| Protokol | Karakteristik Waktu Kunci | Mode Kegagalan Umum |

|---|---|---|

| UART | Bit awal diikuti oleh bit data dan bit berhenti. Bergantung pada baud rate. | Kesalahan bit karena pergeseran jam antara pengirim dan penerima. |

| I2C | Garis SCL dan SDA. Membutuhkan resistor pull-up. SDA harus stabil saat SCL tinggi. | Masalah hold-up bus atau penundaan jam yang menyebabkan waktu habis. |

| SPI | Garis jam dan data terpisah. Dipicu oleh tepi (pengaturan CPOL/CPHA). | Slave merespons terlalu lambat dibandingkan kecepatan jam master. |

| Interupsi GPIO | Sensitivitas tepi. Membutuhkan waktu pemrosesan minimal di ISR. | Interupsi hilang karena eksekusi rutin layanan sebelumnya terlalu lama. |

Sebagai contoh, pada SPI, waktu tepi jam relatif terhadap garis data menentukan apakah data diambil pada tepi naik atau turun. Jika firmware mengasumsikan satu mode dan perangkat keras dikonfigurasi untuk mode lain, data akan dibaca secara salah. Diagram waktu menjelaskan hubungan ini secara visual, mencegah kesalahan konfigurasi.

🔍 Mengevaluasi Masalah dengan Waktu

Ketika suatu sistem berperilaku tidak stabil, alat pertama yang harus digunakan bukan debugger, tetapi diagram waktu. Debugging dengan waktu melibatkan menangkap perilaku listrik aktual dan membandingkannya dengan desain yang diharapkan.

Masalah yang berkaitan dengan waktu umum meliputi:

- Metastabilitas:Ketika suatu sinyal tiba di flip-flop terlalu dekat dengan tepi jam, output menjadi tidak dapat diprediksi. Ia dapat menetap ke Tinggi, Rendah, atau tetap dalam keadaan antara untuk waktu yang tidak pasti.

- Kondisi Balapan: Ketika hasil tergantung pada urutan relatif dari kejadian. Jika dua sinyal berubah secara bersamaan, urutan pemrosesan menjadi penting.

- Integritas Sinyal:Refleksi dan getaran pada jalur panjang dapat menyebabkan transisi palsu. Diagram mungkin menunjukkan osilasi di tempat gelombang persegi yang bersih seharusnya ada.

- Pelanggaran Setup/Waktu Tahan:Data berubah terlalu dekat dengan tepi clock. Ini sering disebabkan oleh kecepatan clock yang terlalu tinggi untuk jalur logika.

Untuk menyelesaikannya, Anda mungkin perlu menambahkan penundaan dalam kode, mengubah frekuensi clock, atau menyesuaikan tata letak perangkat keras. Diagram waktu menyediakan bukti yang diperlukan untuk membuat perubahan ini dengan percaya diri.

📝 Praktik Terbaik untuk Dokumentasi

Membuat diagram waktu untuk dokumentasi sepenting membacanya. Waktu yang didokumentasikan dengan buruk menyebabkan malapetaka pemeliharaan. Insinyur masa depan akan kesulitan memahami mengapa penundaan tertentu ditambahkan ke kode.

Ikuti panduan berikut saat membuat diagram Anda sendiri:

- Gunakan Simbol Standar:Hindari ikon khusus kecuali didefinisikan dalam legenda. Gunakan notasi tepi naik/turun standar.

- Label Semua Hal:Jangan mengasumsikan pembaca tahu apa yang diwakili setiap garis. Labelkan pin, sinyal, dan status dengan jelas.

- Sertakan Konteks:Tampilkan status sinyal kontrol (seperti Chip Select atau Enable) bersamaan dengan jalur data.

- Tentukan Satuan:Selalu menunjukkan skala waktu. Apakah dalam mikrodetik, nanodetik, atau siklus clock?

- Soroti Jalur Kritis:Gunakan garis tebal atau warna berbeda untuk menekankan sinyal yang menentukan stabilitas sistem.

- Kontrol Versi:Perbarui diagram saat perangkat keras atau firmware berubah. Diagram yang usang merupakan risiko.

Dokumentasi tidak boleh hanya menunjukkan jalur ‘yang baik’. Harus juga menunjukkan keadaan kesalahan. Seperti apa tampilan diagram saat terjadi timeout? Seperti apa tampilan diagram saat reset dipicu? Skenario ini sering menjadi tempat tersembunyinya bug paling banyak.

🌡️ Faktor Lingkungan

Diagram waktu sering dibuat dalam kondisi laboratorium ideal. Lingkungan dunia nyata jarang ideal. Suhu, tegangan, dan gangguan elektromagnetik semua memengaruhi propagasi sinyal.

Pertimbangkan faktor-faktor berikut:

- Suhu:Kinerja silikon menurun pada suhu tinggi. Penundaan propagasi meningkat. Sistem yang berfungsi pada 25°C bisa gagal pada 85°C.

- Tegangan:Tegangan catu yang lebih rendah meningkatkan penundaan. Tegangan yang lebih tinggi bisa mengurangi penundaan tetapi meningkatkan konsumsi daya dan panas.

- Kapasitansi Beban: Kabel panjang menambah kapasitansi. Ini memperlambat waktu naik dan turun sinyal, secara efektif memperlebar lebar pulsa tetapi memperlambat transisi.

Desain yang kuat mempertimbangkan variasi ini. Saat membuat diagram waktu untuk produksi, pertimbangkan sudut ‘kasus terburuk’. Ini berarti diagram mewakili transisi sinyal paling lambat dan tepi jam paling cepat yang mungkin terjadi. Jika sistem berfungsi dalam kondisi ini, maka akan berfungsi dalam kebanyakan kondisi.

🛠️ Membuat dan Memvalidasi Diagram

Meskipun menggambar secara manual memungkinkan, rekayasa modern mengandalkan alat otomatis untuk menangkap dan memvalidasi waktu. Namun, prinsip-prinsipnya tetap sama terlepas dari alat yang digunakan. Tujuannya adalah memvisualisasikan aliran waktu.

Saat memvalidasi sebuah diagram:

- Bandingkan dengan Data Lembaran Spesifikasi: Pastikan nilai waktu dalam diagram Anda sesuai dengan spesifikasi pabrikan untuk chip yang digunakan.

- Jalankan Simulasi: Gunakan lingkungan simulasi untuk memodelkan logika sebelum membangun rangkaian fisik.

- Ukur Perangkat Keras Nyata: Tidak ada yang menggantikan pengukuran nyata. Tangkap gelombang sinyal dari papan fisik dan tumpangkan pada diagram desain.

- Periksa Margin: Apakah ada waktu longgar yang cukup antar sinyal? Jika margin nol, setiap variasi akan menyebabkan kegagalan.

Validasi adalah proses yang berkelanjutan. Seiring berkembangnya firmware, kebutuhan waktu bisa berubah. Handler interupsi baru bisa menimbulkan penundaan yang mendorong sinyal melewati batas waktu. Verifikasi berkelanjutan memastikan jembatan antara kode dan perangkat keras tetap kokoh.

🔗 Persilangan Logika dan Fisika

Pada akhirnya, diagram waktu mewakili persilangan antara logika dan fisika. Logika menentukan apa yang seharusnya terjadi; fisika menentukan apa yang benar-benar terjadi. Tugas insinyur adalah menyelaraskan dua realitas ini.

Dengan menguasai interpretasi dan pembuatan diagram ini, Anda mendapatkan kemampuan untuk mendiagnosis kegagalan kompleks yang mungkin terlewat oleh orang lain. Anda berhenti menebak mengapa sistem macet dan mulai melihat secara tepat di mana batasan waktu dilanggar. Tingkat wawasan ini mengubah seorang pengembang menjadi seorang desainer.

Apakah Anda sedang merancang antarmuka sensor sederhana atau bus komunikasi berkecepatan tinggi, diagram waktu adalah referensi utama Anda. Ini memastikan kode yang Anda tulis dieksekusi dalam waktu yang diharapkan perangkat keras. Ini memastikan sinyal yang Anda lihat di layar sesuai dengan tegangan pada pin. Ini adalah bahasa sinkronisasi.

Luangkan waktu untuk memahami diagram ini. Beri mereka perhatian yang sama seriusnya seperti kode itu sendiri. Dalam sistem tertanam, waktu bukan sekadar detail; ia adalah fondasi keandalan. Ketika kode dan perangkat keras berbicara dalam bahasa waktu yang sama, sistem beroperasi dengan presisi dan stabilitas.