Sistem digital bergantung pada sinkronisasi yang tepat agar berfungsi dengan benar. Ketika sinyal tiba pada waktu yang salah, terjadi kegagalan logika, yang mengakibatkan perilaku yang tidak dapat diprediksi. Memahami cara menganalisis dan memperbaiki masalah ini sangat penting bagi siapa saja yang belajar logika digital, teknik komputer, atau elektronika. Panduan ini membahas konsep inti dan langkah-langkah praktis untuk mengidentifikasi dan menyelesaikan masalah waktu yang ditemui dalam rangkaian urutan dan transmisi data.

Memahami Sinyal Jam dan Sudutnya ⏱️

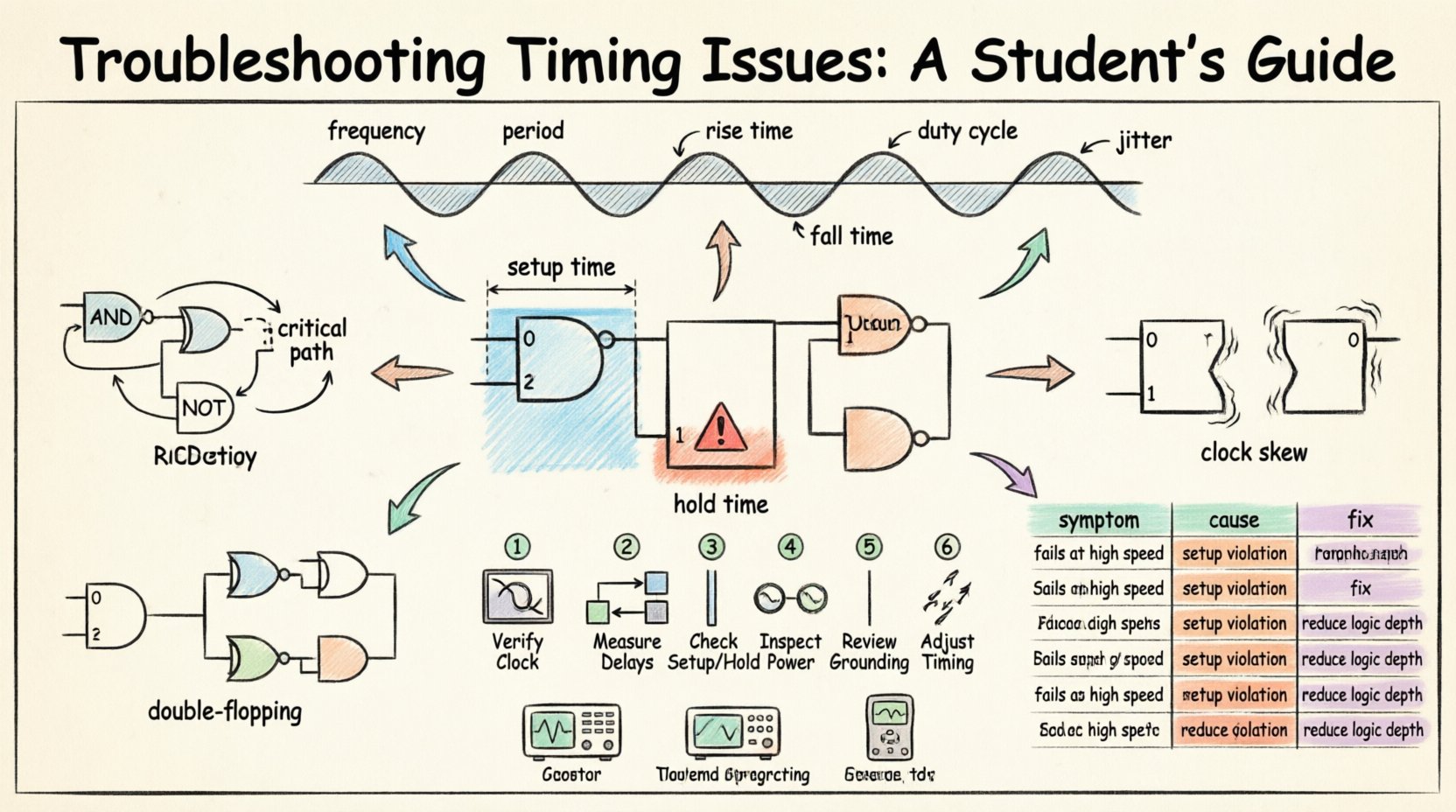

Di inti sebagian besar desain digital terdapat sinyal jam. Gelombang periodik ini menentukan kapan data diambil sampel dan kapan perubahan keadaan terjadi. Pemecahan masalah sering dimulai dengan memverifikasi integritas dari sinyal dasar ini.

- Frekuensi dan Periode: Frekuensi jam menentukan kecepatan operasi. Periode adalah durasi waktu satu siklus penuh. Jika rangkaian membutuhkan jam 100 MHz, periode adalah 10 nanosekon. Setiap penyimpangan di sini memengaruhi semua logika di hilir.

- Waktu Naik dan Turun: Gelombang persegi sempurna bersifat teoretis. Sinyal nyata memiliki waktu naik dan turun yang terbatas. Jika transisi terlalu lambat, sinyal mungkin menghabiskan terlalu banyak waktu di wilayah tegangan yang tidak terdefinisi, menyebabkan banyak perubahan atau kesalahan logika.

- Duty Cycle: Ini adalah rasio waktu sinyal berada pada level tinggi dibandingkan dengan periode total. Duty cycle 50% adalah standar, tetapi beberapa desain membutuhkan siklus yang tidak simetris. Penyimpangan dapat menyebabkan pergeseran margin waktu untuk persyaratan setup atau hold.

Ketika memeriksa suatu rangkaian, gunakan osiloskop atau analis logika untuk melihat bentuk gelombang jam. Perhatikan adanya loncatan kebisingan, getaran, atau jitter yang berlebihan. Jitter mengacu pada penyimpangan tepi jam dari posisi idealnya dalam waktu. Jitter tinggi mengurangi margin waktu efektif yang tersedia agar data dapat stabil.

Pelanggaran Waktu Setup dan Hold ⚠️

Ini adalah pelanggaran waktu yang paling umum ditemui dalam desain logika urutan. Flip-flop dan latch memiliki persyaratan khusus mengenai kapan data harus stabil relatif terhadap tepi jam.

Waktu Setup

Waktu setup adalah jumlah waktu minimum sebelum tepi jam di mana data harus stabil. Jika data berubah terlalu dekat dengan tepi jam, flip-flop mungkin tidak menangkap nilai yang benar.

- Kendala:Waktu propagasi logika kombinasional yang memberi makan flip-flop harus kurang dari periode jam dikurangi waktu setup.

- Gejala:Sistem mungkin berfungsi pada frekuensi yang lebih rendah tetapi gagal saat kecepatan meningkat. Kesalahan bit acak sering terjadi pada output.

- Perbaikan: Kurangi kedalaman logika antar register, tingkatkan periode jam, atau gunakan komponen yang lebih cepat.

Waktu Hold

Waktu hold adalah jumlah waktu minimum setelah tepi jam di mana data harus tetap stabil. Jika data berubah terlalu cepat setelah tepi jam, flip-flop mungkin kehilangan nilai yang telah ditangkap.

- Kendala:Waktu propagasi logika kombinasional harus lebih besar dari waktu hold flip-flop tujuan.

- Gejala:Pelanggaran hold sering terjadi terlepas dari frekuensi. Ini karena penundaan bersifat absolut, bukan relatif terhadap periode.

- Perbaikan: Tambahkan buffer penundaan pada jalur data untuk memperlambat sinyal, atau ubah desain logika untuk mengurangi penundaan.

Sangat penting untuk membedakan keduanya. Pelanggaran setup bergantung pada frekuensi, sedangkan pelanggaran hold bergantung pada jalur. Kesalahan umum adalah mencoba memperbaiki pelanggaran hold dengan memperlambat jam; hal ini tidak akan berhasil dan bahkan dapat memperburuk masalah.

Keterlambatan Propagasi dan Analisis Jalur 📉

Sinyal tidak menempuh perjalanan secara instan. Setiap kabel, gerbang, dan komponen menimbulkan keterlambatan. Menganalisis keterlambatan ini sangat penting untuk memastikan data tiba tepat waktu.

- Keterlambatan Logika Kombinasional: Ini adalah waktu yang dibutuhkan sinyal untuk melewati gerbang seperti AND, OR, dan NOT. Rantai panjang gerbang menimbulkan latensi yang signifikan.

- Keterlambatan Interkoneksi: Pada papan fisik, kabel memiliki kapasitansi dan resistansi. Jalur yang lebih panjang menimbulkan keterlambatan lebih besar. Ini sering dimodelkan sebagai jaringan RC.

- Keterlambatan Pin-ke-Pin: Waktu dari input clock ke output data pada suatu komponen. Ini biasanya ditentukan dalam data lembaran spesifikasi.

Saat melakukan penyelesaian masalah, buat peta jalur kritis. Ini adalah jalur keterlambatan terpanjang antara dua elemen urutan. Jika jalur kritis melebihi periode clock, desain akan gagal. Untuk menemukannya, hitung jumlah keterlambatan untuk semua jalur yang mungkin dan identifikasi nilai maksimumnya.

Skew Clock dan Jitter 📶

Bahkan jika sumber clock sempurna, sinyal mungkin tiba di komponen yang berbeda pada waktu yang berbeda. Fenomena ini dikenal sebagai skew.

- Skew Clock: Ini terjadi ketika sinyal clock menempuh jarak yang berbeda untuk mencapai flip-flop yang berbeda. Skew positif menunda clock penangkap, mengendurkan waktu setup tetapi memperketat waktu hold. Skew negatif memperketat waktu setup tetapi mengendurkan waktu hold.

- Jitter Clock: Variasi jangka pendek dalam waktu tepi clock. Jitter mengurangi anggaran waktu yang tersedia untuk setup data.

- Drift: Perubahan lambat pada frekuensi clock seiring waktu akibat fluktuasi suhu atau catu daya.

Skew sering dikelola melalui sintesis pohon clock pada desain yang kompleks. Pada proyek mahasiswa, biasanya diminimalkan dengan merutekan jalur clock secara merata dan menjaganya tetap pendek. Jika terduga adanya skew, ukur clock secara bersamaan di beberapa titik dalam rangkaian.

Metastabilitas dan Masukan Asinkron 🌀

Ketika data berubah pada saat yang sama dengan tepi clock, flip-flop memasuki keadaan metastabil. Ia tidak segera menetap ke 0 atau 1 tetapi mengambang pada tingkat tegangan antara.

- Risiko:Metastabilitas dapat menyebar melalui sistem, menyebabkan kesalahan logika yang sulit direproduksi.

- Sinyal Asinkron:Masukan dari saklar eksternal atau port komunikasi sering tidak selaras dengan clock internal. Ini harus disinkronkan.

- Double Flopping:Teknik umum untuk menyelesaikan metastabilitas adalah melewatkan sinyal melalui dua flip-flop secara berurutan. Yang pertama menangkap keadaan metastabil, dan yang kedua menyelesaikannya pada siklus berikutnya.

Selalu anggap masukan asinkron sebagai sumber potensial metastabilitas. Jangan menghubungkannya langsung ke logika yang membutuhkan waktu ketat. Gunakan rangkaian sinkronisasi untuk memastikan transfer data yang aman antar domain clock yang berbeda.

Alur Kerja Penyelesaian Masalah Secara Bertahap 🛠️

Ketika terjadi masalah waktu, ikuti pendekatan terstruktur untuk mengidentifikasi penyebabnya. Perubahan acak kemungkinan besar tidak akan memberikan hasil.

- Verifikasi Clock: Periksa frekuensi, siklus kerja, dan amplitudo. Pastikan sinyal stabil dan bersih.

- Ukur Keterlambatan:Gunakan analis logika untuk menangkap gelombang masukan dan keluaran. Ukur keterlambatan propagasi sebenarnya dari jalur tersebut.

- Periksa Setup dan Hold:Hitung apakah jalur memenuhi batasan setup dan hold berdasarkan keterlambatan yang diukur.

- Periksa Daya:Penurunan tegangan dapat memperlambat gerbang. Pastikan catu daya stabil dan menyediakan arus yang cukup.

- Ulasan Grounding:Grounding yang buruk dapat menimbulkan gangguan yang menyerupai kesalahan waktu. Periksa adanya loop ground dan jalur kembali bersama.

- Sesuaikan Waktu: Jika desain fleksibel, sesuaikan frekuensi clock atau tambahkan buffer untuk menyeimbangkan jalur.

Dokumentasi sangat penting dalam proses ini. Catat gelombang dan pengukuran. Data ini membantu dalam membandingkan perilaku yang diharapkan terhadap kinerja aktual.

Tabel Referensi Kesalahan Umum 📊

Gunakan tabel ini sebagai referensi cepat untuk mendiagnosis gejala tertentu.

| Gejala yang Diamati | Penyebab yang Mungkin | Tindakan yang Disarankan |

|---|---|---|

| Sistem gagal pada kecepatan tinggi | Pelanggaran Waktu Setup | Kurangi kedalaman logika atau tingkatkan periode clock |

| Sistem gagal pada kecepatan rendah | Pelanggaran Waktu Hold | Tambahkan buffer penundaan ke jalur data |

| Flip bit acak | Gangguan Sinyal atau Jitter | Periksa pelindung dan stabilitas catu daya |

| Output macet atau restart | Metastabilitas | Terapkan rantai sinkronisasi |

| Perilaku yang tidak konsisten | Kemiringan Jam | Seimbangkan panjang jejak jam |

| Tidak ada output sama sekali | Jam tidak diaktifkan | Periksa distribusi jam dan sinyal aktif |

Alat dan Instrumen 📏

Meskipun alat simulasi berguna, verifikasi fisik sering kali membutuhkan perangkat keras tertentu. Memahami cara menggunakan alat ini dengan benar merupakan bagian dari keterampilan penyelesaian masalah.

- Osiloskop:Sangat penting untuk melihat tingkat tegangan dan bentuk sinyal. Gunakan probe impedansi tinggi untuk menghindari membebani rangkaian.

- Analyzer Logika:Lebih baik untuk sinyal digital. Alat ini menangkap keadaan logika (0 atau 1) seiring waktu. Dapat diatur untuk memicu pada pola tertentu agar mengisolasi kesalahan.

- Penghitung Frekuensi:Digunakan untuk memverifikasi frekuensi tepat dari sumber jam jika osiloskop tidak tersedia.

Pastikan probe dikompensasi dengan benar. Probe yang tidak dikompensasi dapat merusak bentuk sinyal, mengakibatkan kesimpulan yang salah mengenai waktu naik dan keterlambatan.

Pertimbangan Akhir untuk Integritas Sinyal 🔒

Masalah waktu sering kali merupakan gejala dari masalah integritas sinyal yang lebih luas. Semakin cepat sirkuit, semakin penting sifat fisik papan.

- Interferensi Silang:Sinyal pada kabel yang berdekatan dapat saling mengganggu. Pisahkan jalur berkecepatan tinggi dari jalur yang sensitif.

- Penyesuaian Impedansi: Jika impedansi jejak tidak sesuai dengan penggerak atau penerima, terjadi pantulan. Pantulan ini dapat tampak seperti keterlambatan waktu.

- Efek Termal: Saat komponen memanas, karakteristik listriknya berubah. Ini dapat mengubah keterlambatan propagasi dan menyebabkan kegagalan waktu saat beban.

Merancang untuk waktu membutuhkan pandangan menyeluruh. Bukan hanya tentang gerbang logika; tetapi tentang media fisik yang dilalui sinyal. Dengan mengikuti prinsip-prinsip ini, siswa dapat membangun sistem yang kuat yang berfungsi secara andal dalam berbagai kondisi.

Latihan rutin dengan perangkat keras nyata membantu memahami konsep-konsep ini secara mendalam. Teori memberikan kerangka, tetapi debugging langsung membangun intuisi yang dibutuhkan untuk menyelesaikan masalah waktu yang kompleks secara efisien.