Diagramas de tempo são a base da verificação de sistemas digitais. Eles traduzem lógica abstrata em linhas do tempo visuais que engenheiros, designers e testadores dependem para validar o comportamento de sinais. Quando um diagrama de tempo contém erros, as consequências vão muito além da mesa de desenho. Suposições incorretas de tempo podem levar a falhas de hardware, corrupção de dados ou instabilidade do sistema em ambientes de produção. Este guia explora os erros mais frequentes encontrados na análise de tempo e fornece estratégias concretas para garantir precisão.

Criar um diagrama de tempo preciso exige mais do que simplesmente desenhar linhas. Exige um entendimento profundo de domínios de clock, propagação de sinais e restrições físicas. Engenheiros frequentemente correm pela fase de visualização, ignorando detalhes sutis que se tornam críticos durante a implementação. Ao reconhecer esses erros comuns cedo, as equipes podem economizar tempo significativo durante as fases de depuração e integração. Vamos examinar as áreas específicas onde erros ocorrem com frequência.

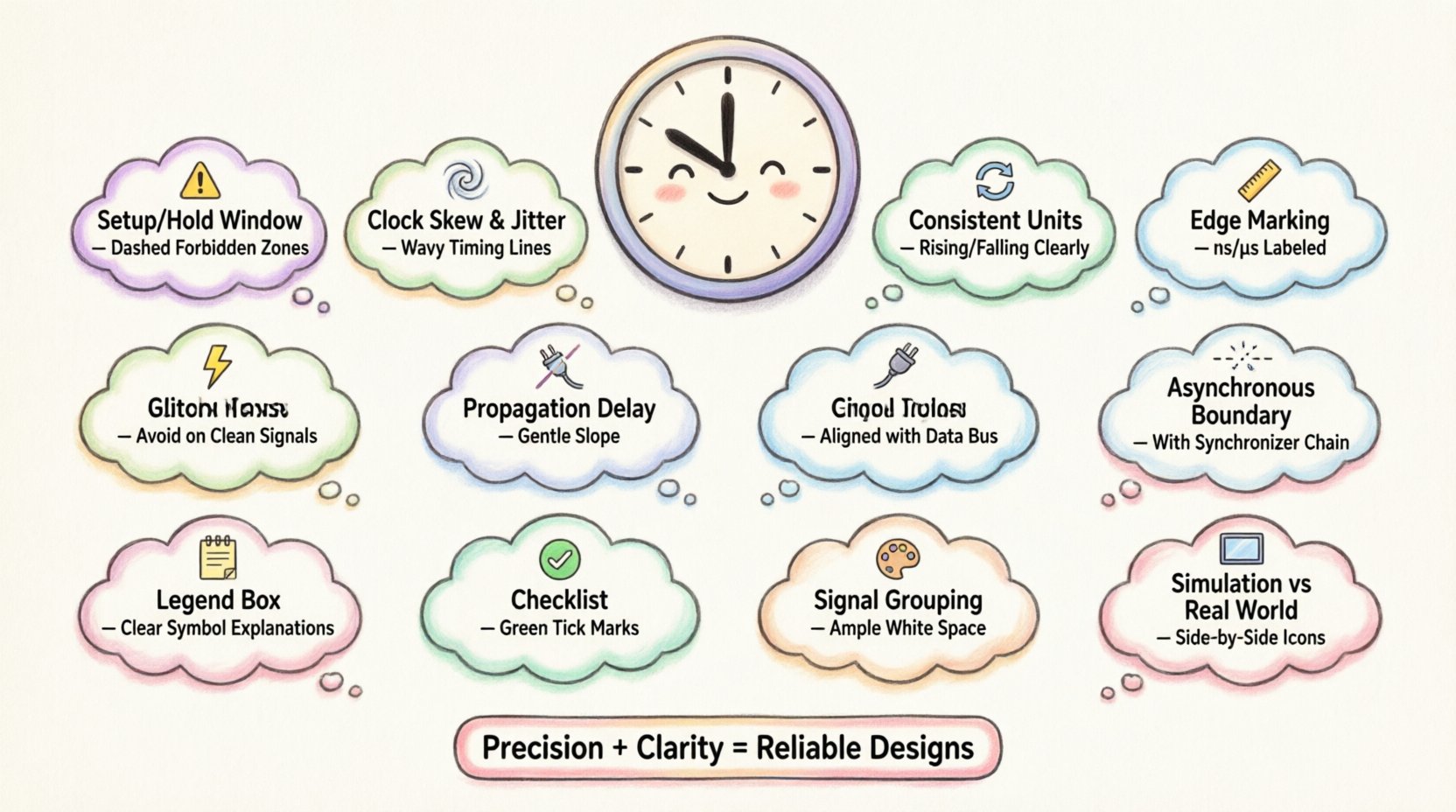

1. Malinterpretando as Violações de Tempo de Setup e Hold ⚠️

Os tempos de setup e hold são restrições fundamentais no design digital síncrono. Uma violação de setup ocorre quando os dados chegam muito tarde antes do borda ativa do clock. Uma violação de hold acontece quando os dados mudam muito cedo após a borda do clock. Esses não são apenas conceitos teóricos; representam limites físicos de flip-flops e portas lógicas.

Muitos diagramas falham em indicar claramente a janela de validade para os sinais de dados. Ao desenhar esses sinais, engenheiros às vezes omitem as janelas crítica de setup e hold, levando à ambiguidade durante a revisão. Um diagrama robusto deve marcar explicitamente essas janelas em relação à borda do clock.

- Erro Comum: Desenhando transições de dados alinhadas exatamente com a borda do clock, sem considerar jitter ou skew.

- Erro Comum: Ignorando a direção da borda (subida vs. descida) para as janelas de setup/hold.

- Erro Comum: Supondo bordas de clock ideais com tempo de transição zero.

Para evitar esses problemas, sempre anote as margens de setup e hold. Use sombreamento ou marcadores distintos para mostrar as zonas proibidas onde as transições de dados são inválidas. Esse indicador visual obriga os revisores a verificar se o caminho do sinal está em conformidade com os requisitos de tempo da lógica receptora.

2. Ignorando o Skew e o Jitter do Clock 🌪️

O skew do clock refere-se à diferença nos tempos de chegada do sinal de clock em diferentes componentes. O jitter representa as variações de curto prazo no tempo do sinal de clock. Ambos os fatores podem alterar drasticamente as janelas de tempo efetivas para os sinais de dados.

Um erro comum em diagramas é tratar o clock como uma linha vertical perfeita em todos os componentes. Na realidade, as redes de distribuição introduzem atrasos. Se um diagrama mostra uma única linha de clock ramificando-se para três registradores diferentes sem levar em conta as diferenças de caminho, ele apresenta uma visão irreais do comportamento do sistema.

- Impacto: O skew pode reduzir o tempo disponível para a propagação dos dados, causando violações de setup falsas.

- Impacto: O jitter pode reduzir a margem de tempo de hold, aumentando o risco de metastabilidade.

Ao criar diagramas, represente os caminhos do clock como linhas separadas com deslocamentos relativos se o skew for significativo. Se o skew for desprezível, declare essa suposição claramente nas anotações do diagrama. Não esconda a complexidade da distribuição do clock se ela afetar o orçamento de tempo.

3. Escalas e Unidades de Tempo Inconsistentes 📏

Um dos erros mais simples, mas mais prejudiciais, é misturar escalas de tempo em um único diagrama. Uma seção pode mostrar nanossegundos enquanto outra mostra microssegundos. Essa inconsistência força o leitor a recalcula constantemente as razões, aumentando a chance de má interpretação.

Outro problema é a ausência de um eixo de tempo claro. Sem uma barra de escala ou marcações rotuladas, a duração dos pulsos torna-se subjetiva. Um pulso curto pode ser de 10 nanossegundos ou 100 nanossegundos, dependendo de como o leitor interpreta o espaçamento.

Siga estas normas para manter a consistência:

- Defina a Escala: Coloque uma régua de tempo na parte inferior ou superior do diagrama.

- Use Notação Científica: Rotule claramente as unidades (ns, μs, ps) no cabeçalho.

- Mantenha as Proporções Proporcionais: Garanta que a distância horizontal entre os eventos corresponda à diferença de tempo.

A consistência constrói confiança. Quando cada engenheiro olha para o diagrama, deve obter os mesmos valores de tempo sem precisar fazer suposições sobre a escala do desenho.

4. Ambiguidade nos Gatilhos de Borda 🔄

A lógica digital muitas vezes depende de gatilhos específicos de borda, como borda de subida ou borda de descida. Um diagrama de tempo deve mostrar explicitamente qual borda dispara a ação. A ambiguidade aqui pode levar a um comportamento completamente oposto no hardware.

Um erro comum é desenhar um sinal de clock sem indicar a borda ativa. Por exemplo, se um flip-flop dispara na borda de descida, mas o diagrama se parece idêntico ao de um disparo na borda de subida, o projetista de lógica pode implementar o comportamento incorreto.

- Melhor Prática:Use setas na linha do clock para indicar a borda ativa.

- Melhor Prática:Rotule o tipo de gatilho na legenda (por exemplo, “Posedge”, “Nedge”).

- Melhor Prática:Evite usar setas duplas, a menos que ambas as bordas sejam ativas.

Clareza é primordial. Se um sinal for assíncrono, certifique-se de que ele esteja claramente separado do domínio do clock para evitar confusão sobre qual borda o controla.

5. Ignorar os Atrasos de Propagação ⏳

O atraso de propagação é o tempo que leva para um sinal viajar da entrada para a saída através de uma porta lógica ou fio. Em diagramas ideais, os sinais parecem mudar instantaneamente. Em sistemas físicos, sempre há um atraso.

Quando os projetistas omitem os atrasos de propagação, o diagrama de tempo sugere que a saída muda imediatamente após a entrada mudar. Isso pode ocultar violações de tempo que ocorrerão em silício. Por exemplo, um caminho combinacional pode parecer atender ao período do clock no diagrama, mas o atraso real empurra os dados além da próxima borda do clock.

| Recursos | Diagrama Ideal | Implementação no Mundo Real |

|---|---|---|

| Transição do Sinal | Linha Vertical | Linha Inclinada com Atraso |

| Propagação | Instantâneo | Atraso da Porta + Atraso do Fio |

| Margem de Setup | Freqüentemente Não Verificado | Deve Considerar o Pior Caso |

Para mitigar isso, anote o atraso esperado para os caminhos críticos. Se o atraso for significativo em relação ao período do clock, desenhe a transição com uma inclinação ou marque explicitamente o valor do atraso. Essa representação visual ajuda os revisores a identificar gargalos potenciais antes da fabricação.

6. Ignorar os Riscos de Metastabilidade 🌌

A metastabilidade ocorre quando um flip-flop recebe dados perto da borda do clock, fazendo com que ele entre em um estado indefinido por uma duração imprevisível. Diagramas de tempo raramente capturam esse estado explicitamente porque é um modo de falha, e não uma operação normal.

No entanto, ignorar a possibilidade de metastabilidade em interfaces assíncronas é uma falha crítica. Se um diagrama mostra um sinal assíncrono se sincronizando a um clock sem uma cadeia de sincronização, isso implica um risco de perda ou corrupção de dados.

- Identificação: Procure sinais que cruzam domínios de clock sem sincronização adequada.

- Documentação: Observe onde a metastabilidade é um risco conhecido e como é mitigada.

- Visualização: Use linhas tracejadas para indicar fronteiras assíncronas.

Mesmo que o sistema seja projetado para lidar com a metastabilidade, o diagrama deve refletir as etapas de sincronização. Isso garante que a equipe de verificação saiba testar essas condições específicas.

7. Glitchs de Sinal e Riscos ⚡

Glitchs são pulsos transitórios que ocorrem devido a atrasos de propagação desiguais em caminhos paralelos. Eles podem causar acionamento falso de lógica se não forem considerados na análise de tempo.

Um erro comum é desenhar sinais limpos e estáveis onde glitchs são fisicamente inevitáveis. Por exemplo, em um multiplexador que muda entre entradas, a saída pode piscar brevemente antes de estabilizar. Se o diagrama mostrar uma transição suave, a lógica posterior pode não estar projetada para filtrar esses glitchs.

Destaque as zonas potenciais de risco no diagrama. Use anotações para alertar que um sinal específico pode apresentar comportamento transitório durante mudanças de estado. Isso informa a estratégia de teste para incluir cenários de detecção de glitchs.

8. Falta de Contexto para Sinais de Controle 🔌

Sinais de dados são inúteis sem o contexto dos sinais de controle, como enable, reset ou chip select. Um diagrama que se concentra apenas nos trilhos de dados frequentemente ignora as condições necessárias para que esses dados sejam válidos.

Por exemplo, um barramento de dados pode mostrar valores válidos, mas se o sinal “Write Enable” não for mostrado como ativo durante essa janela, os dados são efetivamente ignorados. Por outro lado, se o sinal “Write Enable” estiver ativo mas os dados forem inválidos, o sistema escreverá dados inválidos.

- Incluir Controle: Sempre exiba sinais de controle juntamente com sinais de dados.

- Definir Validade: Use uma bandeira “Válido” ou indicador semelhante para indicar quando os dados são confiáveis.

- Condições de Estado: Marque claramente o estado dos sinais de controle (Ativo Alto vs. Ativo Baixo).

A completude é fundamental. Um diagrama de tempo que carece do contexto dos sinais de controle frequentemente é fonte de confusão durante a depuração. Certifique-se de que a relação entre controle e dados seja visualmente explícita.

9. Má utilização de anotações e legenda 📝

Mesmo um diagrama perfeitamente preciso pode ser mal interpretado se carecer de anotações adequadas. Símbolos, abreviações e legendas devem ser consistentes e explicados.

Erros comuns de anotação incluem:

- Usar rótulos genéricos como “Sinal A” em vez de nomes descritivos.

- Falhar em explicar o significado de estilos específicos de linha (sólido vs. tracejado).

- Omitir a definição do nível ativo (Ativo Alto vs. Ativo Baixo).

Uma seção dedicada à legenda deve fazer parte de todo diagrama de tempo. Ela define cada símbolo, estilo de linha e abreviação usada. Isso reduz a carga cognitiva do leitor e garante que todos interpretem o diagrama da mesma forma.

10. Checklist de Verificação e Revisão ✅

Antes de finalizar um diagrama de temporização, é necessária uma revisão sistemática. Use a seguinte lista de verificação para validar a precisão e a clareza do seu trabalho.

| Item de Verificação | Critérios de Aprovação |

|---|---|

| Escala de Tempo | Unidades consistentes e régua clara fornecidas |

| Aresta do Clock | Aresta ativa claramente marcada para todos os clocks |

| Setup/Hold | Janelas definidas para sinais síncronos |

| Propagação | Atrasos considerados em caminhos críticos |

| Sinais de Controle | Sinais de Enable/Reset mostrados com os dados |

| Legendas | Todos os símbolos e abreviações explicados |

| Cruzamento de Domínios | Pontos de CDC identificados e marcados |

Atualizar regularmente esta lista de verificação garante que nenhum erro comum passe despercebido. Serve como uma barreira de qualidade para a documentação antes de chegar à equipe de engenharia.

11. Clareza Visual e Projeto de Layout 🎨

O layout de um diagrama de temporização afeta a facilidade com que erros são detectados. Diagramas cheios com sinais sobrepostos são propensos a leituras incorretas. A alinhamento vertical de sinais relacionados ajuda o olho a rastrear a relação entre os eventos.

Siga esses princípios de layout:

- Agrupe os Sinais: Mantenha sinais relacionados (como endereço e dados) próximos entre si.

- Alinhe as Arestas: Certifique-se de que as arestas do clock estejam alinhadas verticalmente em todos os canais.

- Espaçamento: Deixe espaço suficiente em branco para evitar sobreposição de sinais.

- Codificação por Cor: Use cores diferentes para diferentes domínios de clock, se disponível (embora preto e branco seja o padrão para impressão).

Um layout limpo reduz o esforço cognitivo necessário para interpretar o diagrama. Isso torna mais fácil identificar anomalias e violações de tempo de primeira vista.

12. Restrições do Mundo Real vs. Simulação 🖥️

Diagramas de tempo derivados exclusivamente da simulação podem não refletir realidades físicas. Ferramentas de simulação frequentemente assumem condições ideais, como capacitância parasita zero e roteamento perfeito.

Ao traduzir resultados de simulação para documentação, os engenheiros devem levar em conta as variações de fabricação. Os cantos de processo, tensão e temperatura (PVT) podem alterar as margens de tempo. Um diagrama que mostra apenas valores nominais pode ser insuficiente para um projeto robusto.

- Pior Caso:Considere o pior canto de processo para análise de tempo.

- Melhor Caso:Considere o melhor canto de processo para análise do tempo de retenção.

- Margem:Adicione margens de segurança ao diagrama para considerar as variações de PVT.

A documentação deve refletir a robustez do projeto, e não apenas os resultados de simulação no melhor cenário. Isso prepara a equipe para cenários de implantação no mundo real.

Pensamentos Finais sobre a Precisão de Tempo 🛡️

Diagramas de tempo são ferramentas de comunicação tanto quanto especificações técnicas. Seu objetivo principal é transmitir claramente a intenção e as restrições para todos os envolvidos. Ao evitar erros comuns, como negligenciar o desvio, ignorar disparos nas bordas ou omitir sinais de controle, os engenheiros garantem que a intenção do projeto seja preservada desde a documentação até o hardware.

A precisão nesses diagramas evita retrabalhos caros e ciclos de depuração. Um diagrama bem estruturado serve como a única fonte de verdade para todo o ciclo de vida do projeto. Invista o tempo necessário para fazer a análise de tempo corretamente, e a implementação subsequente seguirá de forma suave.

Lembre-se de que um diagrama de tempo é um documento vivo. Ele deve ser atualizado sempre que o projeto mudar. Manter a integridade das informações de tempo garante que o sistema permaneça confiável durante toda a sua vida útil. Foque na precisão, clareza e completude para entregar projetos digitais robustos.